本指南提供了有關 AMD Vivado Design Suite 中包含的 32 位和 64 位 MicroBlaze V 軟核處理器的信息。該文檔旨在用作為處理器硬件架構的指南,隨附《RISC-V 指令集手冊》第一卷和第二卷。

MicroBlaze V 與傳統 MicroBlaze 處理器之間完全硬件兼容。

本指南包含以下章節

第 2 章:

MicroBlaze V 架構包含處理器功能特性概述以及有關特定定制功能和高速緩存實現的信息。

第 3 章:

MicroBlaze V 信號接口描述描述了可用于連接處理器的信號接口的類型。

附錄 A:

性能和資源使用情況包含不同配置和器件的最大頻率值和資源使用率值。

附錄 B:

附加資源與法律聲明提供了文檔和其他資源的鏈接。

MicroBlaze V 架構概述

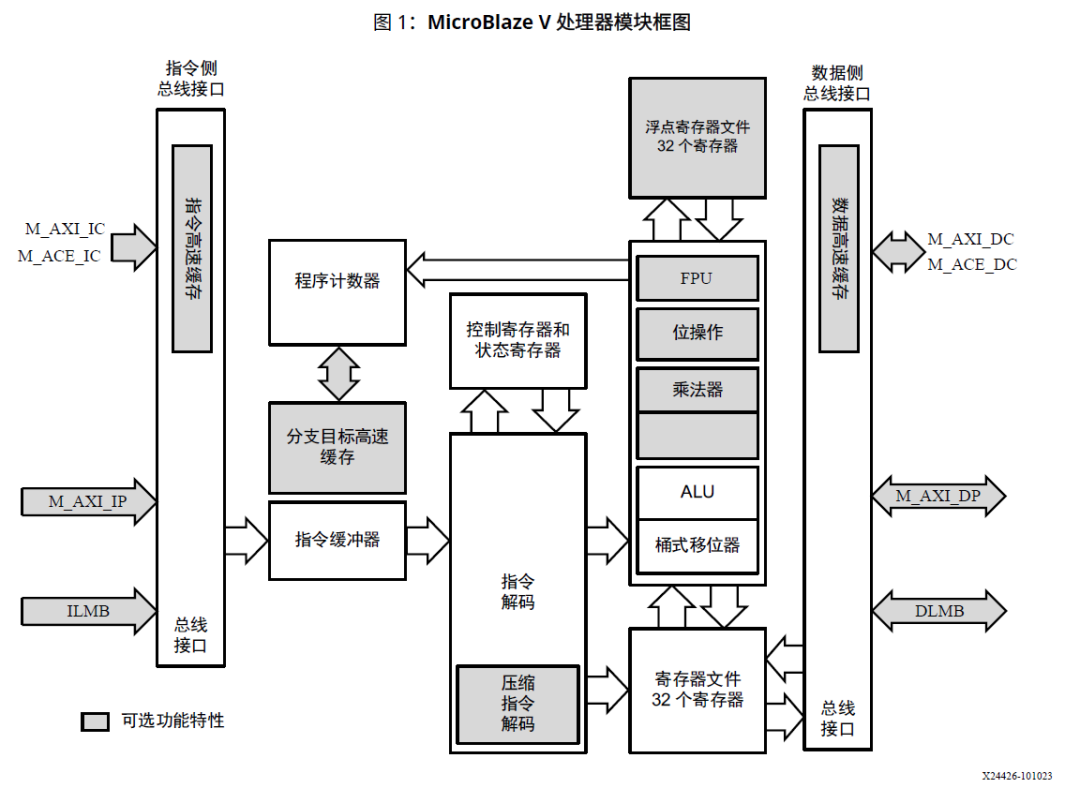

MicroBlaze V 嵌入式處理器軟核是專為在 AMD 現場可編程門陣列中實現而優化的精簡指令集計算機 (RISC)。下圖顯示了該處理器的功能模塊框圖。

功能特性

MicroBlaze V 軟核處理器具有很高的可配置性,您可根據自己的設計需求選擇特定的功能集。

該處理器固定的功能集能實現 RISC-V RV32I 基整數指令集和機器級 ISA。

32 個通用寄存器

可擴展的 32 位程序計數器

單發射流水線

算術邏輯單元 (ALU)

桶式移位器

“Zicsr”控制和狀態寄存器 (CSR) 指令

“Zifencei”指令提取圍欄

除這些固定功能特性外,MicroBlaze V 處理器還會通過參數化設置來允許有選擇地啟用附加功能。

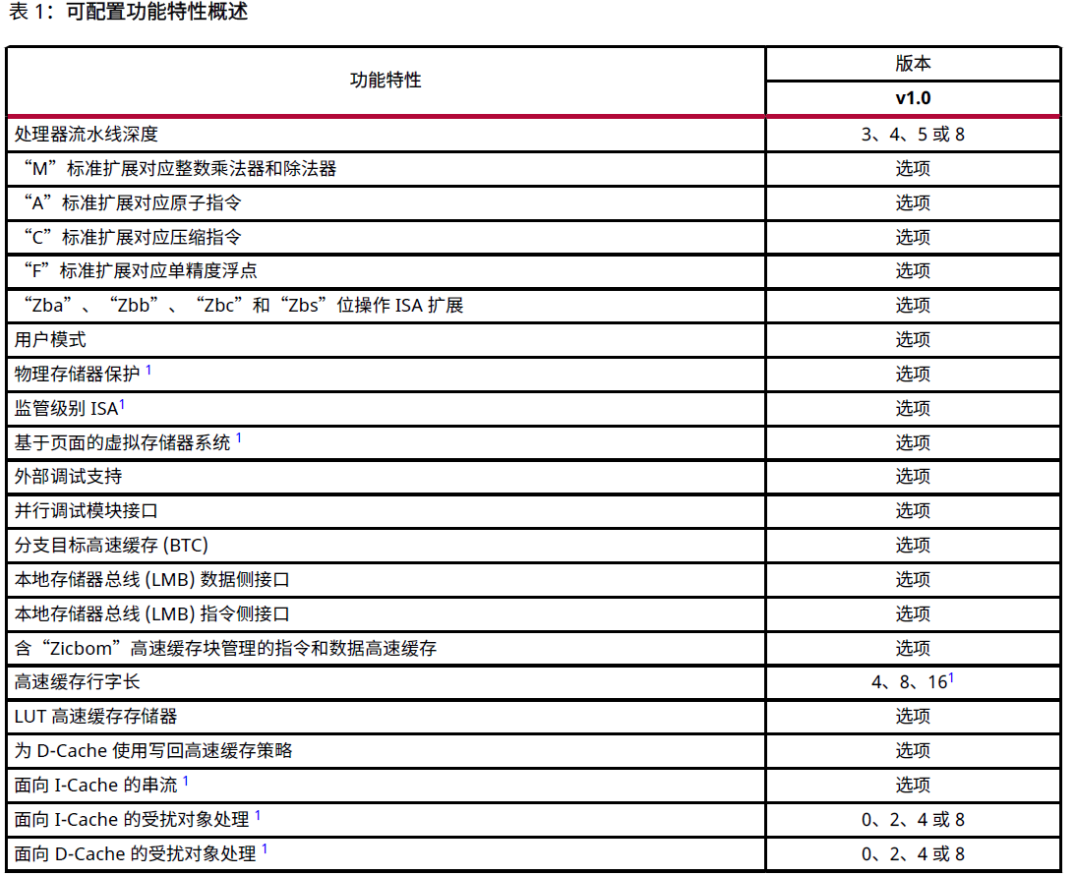

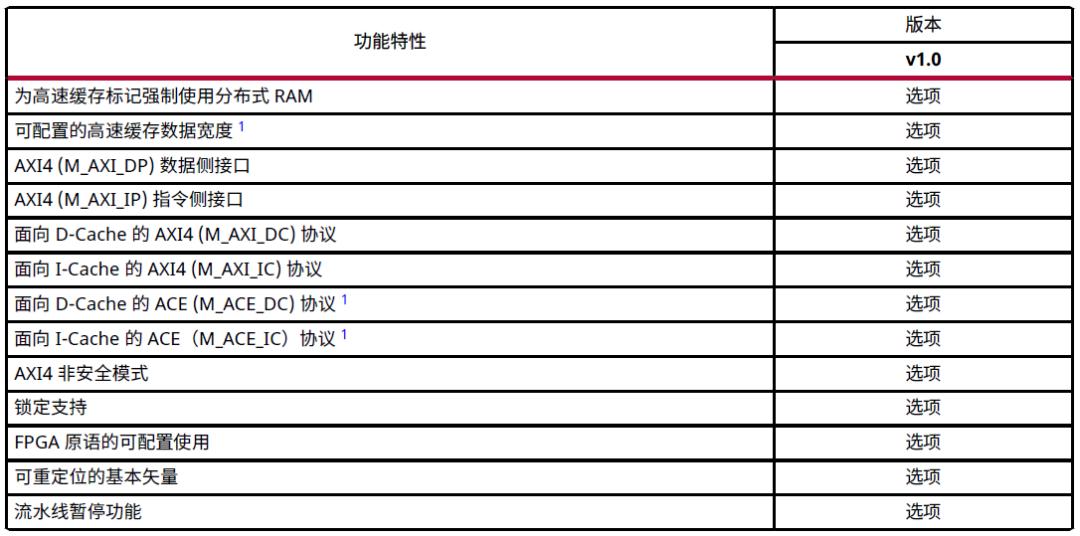

下表提供了可配置的功能特性的概述

術語

下表中簡要解釋了本指南中所使用的 MicroBlaze V 處理器相關的 RISC-V 術語。如需獲取這些術語的完整全面的解釋,請參閱《RISC-V 指令集手冊》。

Custom Instruction(定制指令):可用于供應商專用的非標準擴展的指令集類別。MicroBlaze V 定義了 GET 和PUT 定制指令,以支持 AXI4?Stream 接口,提供與傳統 MicroBlaze 的兼容性。

Exception(異常):在運行時發生的不尋常狀況,此狀況與當前 RISC-V hart 中的指令相關。

Hart:硬件線程。每個 MicroBlaze V 核僅支持一個硬件線程。

Interrupt(中斷):一種外部異步事件,可導致 RISC-V hart 遇到意外的控制傳輸。MicroBlaze V 支持機器外部中斷、不可屏蔽中斷和定制平臺中斷。

Retire(停用):當一條指令執行完成時,就表示停用該指令。在 MicroBlaze V 中,當指令離開 3 階流水線的執行 (EX) 流水線階段,或離開其他所有流水線的寫回 (WB) 流水線階段時,就會停用該指令。

Trap(陷阱):由異常或中斷引發并以陷阱處理程序為目標的控制傳輸。

-

處理器

+關注

關注

68文章

19259瀏覽量

229651 -

amd

+關注

關注

25文章

5466瀏覽量

134087 -

嵌入式

+關注

關注

5082文章

19104瀏覽量

304799 -

MicroBlaze

+關注

關注

3文章

68瀏覽量

21548

原文標題:MicroBlaze V 處理器參考指南

文章出處:【微信號:賽靈思,微信公眾號:Xilinx賽靈思官微】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

軟核處理器助Altera SOPC Builder擴展設計

MicroBlaze處理器的PetaLinux操作系統怎么移植?

microblaze軟核處理器xps和sdk簡單算法創建

求一款雙MicroBlaze軟核處理器的SOPC系統設計

基于MicroBlaze 軟核的FPGA 片上系統設計

基于MicroBlaze軟核的FPGA片上系統設計

基于MicroBlaze軟核的FPGA片上系統設計

基于Xilinx MicroBlaze多核嵌入式系統的設計

MicroBlaze軟核處理器在DAB發射機中的應用

基于雙MicroBlaze軟核處理器的SOPC系統

MicroBlaze軟核處理器簡介

ARTY Board與Xilinx MicroBlaze的配合使用演示

如何使用MicroBlaze軟核進行FPGA片上系統設計

MicroBlaze V軟核處理器的功能特性

MicroBlaze V軟核處理器的功能特性

評論