以下文章來源于ICPMS冷知識,作者gz07apple

過去三十年,碳化硅功率半導體行業取得了長足的進步,但在降低缺陷方面依然面臨著重大挑戰。其主要問題是——碳化硅與柵氧化層之間的界面處存在著大量的缺陷。在NMOS中, 反型層中產生的電子被高密度的界面陷阱等缺陷捕獲,導致溝道內有效載流子數目大幅減少。此外,部分陷阱在俘獲電子之后會變成帶電中心,致使溝道表面的庫侖散射效應加劇,溝道遷移率會進一步下降。

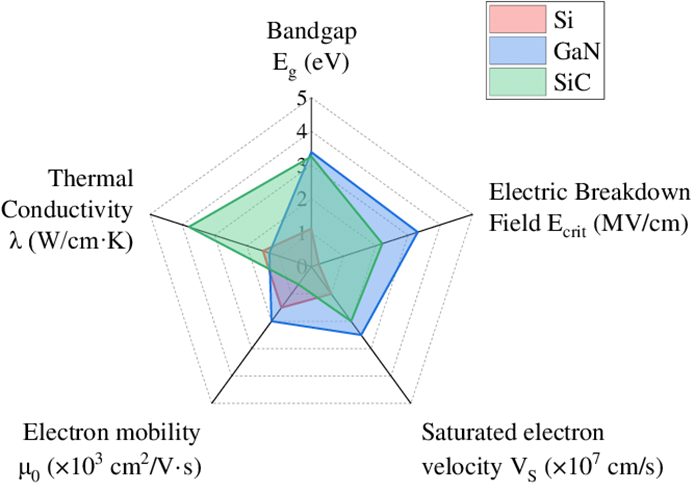

半導體材料的電子遷移率是指,電子在單位電場作用下的平均速度,是衡量電子在被電場拉動(或推動)并穿過半導體材料時速度的量度。電子遷移率越高的半導體材料,電阻率越低,通過相同的電流,損耗越小。由于碳化硅材料的電子遷移率比硅和氮化鎵都要低,若不采取手段實現該技術難點的突破,SiC MOSFET將面臨著因低溝道遷移率導致性能大打折扣的局面。

▲碳化硅材料的電子遷移率不高

為了在晶圓表面形成柵氧化層,器件制造廠商通常會選擇熱氧化處理工藝。對于傳統的硅基MOSFET來說,硅晶圓表面可產出高質量的氧化層。對于碳化硅晶圓,不僅無法通過熱氧化獲得高質量的氧化層,更為嚴重的是,SiC與SiO2之間的界面缺陷比Si與SiO2之間高了100多倍。

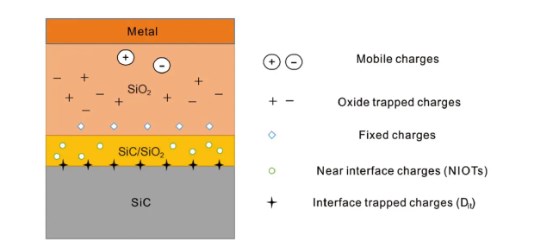

▲碳化硅界面缺陷的主要類型

如上圖所示,根據位置分布,通常將SiC/SiO2界面附近的缺陷分為,界面陷阱(Dit)、近界面氧化物陷阱(NIOTs)、固定電荷、氧化層陷阱及移動電荷。其中界面陷阱主要指位于碳化硅表面的陷阱,主要包括由于熱氧化產生的含碳副產物缺陷、懸掛鍵和晶格失配等形成的陷阱。

界面陷阱主要由金屬雜質、結構缺陷和氧化誘導等因素引起。界面陷阱會影響電子輸運及復合,降低可移動電子濃度,增加界面散射, 導致溝道遷移率下降, 比導通電阻上升。在硅中,氫和氮原子可以有效地消除界面陷阱,但在碳化硅中,氫鈍化效果相對較弱,無法顯著消除界面陷阱。

一、無碳殘留、低缺陷的氧化層

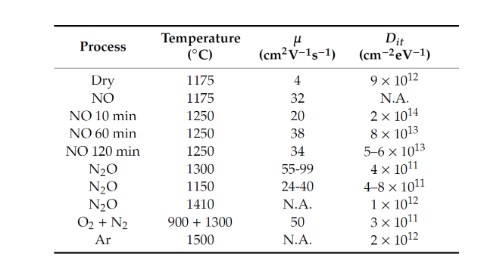

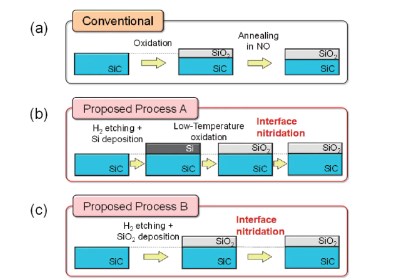

眾所周知,退火工藝可以在一定程度上減少界面缺陷,降低界面陷阱密度,進而提升溝道遷移率。特別是在含氮氛圍中退火,可以有效地將溝道遷移率提升6~12倍。

但由于退火溫度太高(約1300℃),這會導致SiC/SiO2界面出現碳殘留。殘留的碳主要以下面幾種形式存在,如C-Si鍵、碳空位、硅酸鹽和碳化物。鑒于含碳副產物引發的界面缺陷是導致溝道遷移率下降的主要原因,因此業界迫切需要開發一種無碳殘留的柵氧化層制作工藝。

日本京都大學的木本恒暢科研團隊,在2022年提出了一項關于制作高質量柵氧化層的工藝。大致流程如下:首先,通過氫刻蝕去除殘留在碳化硅晶圓表面的缺陷;其次,分兩種方式制作氧化層:一(Process A)是在晶圓表面先沉積一層硅薄膜,然后在750°C低溫下進行氧化,可將其轉換為SiO2薄膜。由于硅氧化的起始溫度為700℃,而碳化硅的氧化起始溫度為900℃,因此750℃僅氧化硅而不會氧化碳化硅。二(Process B)是使用化學氣相沉積(CVD)方式直接沉積SiO2薄膜。

▲高質量氧化層制作工藝流程

最后,引入氮原子以實現界面的高質量化。傳統退火工藝通常使用一氧化氮對界面進行氮化,但碳化硅不可避免地會被一氧化氮中的氧原子氧化,產生新的缺陷。因此,新退火工藝避免使用一氧化氮,而采用在高溫氮氣氛圍中熱處理來提高界面質量。最終的評估結果是,Process A可以將界面缺陷密度降低到傳統工藝的十分之一,而Process B可以將界面缺陷密度降低到傳統工藝的五分之一。

考慮到界面缺陷的大幅降低,以600V或1200V的SiC MOSFET為例,其導通電阻可降低25~35%。換句話說,原來65~75%的芯片尺寸就可以達到相同的額定電流,從而可以將器件成本降低約30%。由于新工藝不采用一氧化氮,相關成本還會進一步下降。因為使用劇毒的一氧化氮不但危險,而且還會增加安裝和維護廢氣處理設備以及檢測警報的成本。

二、優質的垂直晶面成膜

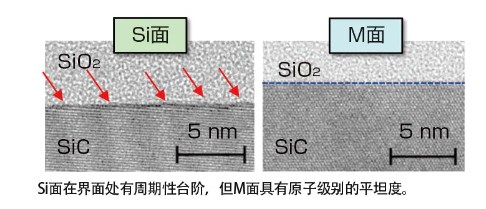

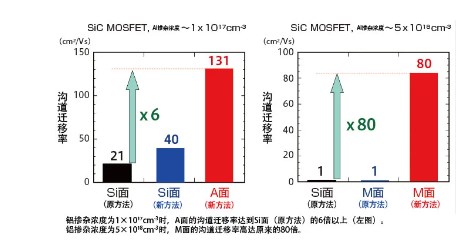

日本京都大學木本教授的科研團隊,不僅提出了關于高質量柵氧化層的制作工藝,而且發現在制造溝槽型MOSFET時,選擇與硅面(0001)垂直的A面或M面上形成柵氧化層,與傳統的硅面成膜的工藝相比,溝道遷移率可以提高約6~7倍。

▲溝槽型MOSFET新的垂直晶面選擇

▲不同晶面成膜后粗糙度對比

此外,通過摻雜較高濃度的鋁形成p阱,并在A面和M面上制造出了溝槽型SiC MOSFET。測量結果表明,相比傳統的平面型(Si面),基于A面和M面的新晶面成膜方法將溝道遷移率分別提高到了6倍和80倍。這樣一來,不僅器件的可靠性大大提高,而且面積大幅減少,使成本可降低到原來的三分之一左右。

▲不同晶面成膜導致溝道遷移率差異

三、眼前一亮的混合外延層

要知道,3C-SiC MOSFET的溝道遷移率為100~370cm2/V·s,而4H-SiC MOSFET通常為20~40cm2/V·s,溝槽型器件為6~90cm2/V·s。上面提到,京都大學可以將溝道遷移率最高做到131cm2/V·s,但仍比3C-SiC MOSFET低三倍左右。

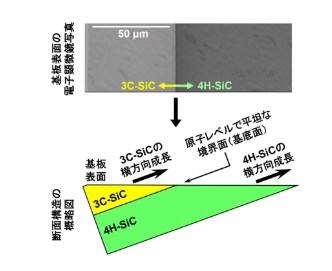

設想如果能夠制造一種混合外延層,既利用3C-SiC材料的高電子遷移率,又利用了4H-SiC材料的高擊穿場強。要實現這一目標,則需要開發一種新的外延生長技術,以無縫堆疊兩種不同晶型的碳化硅層。

2023年9月,日本東北大學的科研團隊發明了一種名為同步橫向外延(Simultaneous Lateral Epitaxy,SLE)生長方法。簡單來說,就是在4H-SiC的延伸基面上生長3C-SiC層,3C-SiC也沿著4H-SiC基面延伸,這樣使得3C-SiC層與4H-SiC層之間的界面非常平坦,完全沒有原子偏差。

▲SLE外延層生長法

使用掃描非線性介電常數電鏡(SNDM)測量的結果表明,3C-SiC表面的缺陷密度僅為4H-SiC的兩百分之一。SLE法大幅降低了界面缺陷密度,預測制作的MOSFET可將損耗降低30%以上。

由于SLE法能夠直接在碳化硅外延層表面引入不同的晶體結構,而無需大幅改變現有的SiC MOSFET器件形狀或制造工藝,預計該方法可以快速導入現有的器件生產線。

總結

本文介紹了三種碳化硅MOSFET溝道遷移率提升工藝,包括通過工藝創新制作無碳殘留、低缺陷氧化層;針對溝槽型器件選擇優質垂直晶面成膜;使用SLE生長法制作含高遷移率的3C-SiC混合外延層。

SiC MOSFET器件目前存在兩個主要技術難點沒有完全突破:低溝道遷移率和高溫、高電場下柵氧化層的可靠性。在克服這兩個問題后,碳化硅功率半導體行業將迎來爆發式增長。

-

MOSFET

+關注

關注

147文章

7229瀏覽量

213945 -

半導體

+關注

關注

334文章

27673瀏覽量

221366 -

晶圓

+關注

關注

52文章

4970瀏覽量

128201 -

SiC

+關注

關注

29文章

2875瀏覽量

62827 -

碳化硅

+關注

關注

25文章

2812瀏覽量

49183

原文標題:【推薦】SiC MOSFET 溝道遷移率提升工藝簡介

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

第三代半導體材料盛行,GaN與SiC如何撬動新型功率器件

溝槽結構SiC-MOSFET與實際產品

SiC-MOSFET有什么優點

SiC功率器件SiC-MOSFET的特點

CGHV96100F2氮化鎵(GaN)高電子遷移率晶體管

半導體工藝幾種工藝制程介紹

SiC-MOSFET器件結構和特征

載流子遷移率測量方法總結

溝槽結構SiC MOSFET幾種常見的類型

載流子輸運現象之散射率、遷移率、電阻率、砷化鎵

8.2.10.3 4H-SiC反型層遷移率的實驗結果∈《碳化硅技術基本原理——生長、表征、器件和應用》

6.3.7 遷移率限制因素∈《碳化硅技術基本原理——生長、表征、器件和應用》

8.2.10.2 反型層遷移率的器件相關定義∈《碳化硅技術基本原理——生長、表征、器件和應用》

SiC MOSFET溝道遷移率提升工藝介紹

SiC MOSFET溝道遷移率提升工藝介紹

評論