第一代半導體材料以傳統的硅(Si)和鍺(Ge)為代表,是集成電路制造的基礎,廣泛應用于低壓、低頻、低功率的晶體管和探測器中,90%以上的半導體產品是用硅基材料制作的; 第二代半導體材料以砷化鎵(GaAs)、磷化銦(InP)和磷化鎵(GaP)為代表, 相對硅基器件具有高頻、高速的光電性能,廣泛應用于光電子和微電子領域; 第三代半導體材料以碳化硅(SiC)、氮化鎵(GaN)、氧化鋅(ZnO)、金剛 石(C)、氮化鋁(AlN)等新興材料為代表。

碳化硅是第三代半導體產業發展的重要基礎材料,碳化硅功率器件以其優異的耐高壓、耐高溫、低損耗等性能,能夠有效滿足電力電子系統的高效率、小型化和輕量化要求。

因其優越的物理性能:高禁帶寬度(對應高擊穿電場和高功率密度)、高電導率、高熱導率,有望成為未來最被廣泛使用的制作半導體芯片的基礎材料。特別是在新能源汽車、光伏發電、軌道交通、智能電網等領域具有明顯優勢。

碳化硅技術壁壘是什么?碳化硅技術壁壘有哪些?

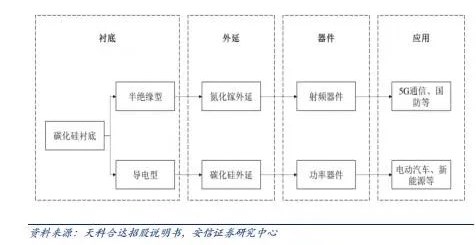

SiC 生產過程分為SiC 單晶生長、外延層生長及器件制造三大步驟,對應的是產業鏈襯底、外延、器件與模組四大環節。

主流制造襯底的方式首先以物理氣相升華法,在高溫真空環境下將粉料升華,通過溫場的控制在籽晶表面生 長出碳化硅晶體。以碳化硅晶片為襯底,使用化學氣相沉積法,在晶片上淀積一層單晶形成外延片。其中,在導電型碳化硅襯底上生長碳化硅外延層,可制成功率器件,主要應用于電動車、光伏等領域;在半絕緣型碳化硅襯底上生長氮化鎵 外延層,可進一步制成射頻器件,應用于 5G 通訊等領域。

就目前而言,碳化硅產業鏈中碳化硅襯底的技術壁壘最高,碳化硅襯底生產難度最高。

SiC的生產瓶頸尚未完全徹底的解決,原料晶柱的質量不穩定存在良率問題,這就導致了SiC器件的成本過高。硅材料長晶平均只要3天即可長成一根晶棒,但碳化硅晶棒則需要一周,一般的硅晶棒可以長200公分的長,但一根碳化硅的晶棒只能長出2公分。而且SiC本身屬于硬脆性材料,由其制成的晶圓,在使用傳統的機械式切割晶圓劃片時,極易產生崩邊,影響產品良率及可靠性。SiC基板與傳統的硅晶錠有很大不同,從設備、工藝、處理到切割的一切都需要進行開發,以處理碳化硅。

碳化硅產業鏈主要分為襯底、外延、器件和應用四大環節,襯底材料是產業鏈的基礎,外延材料是器件制造的關鍵,器件是產業鏈的核心,應用是產業發展的動力。產業上游利用原材料通過物 理氣相升華法等方法制成襯底材料,再利用化學氣相沉積法等方法生長外延材料, 產業中游基于上游材料制成射頻器件、功率器件等器件,最終應用于下游 5G 通信、電動汽車、軌道交通等。其中,襯底和外延共占產業鏈成本 60%,是產業鏈主要價值所在。

SiC襯底:SiC晶體通常用Lely法制造,國際主流產品正從4英寸向6英寸過渡,且已經開發出8英寸導電型襯底產品,國內襯底以4英寸為主。由于現有的6英寸的硅晶圓產線可以升級改造用于生產SiC器件,所以6英寸SiC襯底的高市占率將維持較長時間。

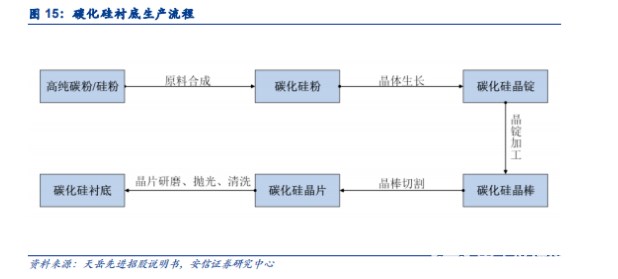

碳化硅襯底工藝復雜,制作難度大。碳化硅襯底是一種由碳和硅兩種元素組成的 化合物半導體單晶材料。目前行業內主要以高純碳粉、 高純硅粉為原料合成碳化 硅粉,在特殊溫場下,采用成熟的物理氣相傳輸法(PVT 法),在晶體生長爐中 生長不同尺寸的碳化硅晶錠,最后經過加工、切割、研磨、拋光、清洗等多道工 序產出碳化硅襯底。

穩定量產性能穩定的高品質碳化硅晶片的技術難點有:

1)由于晶體需要在 2000℃以上的高溫密閉環境生長,對控溫要求極高;

2)由于碳化硅存在 200 多種晶體結構,但只有少數幾種結構的單晶型碳化硅才是 所需的半導體材料,在晶體生長過程中需要精確控制硅碳比、生長溫度梯度、晶 體生長速率以及氣流氣壓等參數;

3)氣相傳輸法下,碳化硅晶體生長的擴徑技術難度極大;

4)碳化硅硬度與金剛石接近,切割、研磨、拋光技術難度大。

SiC外延:通常用化學氣相沉積(CVD)方法制造,根據不同的摻雜類型,分為n型、p型外延片。國內瀚天天成、東莞天域已能提供4寸/6寸SiC外延片。對于SiC外延來說,高壓領域控制難,SiC外延質量對SiC器件影響較大。而且外延設備被行業四大龍頭企業 Axitron、 LPE、TEL 和 Nuflare 所壟斷。

碳化硅外延片,是指在原有碳化硅襯底 上生長了一層有一定要求的、與襯底晶相同的單晶薄膜(外延層)的碳化硅片。外延生長主要使用 CVD(Chemical Vapor Deposition,化學氣相沉積)設備或者 MBE(Molecular Beam Epitaxy,分子束外延)設備。由于碳化硅器件是直接在外延層制造,外延質量的好壞直接影響了器件的性能和良率,隨著器件需求耐壓性能的不斷提高,對應的外延層厚度就越厚,控制難度也就越高。一般電壓在 600V 左右時,所需要的外延層厚度約在 6 微米左右;電壓在 1200-1700V 之間時,所需要的外延層厚度就達到 10-15 微米。如果電壓達到一萬伏以上時,可能就需要 100 微米以上的外延層厚度。而隨著外延層厚度的不斷增加,對厚度和電阻率均勻性以及缺陷密度的控制就變得愈發困難。

SiC器件:國際上600~1700V SiC SBD、MOSFET已經實現產業化,主流產品耐壓水平在1200V以下,封裝形式以TO封裝為主。價格方面,國際上的SiC產品價格是對應Si產品的5~6倍,正以每年10%的速度下降,隨著上游材料器件紛紛擴產上線,未來2~3年后市場供應加大,價格將進一步下降,預計價格達到對應Si產品2~3倍時,由系統成本減少和性能提升帶來的優勢將推動SiC逐步占領Si器件的市場空間。

傳統封裝基于硅基,三代半導體材料具有全新設計。若將傳統硅基封裝結構用于寬禁帶半導體功率器件時,會在頻率、散熱、可靠性等方面帶來新的問題與挑戰。SiC 功率器件對寄生電容和寄生電感更加敏感。相比于 Si 器件 SiC 功率芯片的開 關速度更快,這會對驅動電壓的波形帶來過沖和震蕩,引起開關損耗的增加,嚴重時甚至會引起功率器件的誤開關。此外 SiC 功率器件工作溫度更高,對散熱的 要求也更高。

寬禁帶半導體功率封裝領域研發出多種不同結構。傳統 Si 基功率模塊封裝不再適 用。針對傳統 Si 基功率模塊封裝存在寄生參數過高,散熱效率差的問題,SiC 功 率模塊封裝在結構上采用了無引線互連(wireless interconnection)和雙面散熱 (double-side cooling)技術,同時選用了導熱系數更好的襯底材料,并嘗試在模 塊結構中集成去耦電容、溫度/電流傳感器以及驅動電路等,研發出了多種不同的模塊封裝技術。而且在SiC器件制造存在較高的技術壁壘,生產成本很高。

碳化硅器件是通過 CVD 在碳化硅襯底上疊層外延膜,經過清洗、氧化、光刻、刻蝕、去光阻、離子注入、化學氣相沉積沉淀氮化硅、拋光、濺鍍、后加工等步驟后在 SiC 單晶基板上形成元件結構所得。其中,SiC 功率器件主要包括 SiC 二極管、SiC 晶體管和 SiC 功率模塊。受制于上游材料生產速度慢、良品率低等原因,碳化硅器件具有較高制造成本。

此外,碳化硅器件制造具有一定技術難度:

1)需要開發與碳化硅材料特性吻合的特定工藝,如:SiC 具有高熔點使傳統熱擴散失效,需要采用離子注入摻雜法,并精準控制溫度、升溫速率、持續時間、氣體流量等參數;SiC 對化學溶劑具有惰性,應采用干刻蝕等方法,并優化和開發掩膜材料、氣體混合物、側壁斜率的控制、蝕刻速率、側壁粗糙度等;

2)碳化硅晶片上金屬電極的制造要求接觸電阻低于 10- 5Ω2,符合要求的電極材料 Ni 和 Al 在 100℃ 以上時具有較差熱穩定性,但具有較好熱穩定性的 Al/Ni/W/Au 復合電極材料接觸比電阻高 10- 3Ω2;

3)SiC 切割磨損高,SiC 硬度僅次于金剛石,對切割、研磨、拋光等技術提出了更高的要求。

而且,溝槽型碳化硅功率器件具有更大制造難度。根據器件結構的不同,碳化硅功率器件主要可以分為平面型器件和溝槽型器件。平面型碳化硅功率器件具有較好的單位一致性,制作工藝簡單,但易產生JFET 效應,具有較高的寄生電容和通態電 阻。相較于平面型器件,溝槽型碳化硅功率器件單位一致性較低,具有更復雜的制作工藝,但溝槽結構有利于增加器件單位密度,不易產生 JFET 效應,有利于解 決溝道遷移率低等問題,具有導通電阻小、寄生電容小、開關能耗低等優良性能,具有顯著的成本優勢和性能優勢,已成為碳化硅功率器件發展的主流方向。根據 Rohm 官網,ROHM Gen3 結構(Gen1 Trench 結構)僅為 Gen2(Plannar2)芯片 面積的 75%,且同一芯片尺寸下 ROHM Gen3 結構導通電阻降低 50%。

碳化硅襯底、外延、前段、研發費用和其他分別在碳化硅器 件制造成本中占比 47%,23%,19%,6%,5%。

最后我們再著重分解一下碳化硅產業鏈中襯底的技術壁壘。

碳化硅襯底生產過程與硅基襯底類似,但是難度更大。

碳化硅襯底的制作流程一般包括原料合成、晶體生長、晶錠加工、晶棒切割、晶片研磨、拋光、清洗等環節。

其中晶體生長階段為整個流程的核心,該步驟決定了碳化硅襯底的電學性質。

碳化硅材料在一般條件下很難液相生長,如今市場流行的氣相生長法,生長溫度在 2300℃以上,而且需要精確調控生長溫度,整個操作過程幾乎難以觀測,稍有差錯就會導致產品報廢。相比之下,硅材料只需要 1600℃,要求低很多。制備碳化硅襯底還面臨長晶速度慢,晶型要求高等困難。碳化硅晶圓生長約需要 7 至 10 天,而硅棒拉晶只需要 2 天半。而且碳化硅是硬度僅次于金剛石的材料,切割、研磨、拋光時候也會損失掉的很多,產出比只有 60%。

我們知道碳化硅襯底的尺寸做大是趨勢,隨著尺寸不斷增大,擴徑技術的要求也越來越高。需要綜合多方面的技術控制要素,才能實現晶體的迭代擴徑生長。

轉載:半導體材料與工藝

-

集成電路

+關注

關注

5387文章

11530瀏覽量

361643 -

半導體

+關注

關注

334文章

27290瀏覽量

218090 -

SiC

+關注

關注

29文章

2804瀏覽量

62608 -

碳化硅

+關注

關注

25文章

2748瀏覽量

49019

原文標題:碳化硅技術壁壘有哪些?

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

碳化硅生產難點是什么

碳化硅生產難點是什么

評論