一般運放的datasheet中會列出眾多的運放參數,有些易于理解,我們常關注,有些可能會被忽略了。在接下來的一些主題里,將對每一個參數進行詳細的說明和分析。力求在原理和對應用的影響上把運放參數闡述清楚。由于本人的水平有限,寫的博文中難免有些疏漏,希望大家批評指正。

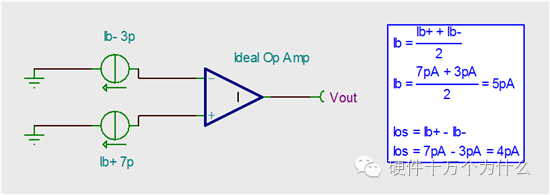

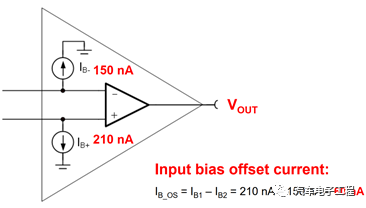

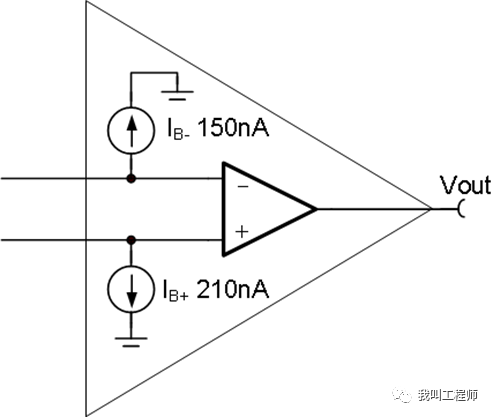

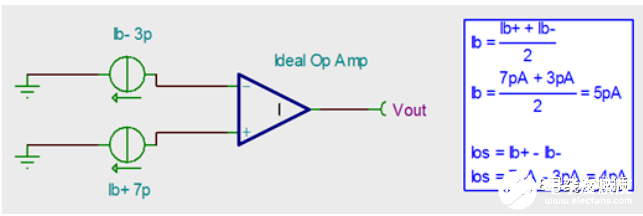

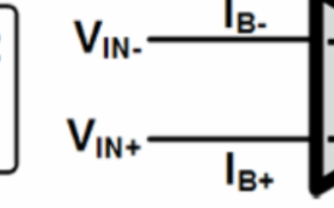

第一節要說明的是運放的輸入偏置電流Ib和輸入失調電流Ios .眾說周知,理想運放是沒有輸入偏置電流Ib和輸入失調電流Ios .的。但每一顆實際運放都會有輸入偏置電流Ib和輸入失調電流Ios .我們可以用下圖中的模型來說明它們的定義。

輸入偏置電流Ib是由于運放兩個輸入極都有漏電流(我們暫且稱之為漏電流)的存在。我們可以理解為,理想運放的各個輸入端都串聯進了一個電流源,這兩個電流源的電流值一般為不相同。也就是說,實際的運入,會有電流流入或流出運放的輸入端的(與理想運放的虛斷不太一樣)。那么輸入偏置電流就定義這兩個電流的平均值,這個很好理解。輸入失調電流呢,就定義為兩個電流的差。

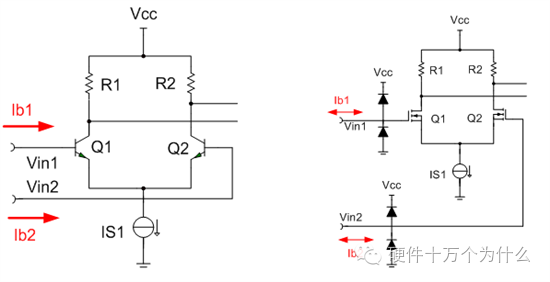

說完定義,下面我們要深究一下這個電流的來源。那我們就要看一下運入的輸入級了,運放的輸入級一般采用差分輸入(電壓反饋運放)。采用的管子,要么是三級管bipolar,要么是場效應管FET。如下圖所示,對于bipolar,要使其工作在線性區,就要給基極提供偏置電壓,或者說要有比較大的基極電流,也就是常說的,三極管是電流控制器件。那么其偏置 電流就來源于輸入級的三極管的基極電流,由于工藝上很難做到兩個管子的完全匹配,所以這兩個管子Q1和Q2的基極電流總是有這么點差別,也就是輸入的失調電流。Bipolar輸入的運放這兩個值還是很可觀的,也就是說是比較大的,進行電路設計時,不得不考慮的。而對于FET輸入的運放,由于其是電壓控制電流器件,可以說它的柵極電流是很小很小的,一般會在fA級,但不幸的是,它的每個輸入引腳都有一對ESD保護二極管。這兩個二極管都是有漏電流的,這個漏電流一般會比FET的柵極電流大的多,這也成為了FET輸入運放的偏置電流的來源。當然,這兩對ESD保護二極管也不可能完全一致,因此也就有了不同的漏電流,漏電流之差也就構成了輸入失調電流的主要成份。

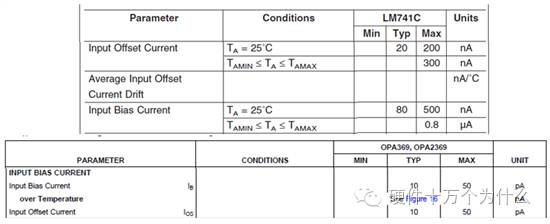

下面列表中上表是bipolar的LM741的輸入偏置電流和輸入失調電流,這個電流流到外面電阻,即使是K歐級的,也會產生幾十uV的失調電壓,再經放大,很容易就會使輸出的電壓誤差到mV級。下表則是CMOSFET的OPA369的輸入偏置電流和輸入失調電流,這兩個值要小的多了,比較好的COMS運放輸入偏置電流和輸入失調電流的典型值可以做到小于1pA的目標。

這里還要強調的是,ESD的反向漏電流是與其反相電壓有關的。因此當Vin=(Vcc-Vss)/2 時,加在兩個ESD保護二極管的電壓相當,他們的反向電流可以認為是近似相等的,此時理想情況是無電流流入或流出的,實際情況是電流達到最小值。因此這時有最小的偏置電流,當運放輸入端電壓Vin不等于(Vcc-Vss)/2,勢必造成一個二極管的反向電壓高,另一個低,此時兩個二極管的反向漏電流就不等了,這個差電流就會構成了輸入偏置電流的主要成份。這個現場稱為領節效應。因此要使FET輸入偏置電流最小,就要把共模電壓設置在(Vcc-Vss)/2處。

上面分析了定義和來源。下面就要說說這兩個參數對電路的影響了,輸入偏置電流會流過外面的電阻網絡,從而轉化成運放的失調電壓,再經運放話后就到了運入的輸出端,造成了運放的輸入誤差。這也就說明了,在反向放大電路中,為什么要在運放的同相輸入端連一個電阻再接地的原因。并且這個電阻要等于反向輸入端的電阻和反饋電阻并聯后的值。這就是為了使兩個輸入端偏置電流流過電阻時,形成的電壓值相等,從而使它們引入的失調電壓為0。這樣說,太抽象了,還是看下面一組圖容易理解一些。

再有一點,對于微小電流檢測的電路,一般為跨阻放大電路,如光電二極管的探測電路,一般有用光信號都比較微弱轉化的光電源信號更微弱,常常為nA級甚于pA級。這個電路的本意是想讓光電流向反饋電阻流動從而在放大電路輸出端產生出電壓。如果選用的運放的輸入偏置電流過大,剛這個微弱的光電流會有一部分流入到運放的輸入端,而達不到預設的I/V線性轉化。

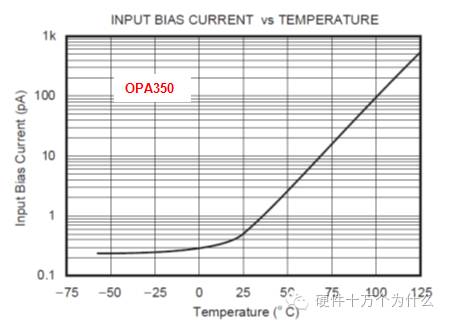

還需要注意的一點時,許多運放的輸入失調電流會隨著溫度的變化而變化,如下圖所示OPAl350的輸入失調電流會在高于25度時快速的升高。在100度時的輸入偏置電流是25度時的幾百倍。如果設計的系統是在很寬的溫度范圍內工作,這一因素不得不考慮。

以上啰啰嗦嗦的講了運放的輸入偏置電流和失調電流,希望對大家有用。

-

輸入偏置電流

+關注

關注

0文章

8瀏覽量

5884 -

輸入失調電流

+關注

關注

0文章

4瀏覽量

6102

原文標題:輸入偏置電流和輸入失調電流

文章出處:【微信號:eet-china,微信公眾號:電子工程專輯】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

快速了解運放的輸入偏置電流Ib和輸入失調電流Ib_os參數

運放的靜態參數輸入偏置電流Ib和輸入失調電流及溫度漂移

輸入偏置電流和輸入失調電流(運放參數的詳細解釋和分析)

輸入偏置電流和輸入失調電流對電路的影響是什么

運放參數的詳細解釋和分析:輸入偏置電流和輸入失調電流

深度解析輸入偏置電流和輸入失調電流的定義來源以及對電路的影響

深度解析輸入偏置電流和輸入失調電流的定義來源以及對電路的影響

深度解析輸入偏置電流和輸入失調電流的定義來源以及對電路的影響

評論