以下文章來(lái)源于Altium ,作者Altium

如今,可以認(rèn)為大多數(shù)PCB存在某種類(lèi)型的信號(hào)完整性問(wèn)題的風(fēng)險(xiǎn),這種問(wèn)題通常與高速數(shù)字設(shè)計(jì)相關(guān)。高速PCB設(shè)計(jì)和布局專(zhuān)注于創(chuàng)建不易受信號(hào)完整性、電源完整性和EMI/EMC問(wèn)題影響的電路板設(shè)計(jì)。雖然沒(méi)有任何設(shè)計(jì)能夠完全避免這些問(wèn)題,但通過(guò)遵循這些高速電路板設(shè)計(jì)指南,可以將其減少到不明顯的程度,并且不會(huì)在最終產(chǎn)品中造成性能問(wèn)題。

創(chuàng)建原理圖并準(zhǔn)備過(guò)渡到PCB布局后,您需要利用PCB設(shè)計(jì)工具中的特定功能來(lái)正確布局和布線。在您的PCB設(shè)計(jì)軟件中,您將有機(jī)會(huì)在疊層中準(zhǔn)備電源和接地平面布置、計(jì)算走線的阻抗曲線并查看疊層的PCB材料選項(xiàng)。高速設(shè)計(jì)的大多數(shù)方面都圍繞PCB疊層設(shè)計(jì)和布線以確保信號(hào)和電源完整性,而一個(gè)合適的ECAD軟件可以幫助您在這些領(lǐng)域取得成功。

高速數(shù)字設(shè)計(jì)基礎(chǔ)知識(shí)

那么,什么是高速電路板設(shè)計(jì)?高速設(shè)計(jì)特指使用高速數(shù)字信號(hào)在元件之間傳遞數(shù)據(jù)的系統(tǒng)。高速數(shù)字設(shè)計(jì)與采用較慢數(shù)字協(xié)議的簡(jiǎn)單電路板之間的分界線是模糊的。用于將特定系統(tǒng)表示為“高速”的一般指標(biāo)是系統(tǒng)中使用的數(shù)字信號(hào)的邊沿速率(或上升時(shí)間)。大多數(shù)數(shù)字設(shè)計(jì)同時(shí)使用高速(快邊沿速率)和低速(慢邊沿速率)數(shù)字協(xié)議。在當(dāng)今的嵌入式計(jì)算和物聯(lián)網(wǎng)時(shí)代,大多數(shù)高速電路板都有一個(gè)用于無(wú)線通信和網(wǎng)絡(luò)的RF前端。

盡管所有設(shè)計(jì)都從原理圖開(kāi)始,但高速PCB設(shè)計(jì)的主要部分集中在互連設(shè)計(jì)、PCB堆疊設(shè)計(jì)和布線上。如果您在前兩個(gè)方面均取得成功,那么在第三個(gè)方面也很可能會(huì)成功。請(qǐng)閱讀以下部分,了解如何著手高速設(shè)計(jì),以及PCB設(shè)計(jì)軟件的重要作用。

規(guī)劃您的高速PCB疊層和阻抗

您為高速電路板創(chuàng)建的PCB疊層將決定阻抗以及布線的難易程度。所有PCB疊層都包括一組專(zhuān)用于高速信號(hào)、電源和接地平面的層,在疊層中分配層時(shí)需要考慮以下幾點(diǎn):

電路板尺寸和網(wǎng)數(shù):電路板有多大,您需要在PCB布局中布線多少網(wǎng)。物理意義上較大的電路板可能有足夠的空間允許您在整個(gè)PCB布局中布線,而無(wú)需使用多個(gè)信號(hào)層。

布線密度:在網(wǎng)數(shù)較高且電路板尺寸受限于較小區(qū)域的情況下,表層周?chē)赡軟](méi)有太多布線空間。因此,當(dāng)走線靠得更近時(shí),您將需要更多的內(nèi)部信號(hào)層。采用較小的電路板尺寸可能會(huì)強(qiáng)制提高布線密度。

接口數(shù)量:有時(shí)每層僅布線一個(gè)或兩個(gè)接口是很好的策略,具體取決于總線寬度(串聯(lián)與并聯(lián))和電路板尺寸。將所有信號(hào)保持在同一層的高速數(shù)字接口中可確保所有信號(hào)看到一致的阻抗和偏斜。

低速和RF信號(hào):您的數(shù)字設(shè)計(jì)中是否會(huì)有任何低速數(shù)字或RF信號(hào)?如果是這樣,這些可能會(huì)占用表面層上可用于高速總線或元件的空間,并且可能需要額外的內(nèi)部層。

電源完整性:電源完整性的基石之一是使用大型電源平面和接地層來(lái)滿足大型集成電路所需的每個(gè)電壓等級(jí)。這些應(yīng)該放在相鄰的層上,以幫助確保有高平面電容來(lái)支持去耦電容器的穩(wěn)定電源。

PCB材料選項(xiàng)、層數(shù)和厚度

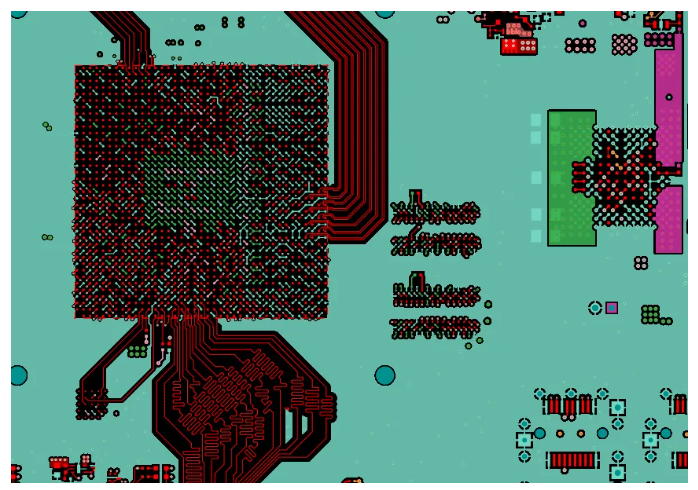

在設(shè)計(jì)PCB疊層之前,請(qǐng)考慮設(shè)計(jì)中容納所有數(shù)字信號(hào)所需的層數(shù)。有幾種方法可以確定這一點(diǎn),但是這些方法依賴(lài)于一點(diǎn)數(shù)學(xué)知識(shí)以及在高速電路板設(shè)計(jì)方面的過(guò)往經(jīng)驗(yàn)。除了上面列出的考慮層數(shù)的要點(diǎn)外,具有BGA/LGA封裝的大型高速I(mǎi)C也可以決定所需的電路板尺寸。在進(jìn)行BGA扇出時(shí),每個(gè)信號(hào)層通常可以容納2行,并且在構(gòu)建疊層時(shí)確保在層數(shù)中包括電源層和接地平面層數(shù)。

附帶大型多邊形的FPGA上的BGA扇出用于在高速設(shè)計(jì)中供電

只要元件之間的線路不過(guò)長(zhǎng),F(xiàn)R4級(jí)材料通常可用于高速數(shù)字設(shè)計(jì)。如果布線確實(shí)變得過(guò)長(zhǎng),高速通道就會(huì)有過(guò)多損失,并且通道接收端的元件可能無(wú)法恢復(fù)信號(hào)。選擇材料時(shí)要考慮的主要材料特性是PCB層壓板的損耗角正切。通道幾何形狀也將決定損耗,但通常選擇損耗角正切較低的FR4層壓板是在較小型電路板中開(kāi)始的好地方。

如果您的布線過(guò)長(zhǎng),則可能需要更專(zhuān)業(yè)的材料作為高速信號(hào)的基板。基于PTFE的層壓板、偏光玻璃層壓板或其他特殊材料系統(tǒng)是支持更大的高速數(shù)字電路板的不錯(cuò)選擇,這些電路板的布線非常長(zhǎng)且需要低插入損耗。370HR是一套適用于小型高速PCB的入門(mén)級(jí)高TG層壓材料。對(duì)于較大的電路板,Megtron或Duroid層壓板等材料也是不錯(cuò)的選擇。在繼續(xù)之前,請(qǐng)咨詢(xún)您的制造商,確保您的材料選擇和建議的堆疊是可制造的。

阻抗控制

只有在您創(chuàng)建擬議的疊層并與你的制造廠完成驗(yàn)證后,才能確定阻抗。制造商可以提議對(duì)PCB堆疊進(jìn)行修改,例如替代的PCB材料選項(xiàng)或?qū)雍穸取T诏B層上獲得間隙并最終確定層厚度后,您就可以開(kāi)始計(jì)算阻抗值。

阻抗通常使用公式或附帶場(chǎng)求解器工具的計(jì)算器進(jìn)行計(jì)算。設(shè)計(jì)中所需的阻抗將決定傳輸線的尺寸,以及與附近電源層或接地層的距離。傳輸線的寬度可以通過(guò)以下一些工具來(lái)確定:

IPC-2141和Waddell公式:這些公式為阻抗估計(jì)提供了一個(gè)起點(diǎn),并且它們?cè)谳^低頻率下產(chǎn)生準(zhǔn)確的結(jié)果。

2D/3D場(chǎng)求解器實(shí)用程序:場(chǎng)求解器用于在您為高速板定義的傳輸線幾何結(jié)構(gòu)內(nèi)求解麥克斯韋方程。

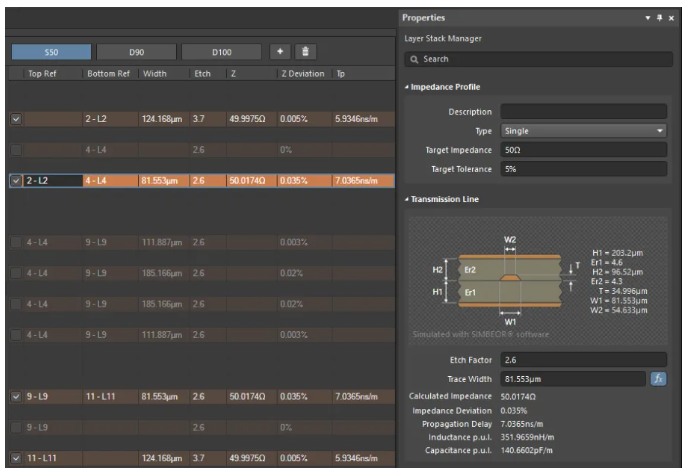

使用附帶場(chǎng)求解器的層堆疊管理器將為您提供最準(zhǔn)確的結(jié)果,同時(shí)考慮到銅的粗糙度、蝕刻、不對(duì)稱(chēng)線路排列和差分對(duì)。計(jì)算出走線的阻抗曲線后,您需要在布線工具中將其設(shè)置為設(shè)計(jì)規(guī)則,以確保走線具備所需的阻抗。

高速電路板中傳輸線設(shè)計(jì)的阻抗計(jì)算。Altium Designer中的“層堆棧管理器”包含一個(gè)阻抗計(jì)算器,用于計(jì)算銅的粗糙度。

大多數(shù)高速信號(hào)協(xié)議,如PCIe或以太網(wǎng),都使用差分對(duì)布線,所以您需要通過(guò)計(jì)算走線寬度和間距來(lái)設(shè)計(jì)成特定的差分阻抗。場(chǎng)求解器工具是計(jì)算任何幾何形狀(微帶線、帶狀線或共面)的微分阻抗的最佳工具。場(chǎng)求解器工具的另一個(gè)重要結(jié)果是傳播延遲,它將在高速布線過(guò)程中被用來(lái)執(zhí)行長(zhǎng)度調(diào)整。

對(duì)高速PCB進(jìn)行布局規(guī)劃

對(duì)于高速PCB布局中元件的布置位置,沒(méi)有具體的規(guī)則或標(biāo)準(zhǔn)。一般來(lái)說(shuō),將最大的中央處理器IC放置在靠近電路板中心的位置是個(gè)好主意,因?yàn)樗ǔP枰阅撤N方式與電路板上的所有其他元件連接。可將直接與中央處理器連接的較小IC放置在中央IC周?chē)员阍g的布線可以保持短而直接。然后,可在電路板周?chē)胖猛鈬O(shè)備,以提供所需的功能。

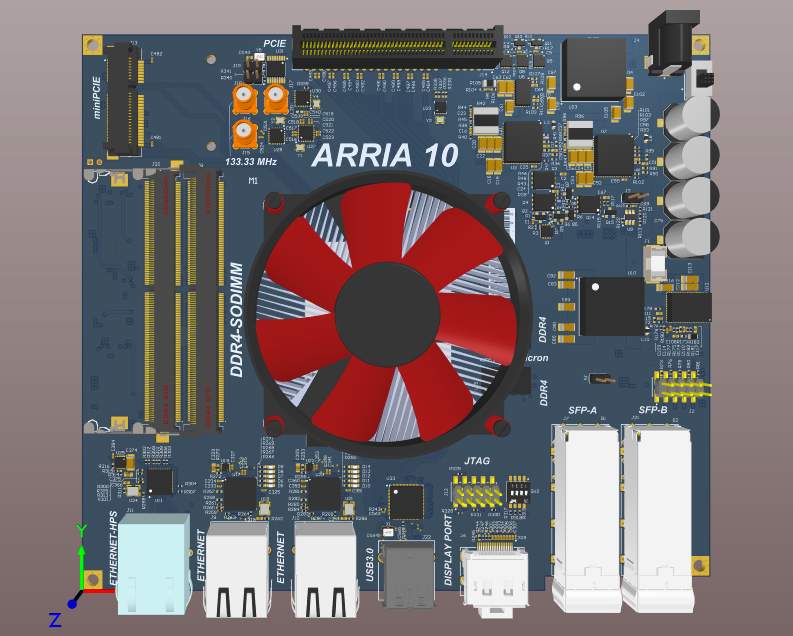

當(dāng)主控制器IC放置在電路板的中心附近,而其他高速外圍設(shè)備放置在其周?chē)鷷r(shí),高速布局效果最佳。這是主板在電路板中央放置大型處理器的原因之一。Altium Designer中的MiniPC項(xiàng)目將其PCIe、DDR4、USB 3.0和以太網(wǎng)外圍設(shè)備放置在中央FPGA SoC周?chē)虼瞬季€更加容易。

放置元件后,您可以使用PCB設(shè)計(jì)工具來(lái)幫助您開(kāi)始設(shè)計(jì)布線。這是高速數(shù)字電路設(shè)計(jì)的敏感部分,因?yàn)椴徽_的布線會(huì)破壞信號(hào)完整性。如果正確完成前面的步驟,則更容易實(shí)現(xiàn)信號(hào)完整性。您應(yīng)該在PCB設(shè)計(jì)規(guī)則中設(shè)置阻抗曲線,以便設(shè)計(jì)中的任何布線均以正確的寬度、間隙和間距放置,在布線過(guò)程中保持受控阻抗。

布線、信號(hào)完整性和電源完整性

信號(hào)完整性始于設(shè)計(jì)電路板的特定阻抗值并在布局和布線期間保持該阻抗值。確保信號(hào)完整性的其他一些策略包括:

旨在縮短元件之間的路徑以確保高速信號(hào)

盡量減少通過(guò)過(guò)孔的布線,理想情況下僅使用兩個(gè)過(guò)孔進(jìn)出內(nèi)層

通過(guò)背鉆消除超高速線路(例如 10G+ 以太網(wǎng))上的短截線

注意是否需要任何終端電阻以防止信號(hào)反射;查看數(shù)據(jù)表以檢查是否存在片上終端

請(qǐng)咨詢(xún)您的制造商,了解哪些材料和工藝可以幫助避免纖維編織效應(yīng)

使用粗略的串?dāng)_計(jì)算或模擬來(lái)確定電路板布局中網(wǎng)絡(luò)之間的適當(dāng)間距

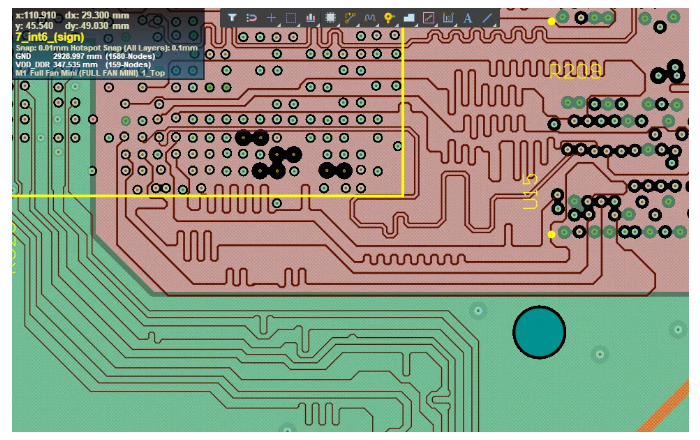

保留需要長(zhǎng)度匹配的總線和網(wǎng)絡(luò)列表,以便可以應(yīng)用調(diào)整結(jié)構(gòu)來(lái)消除偏移

這些要點(diǎn)可以設(shè)置為布線工具的設(shè)計(jì)規(guī)則,這將有助于確保您遵守高速設(shè)計(jì)的最佳實(shí)踐。

高速PCB布線

您在高速設(shè)計(jì)項(xiàng)目中設(shè)置的設(shè)計(jì)規(guī)則將確保您在設(shè)計(jì)布線時(shí)滿足阻抗、間距和長(zhǎng)度目標(biāo)。此外,可以在您的布線中強(qiáng)制執(zhí)行差分對(duì)布線中的重要規(guī)則,特別是最小化長(zhǎng)度不匹配,以防止走線之間的偏移和強(qiáng)制間距,以確保滿足差分阻抗目標(biāo)。最好的布線工具將允許您將走線幾何限制編輯為設(shè)計(jì)規(guī)則,從而確保性能。

長(zhǎng)度調(diào)整用于跨并行總線和差分對(duì)中的走線之間,以確保時(shí)延匹配并消除接收器上所見(jiàn)信號(hào)之間的偏差。

高速PCB布線中最重要的一點(diǎn)是在走線附近放置接地平面。疊層應(yīng)構(gòu)建為在與阻抗控制信號(hào)相鄰的層中具有接地平面,以便保持一致的阻抗并在PCB布局中定義清晰的返回路徑。不應(yīng)在接地層中的間隙或裂縫上放置走線,以避免產(chǎn)生EMI問(wèn)題的阻抗不連續(xù)性。接地平面布置并不局限于確保信號(hào)完整性,它在電源完整性和確保穩(wěn)定的電力輸送方面也發(fā)揮著作用。

電源完整性

電源完整性是一個(gè)廣泛的話題,與高速PCB設(shè)計(jì)高度相關(guān)。確保向高速元件提供穩(wěn)定的功率在PCB設(shè)計(jì)中至關(guān)重要,因?yàn)殡娫赐暾詥?wèn)題可能偽裝成信號(hào)完整性問(wèn)題。電源完整性側(cè)重于向元件提供低噪聲電力。PCB疊層和PDN的布局是決定數(shù)字設(shè)計(jì)中電源完整性水平的主要因素。如果成功完成,功率將輸送到具有低噪聲和電源軌上非常微弱的瞬態(tài)振蕩的快速數(shù)字元件。設(shè)計(jì)具有良好電源完整性的高速PCB可確保低排放、低噪聲功率輸送,并消除高速互連中出現(xiàn)的一些SI問(wèn)題。

適用于高速設(shè)計(jì)和布局的高級(jí)工具

一個(gè)優(yōu)秀的高速PCB設(shè)計(jì)軟件會(huì)將所有這些功能整合到一個(gè)應(yīng)用中,而不是強(qiáng)迫您使用單獨(dú)的工作流程來(lái)克服不同的設(shè)計(jì)挑戰(zhàn)。高速PCB布局設(shè)計(jì)人員必須在前端執(zhí)行大量工作以確保信號(hào)完整性、電源完整性和電磁兼容性,但是正確的高速布局工具可以幫助您將結(jié)果作為設(shè)計(jì)規(guī)則實(shí)施,以確保設(shè)計(jì)按預(yù)期執(zhí)行。

更高級(jí)的PCB設(shè)計(jì)軟件將與仿真應(yīng)用對(duì)接,以幫助您執(zhí)行符合行業(yè)標(biāo)準(zhǔn)的分析。一些仿真程序?qū)iT(mén)用于評(píng)估新設(shè)計(jì)中的信號(hào)完整性和電源完整性,以及檢查PCB布局中的EMI。仿真在高速設(shè)計(jì)中非常有用,因?yàn)樗鼈兛梢詭椭脩?hù)在設(shè)計(jì)進(jìn)入制造之前查明具體的SI/PI/EMI問(wèn)題。一些示例包括返回路徑跟蹤、在走線中定位阻抗不連續(xù)性,以及為防止EMI而采用去耦電容器的理想布局。

使用高速設(shè)計(jì)軟件完成您的物理布局

當(dāng)您需要構(gòu)建先進(jìn)的高速數(shù)字系統(tǒng),同時(shí)確保維持信號(hào)完整性和電源完整性時(shí),請(qǐng)使用基于規(guī)則驅(qū)動(dòng)設(shè)計(jì)引擎的最佳高速設(shè)計(jì)和布局工具集。無(wú)論您需要布局密集的單板計(jì)算機(jī)還是復(fù)雜的混合信號(hào)PCB,優(yōu)秀的PCB布局工具將幫助您在創(chuàng)建高速PCB布局時(shí)保持靈活性。

-

pcb

+關(guān)注

關(guān)注

4351文章

23405瀏覽量

406615 -

PCB設(shè)計(jì)

+關(guān)注

關(guān)注

396文章

4775瀏覽量

89137 -

疊層設(shè)計(jì)

+關(guān)注

關(guān)注

0文章

28瀏覽量

6338

原文標(biāo)題:什么是高速PCB設(shè)計(jì)?

文章出處:【微信號(hào):發(fā)燒友研習(xí)社,微信公眾號(hào):發(fā)燒友研習(xí)社】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

評(píng)論