文章來源:SPICE 模型

原文作者:若明

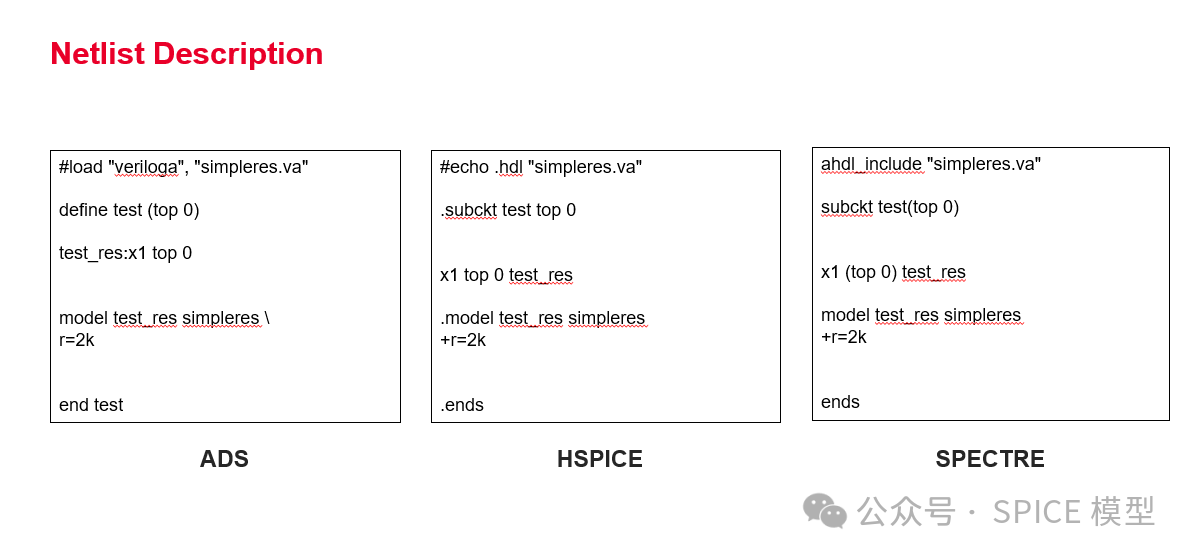

Verilog-A對緊湊型模型的支持逐步完善,在模型的實現上扮演越來越重要的角色,已經成為緊湊模型開發的新標準。而且Verilog-A能夠在抽象級別和應用領域中擴展SPICE建模和仿真功能,因此學會如何用Verilog-A來開發器件模型在建模領域將尤為重要。今天就來以簡單的例子來介紹如何開發一個Verilog-A Model。

SPICE電路元件模型通常稱為緊湊型模型。它們應該足夠簡單,以提供有效的電路仿真,并足夠精確,使仿真結果對電路設計者有用。隨著在LRM 2.2中引入語言擴展以支持緊湊的器件建模,Verilog-A已成為電子行業中用于開發有源和無源半導體器件緊湊模型的標準語言。

假設:

您是一個器件工程師/研究者

您需要的是一個Compact Spice Model(而不是TCAD Model)

您對一個器件的物理特性比較了解

您需要理解的是:

什么是Compact Model

電路仿真器如何使用一個Compact Model

如何將器件的電路方程編寫為Verilog-A Model

需要了解一些常見的錯誤和Debug的能力

需要知道如何測試您的Model

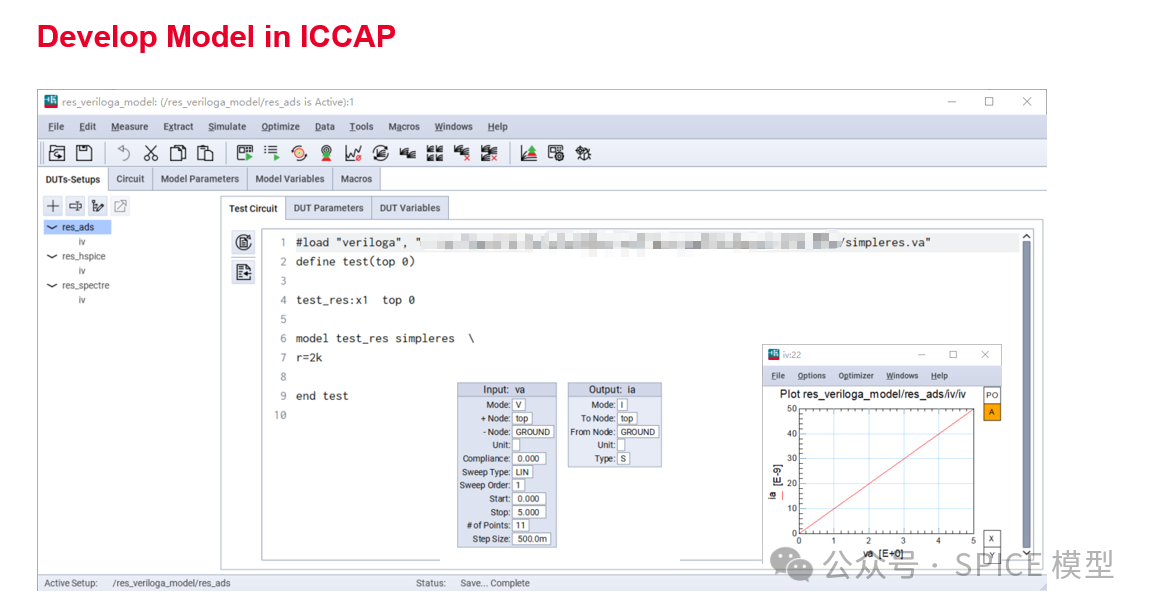

一個簡單的例子

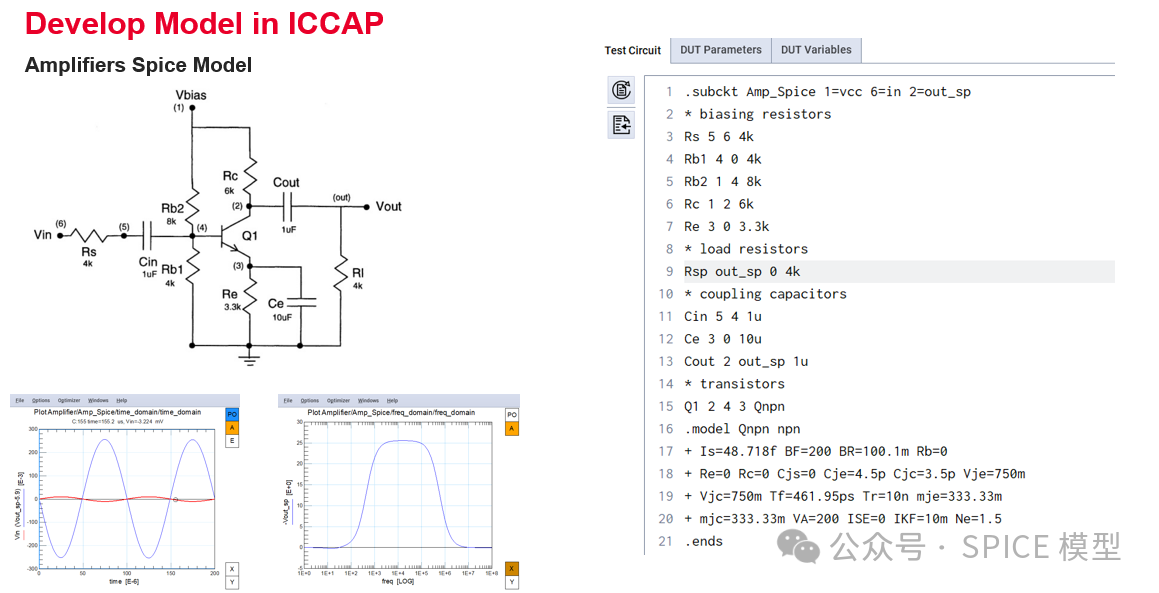

Amplifier Model的例子

對一個放大器建模是一個比較基礎的例子,但是要增加額外的效應,則是具有挑戰性的。如果簡單的來考慮放大器,可以簡單的認為輸出為增益乘以輸入。我們從電路設計的角度,自下而上地來看一個放大器的模型:Spice晶體管級模型,功能級模型,結構級模型,行為級模型。

Spice晶體管級模型

在晶體管級模型,首先要非常清楚最底層的放大器的電路是如何設計的,并且要有每一個最底層的元器件的Spice Model。要按照電路使用Spice語法描述電路,搭建Subckt Model。Spice Model多用于IC設計領域。

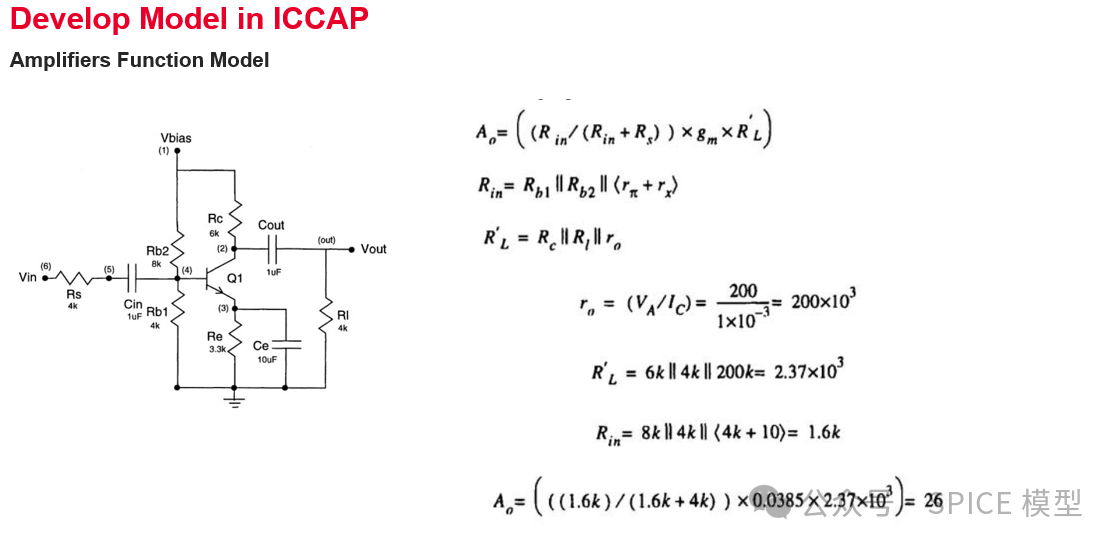

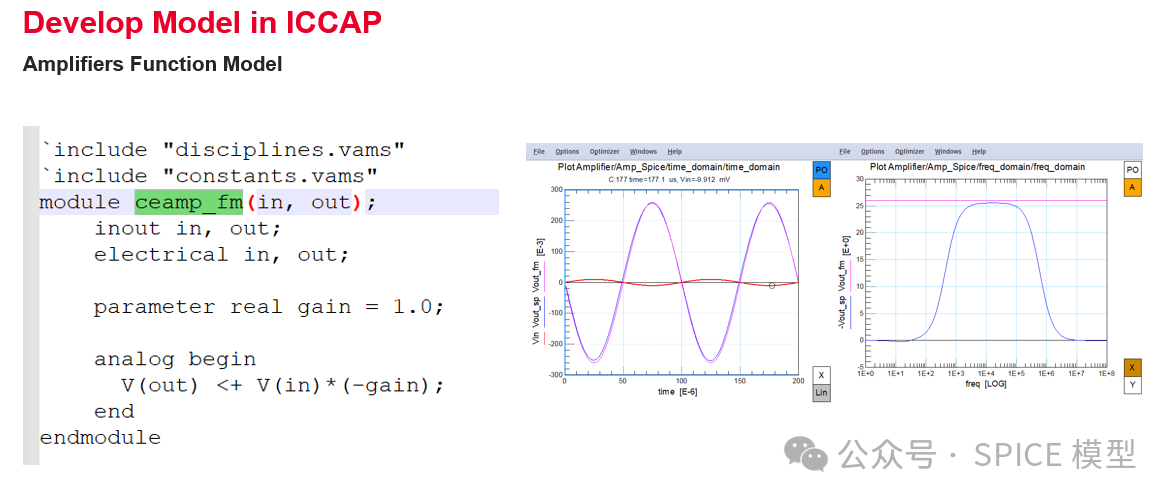

功能級模型

在功能級模型,首先要對電路功能進行分析。以放大器為例,我們最關心的功能是其放大增益,經過推導,推導出增益,然后以Verilog-A來實現。

在這里gain作為放大器的參數,可以改變。如下圖所示,與Spice Model比較,只反映出放大特性,沒有考慮頻率的響應。

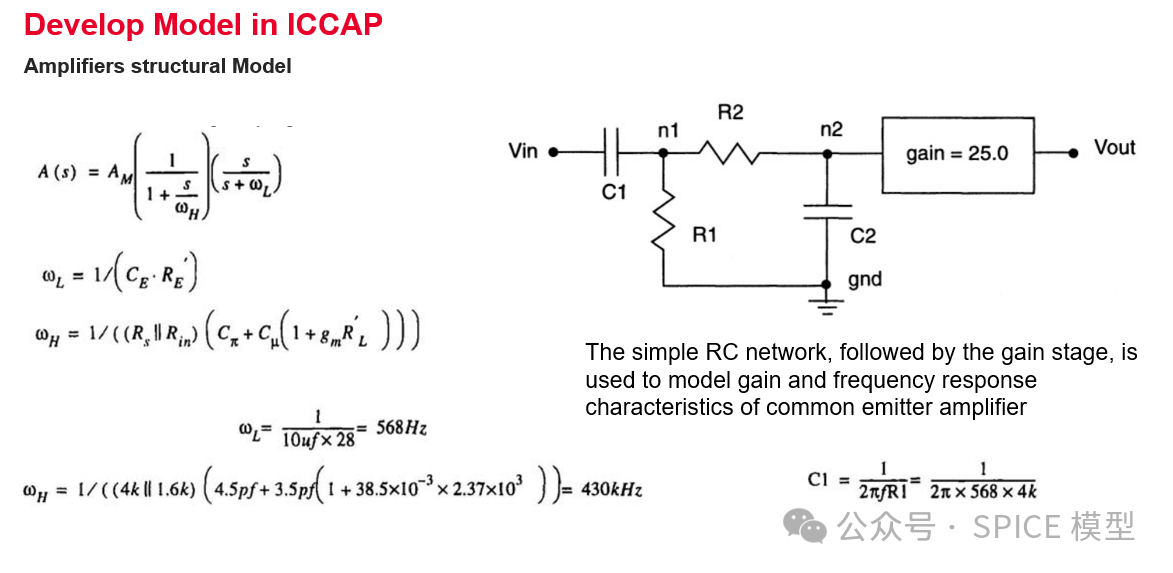

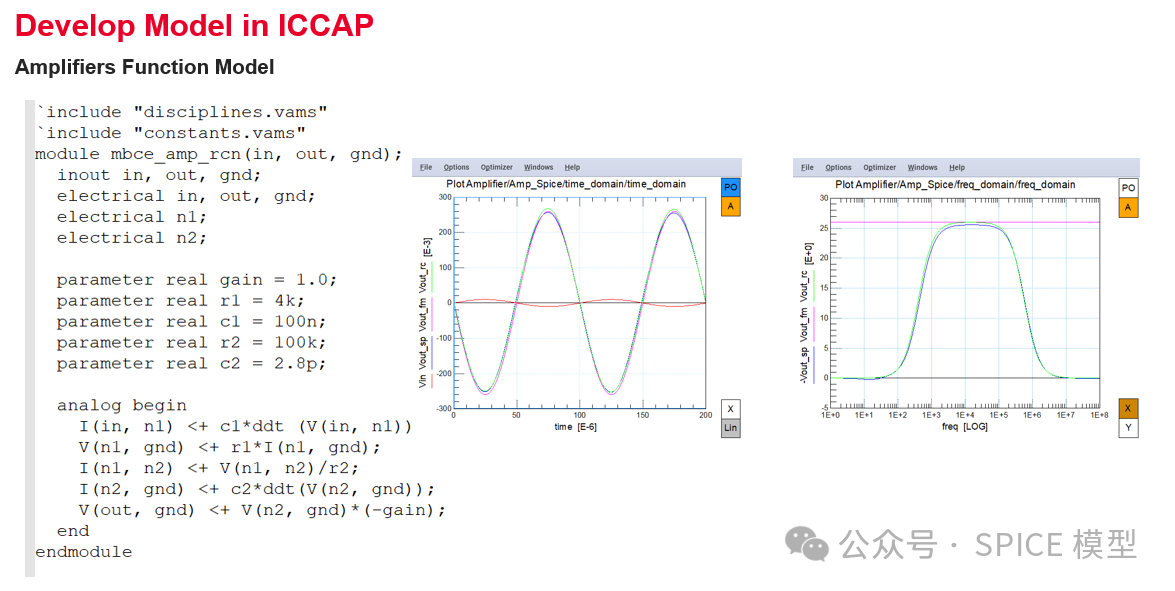

結構級模型

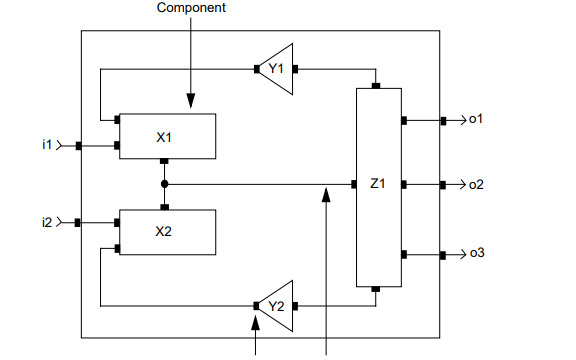

如果在簡單的增益模型的基礎上考慮頻率的響應,我們可以通過結構級模型實現。首先,要考慮放大器對頻率的特性,通過推導,發現其頻率相應可以通過RC網絡來實現。

在這里增加RC網絡的參數,來表征放大器對頻率的響應。如下圖所示,通過調諧RC網絡參數,可以達到和Spice Model接近的效果。

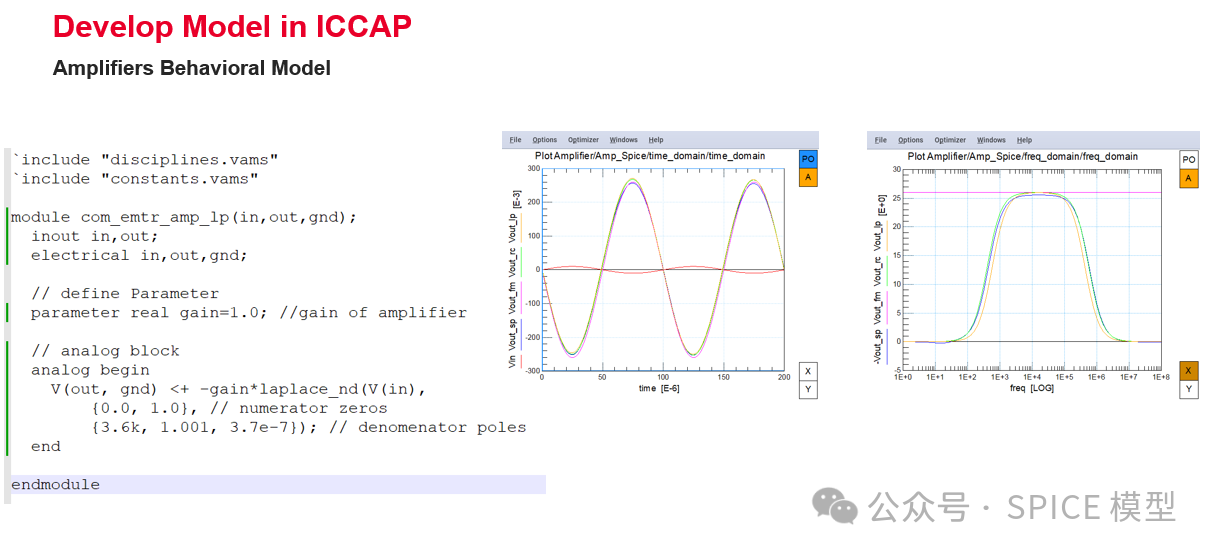

行為級模型

Verilog-A語言包括實現集總線性連續時間濾波器的內置拉普拉斯變換函數。該變換用于模擬放大器的頻率效應,將其行為視為一個簡單的帶通濾波器。此類模型我們可以認為是行為級模型,通常在更頂層的系統級電路中使用。如下圖所示,與Spice Model比,也能夠達到接近的效果。

-

半導體

+關注

關注

335文章

28012瀏覽量

225455 -

仿真

+關注

關注

50文章

4155瀏覽量

134481 -

SPICE

+關注

關注

6文章

189瀏覽量

42936 -

模型

+關注

關注

1文章

3415瀏覽量

49475 -

電路元件

+關注

關注

0文章

118瀏覽量

11119

原文標題:如何利用Verilog-A 開發器件模型?

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

DxDesigner建模

業界領先的半導體器件SPICE建模平臺介紹

Verilog-A的模擬電路行為模型及仿真

Cadence中Verilog語言參考使用教程免費下載

ST公司的M25Pxx SPI flash memory的verilog仿真模型

如何利用Verilog-A開發器件模型

如何利用Verilog-A開發器件模型

評論