在電子信息制造業的快速發展中,數字化和智能化已成為推動行業發展的雙引擎。5G技術的普及,更是為"電子+"趨勢提供了強有力的支撐。"電子+"戰略指的是通過電子和通信技術的廣泛應用,實現非電子產品的電子化和簡單電子產品的智能化。5G網絡的"低延遲、大帶寬、廣連接"特性,為生產設備、消費終端等萬物互聯提供了理想的網絡環境,智能汽車等新興領域的快速發展便是這一趨勢的生動體現。

1 現代電子裝聯工藝技術的概述

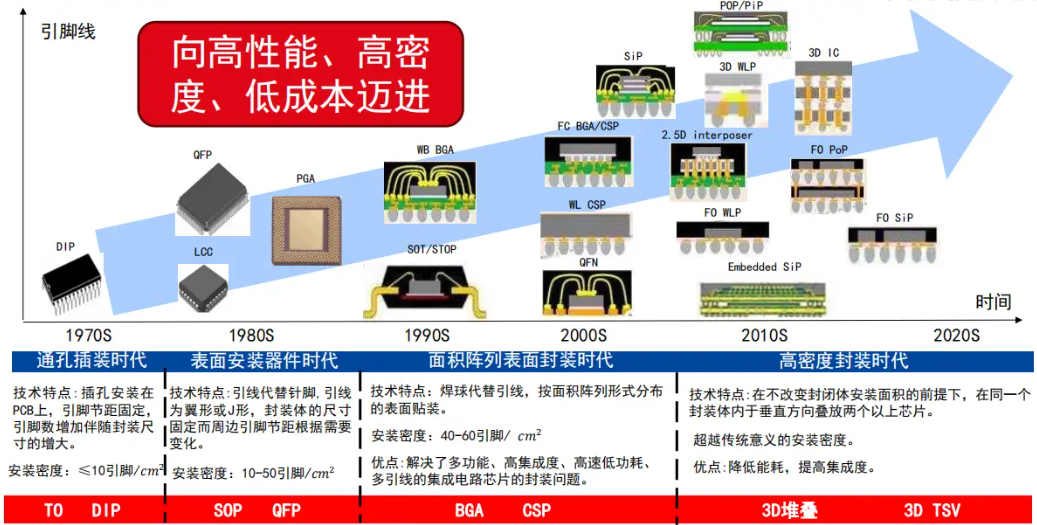

電子裝聯工藝的發展經歷了多個階段,從電子管時代到晶體管時代,再到集成電路時代、表面安裝時代,直至今天的微組裝時代。裝聯工藝技術經歷了三次重大革命:通孔插裝、表面安裝和微組裝。器件封裝技術也經歷了從QFP、BGA、CSP、DCA到MCM的演變。隨著小型和超小型器件的涌現,高密度組裝技術的發展推動了相關工藝和組裝設備的創新。

現代電子裝聯工藝主要包括裝聯前的準備、PCB組裝和整機組裝。裝聯前的準備包括元器件和PCB的可焊性測試、元器件引線的預處理、導線的端頭處理、PCB的復驗和預處理。PCB組裝通常包括通孔插裝、表面安裝和混合安裝,電氣互連技術包括手工焊接、波峰焊接、再流焊接、激光焊接、壓接、繞接等,清洗方式也多種多樣。整機組裝則涉及機械安裝、電氣互連、電纜組裝件制作、防護與加固等多個環節。

2 現代電子裝聯工藝技術更新現狀

2.1 系統級封裝技術-SIP

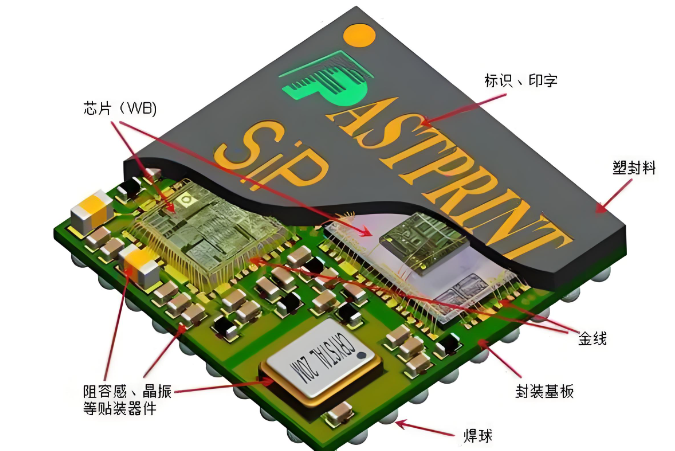

SIP技術融合了傳統的SMT組件制程工藝與芯片封裝工藝,其應用日益廣泛,尤其在AIoT產品與可穿戴電子產品領域。SIP技術可以實現多功能的集中,具有輕便性、超薄性、微小化、高傳輸性等特點。隨著技術要求與生產工藝難度的提高,整合封裝工藝和組件工藝,增強功能性,面臨著諸多挑戰。

在小型化消費電子市場的快速發展推動下,SiP技術得到了廣泛應用。預計到2025年,系統級封裝市場規模將達到188億美元,復合年增長率為6%。SiP技術的應用主要是將各類功能的有源電子元件與可選無源器件進行組裝,形成具有一定功能的單個標準封裝件,實現多類型功能芯片的集成封裝。

從SiP封裝工藝的運用分析,是按照一定的工序,在封裝基班上,進行器件的組裝互連,同時將芯片包封保護。按照芯片與基板的連接方式,SiP封裝制程可以備劃分為兩類,即引線鍵合封裝和倒裝焊兩種。以引線鍵合封裝流程為例,主要流程如下:(1)晶圓研磨。指的是采用機械或者CMP方式,完成研磨作業,將圓片處理到一定的薄度適合進行封裝作業。一般來說,主要包括貼膜、背面研磨、去膜三個環節。(2)晶圓切割。根據工藝流程,需要進行貼片,目的是防止芯片在收割時散落,同時也是方便后續芯片切單環節拾取芯片。芯片切單也就是芯片切割,可采用刀片切割法和激光切割方法。切割之后,全部的芯片都完全分離,放入到晶圓框架盒內,開展下道工序。

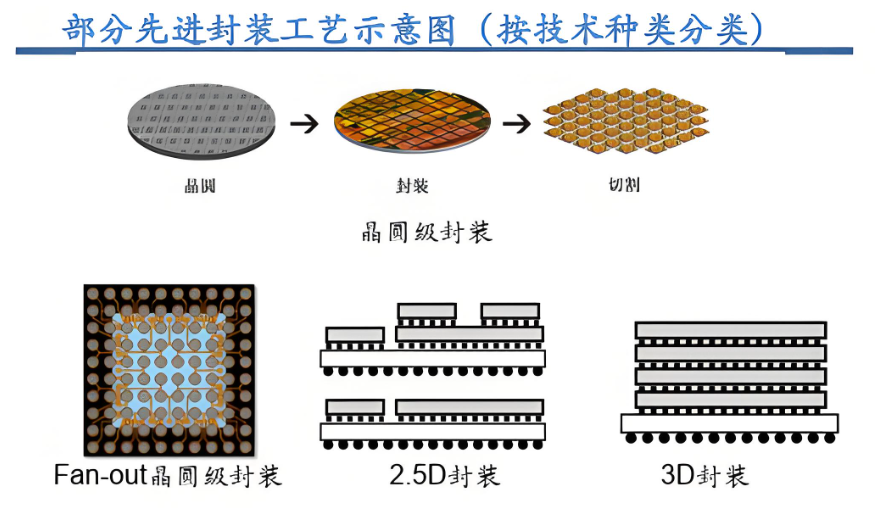

2.2 高密度先進封裝HDAP

高密度先進封裝HDAP已成為芯片封裝技術發展的熱點。這種技術采用先進的設計思路與集成工藝,實現芯片的封裝級重構,提高功能密度。先進封裝技術包括裝焊、晶圓級封裝(WLP)、2.5D封裝(RDL)、3D封裝(TSV)等。與傳統封裝工藝不同,先進封裝創新了封裝工藝,無Bonding Wire,且封裝集成度高,體積小,內部互聯短,系統性能得到全面提升。

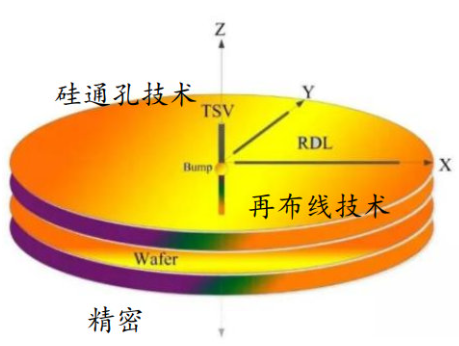

先進封裝的四個要素為:Bump、RDL、Wafer、TSV。其中,Bump為一種金屬凸點,自從倒裝焊Flip Chip出現就已經實現了廣泛應用,主要分為球狀與柱狀或者塊狀。隨著工藝技術水平的不斷提高,Bump尺寸可以越做越小。混合鍵合最為突出的特點就是無凸點的鍵合結構,在實際應用中可以達到高集成密度的水平。

RDL重布線層,XY平面電氣延伸和互聯。從實際應用的角度來說,進行芯片設計與制造,通常來說IO Pad分布在芯片的邊沿或四周圍,如果是Bond Wire工藝較為方便,但對于Flip Chip不適合。因此,RDL有了發揮空間。其在晶元表面沉積金屬層以及介質層,并且能夠形成金屬布線,實現進行IO端口的重新布局,布置到占位更加充足的區域,同時形成面陣列排布效果。從RDL的具體應用分析,在FIWLP中,此技術為關鍵技術之一,能夠將IO Pad進行扇入Fan-In,或者扇出Fan-Out,能夠形成多種類型的晶圓級封裝。如果是2.5D IC集成中,此技術的應用也比較重要,通過RDL將網絡互聯并且分部到相應的位置,最終實現硅基板上方芯片的Bump與基板下方的Bump的連接。如果是3D IC集成,當堆疊上下不是一樣的芯片,利用此技術重布線層促使上下層芯片的IO對準,最終完成電氣互聯。

Wafer晶圓被認為有著廣泛用途的技術,不僅能作為芯片制造的基底,也能夠在Wafer上制作硅基班實現2.5D集成。此外,還可以用于WLP晶圓級封裝,當作WLP的承載晶圓。不同于傳統的封裝技術,WLP在Wafer的基礎上先進行封裝,之后切割分片,全面提高了作業的效率,并且節約了一定的成本。從Wafer的尺寸變化來看,由最初的6英寸和8英寸,到當前的12英寸,未來會發展到18英寸。

TSV硅通孔的功能為Z軸電器延伸和互聯。根據集成類型進行劃分,主要為2.5D TSV與3D TSV。在一定的時間背景下,先進封裝僅僅是個概念,隨著技術的發展未來也會變成“傳統封裝”。根據四要素內在的先進性進行排序,具體為Bump、RDL、Wafer、TSV。

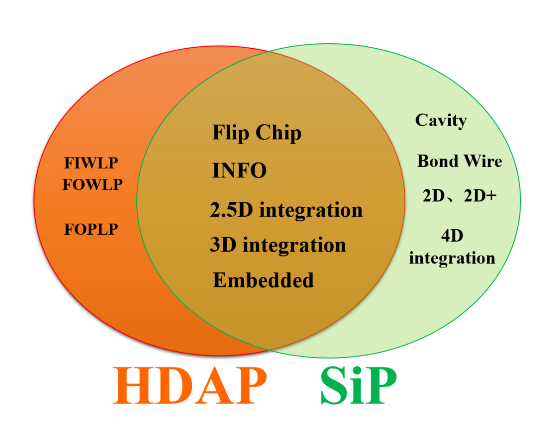

2.3 先進封裝與SiP的對比

SiP技術和先進封裝技術都是半導體產業鏈關注的焦點。從兩個技術的不同點分析,主要如下:(1)關注點。SiP技術重點是系統在封裝內部的實現,因此系統為技術的主要關注對象。與Sip系統級封裝相對的是單芯片封裝。這里所述的先進封裝,更加注重封裝技術和工藝的先進性,與其相對的是傳統封裝。(2)技術范疇不同。例如,單芯片的FIWLP、FOWLP以及FOPLP為先進封裝,不過不在SiP范疇內;FliP Chip和2.5D integration以及3D integration在HDAP范疇內,同時也可以應用在SiP。

這兩項技術都具有小型化、低功耗、高性能的特點,為電子系統集成提供解決方案。盡管兩項技術自身不存在瓶頸,但在裸芯片的供應鏈和芯片之間的接口標準方面,仍需進一步完善。

3 現代電子裝聯工藝技術的發展

3.1 借助自然原理

自然原理在生產過程中的應用是技術研究的重要內容。自然界中的物質對象極為復雜,它們通過耦合無數相同的元素來形成自身,如DNA雙螺旋線。這些結構在熱動力學平衡中不依賴共價化學鍵結合,比較容易被機械力影響,不過能夠持續地修復,進行自我的調整,同時也能夠借助每個顆粒的屬性實現構建,其中涵蓋表面張力與分子之間的耦合力。

從合成技術的角度來說,自組裝工藝技術的應用,要處于相應的條件中實現控制,進而獲得理想的結構或屬性,比如分子條件和壓力條件等。隨著半導體設備日益的微小化,帶動著現代電子裝聯工藝技術研究在這些方面進行。

3.2 封裝差距

隨著半導體尺寸的不斷縮小,許多機械組裝技術已無法滿足需求,先進封裝技術的應用研究因此受到廣泛關注。封裝差距指的是微型和中間規模的組裝封裝差距。按照摩爾定律,那么可能會遇到組裝問題。傳統的電子元器件封裝中,實現系統級封裝,有著一定的成本壓力。隨著新封裝技術的應用和發展,系統級封裝的水平將得到提高,封裝成本也將降低。

(未完,接下篇)

審核編輯 黃宇

-

激光

+關注

關注

19文章

3224瀏覽量

64602 -

焊錫

+關注

關注

0文章

271瀏覽量

18234

發布評論請先 登錄

相關推薦

光模塊技術發展趨勢 光模塊常見故障及解決方法

開關電源的最新技術發展趨勢

未來的ar技術發展趨勢

智能駕駛技術發展趨勢

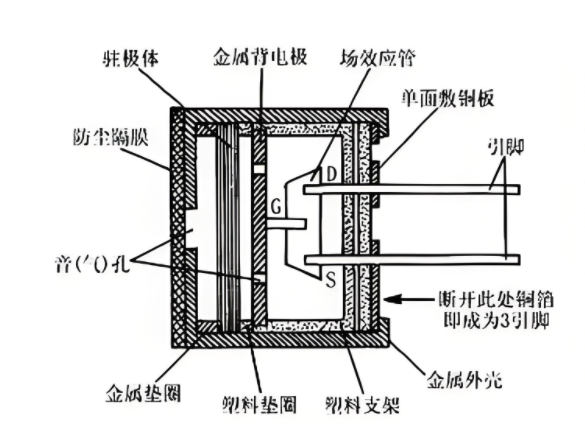

激光焊錫機:麥克風(咪頭)制造的精密焊接工藝

精密連接的創新者:激光焊錫機在傳感器制造中的優勢

無線充電技術發展趨勢

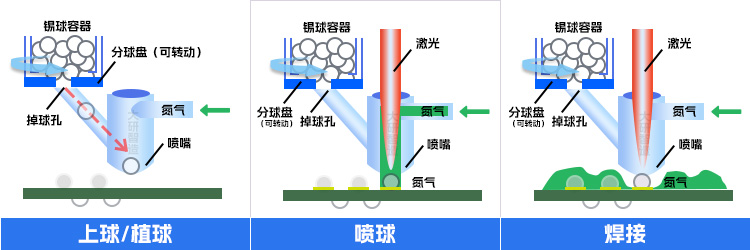

激光焊錫技術的優勢在哪

Molex推出的MID LDS技術哪里有?-赫聯電子

揭秘:PCB電子激光焊錫技術的檢測方法與應用范圍

電子裝聯工藝技術發展趨勢及激光焊錫技術的優勢(上)

電子裝聯工藝技術發展趨勢及激光焊錫技術的優勢(上)

評論