從理論上來說,物理綜合工具擁有關于布局的所有必要信息;在實踐中,它們也必須非常小心地與實際布局數據關聯。

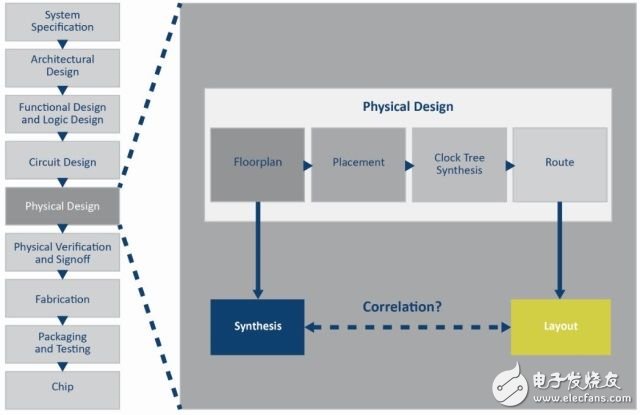

一個芯片的設計涉及到許多階段,從系統規范和架構設計,各種制造方法以及最終裝入設備的芯片成品的封裝。在這個周期中,準確估計時序和面積將至關重要,因為這樣才能制訂準確的計劃并使產品符合各方面的需求。本文將介紹這個過程的物理設計(或稱后端設計)部分,特別是在與物理設計相關的步驟中將時序與面積關聯起來。

集成電路 (IC) 設計流程和物理設計步驟 (圖1)

綜合與布局之間的關聯問題

大型設計的整個物理設計流程可能需要很多天才能完成。因此,如果能夠向設計和架構團隊盡早提供反饋,讓他們可以規劃好時序限制,自由地快速利用布局選項,將能夠創造寶貴的價值。為了實現這些目標,必須可靠地估計時序和面積。

在過去,我們已經很好地掌握了綜合布局與布線之間的相關性。對于時序,準確度在3%至4%左右,而面積的結果甚至更好。但在新的先進工藝中,從28 納米工藝節點開始,我們遇到了越來越多意想不到的結果。我們不僅看到了物理綜合結果與布局和布線的實際時序之間更大的差距,而且還看到一部分時序路徑明顯變得更快,而其他時序路徑則變慢很多,這相當令人費解。在觀察面積時,結果更令人擔憂。從綜合到布局,相關性已經變得相當差,如下圖所示:

布局規劃階段(頂部)與布局階段(底部)的綜合單元密度比較 (圖2)

上面的圖片是CEVA-XM4內核的單元密度圖,比較了綜合階段(頂部)與布局階段(底部)的單元密度。布局階段圖像的橙色部分顯示了面積的顯著增長。在這種情況下,面積的整體增長在18% 左右。這很不好,但也許還能忍受。但考慮到大部分設計是固定面積(內存和寄存器),從綜合到布局根本不會改變,就很清楚某些部分確實會超過最高限制。把緩沖器單元面積分離之后我們發現綜合面積增加了118%,這意味著緩沖器數和面積增加了一倍以上。

在達到極限單元密度(標記為橙色)的領域,布局工具發現很難確定單元的合理布局和進行多次迭代,因此需要花費大量時間進行收斂。

設法增強時序和面積的相關性

解決這個問題的第一次嘗試是收緊頻率。也就是說,我們盡量以較高的頻率進行綜合,然后在布局和布線階段再切換到稍微低一些的頻率。但這個解決方案并沒能解決問題。另一個嘗試是降低線網和單元的時序。實際上,降低時序就是增加讓單元處理速度更慢或更快的系數。我們嘗試了幾個數字。我們探索的另一個方向是提高提取數字的相關性。這是通過將系數應用于被提取的線網電阻和電容 (RC) 值來實現的。這些值通過更改其 RC 值直接影響線網的延遲,并通過改變其負載電容從而影響單元的延遲。

從電氣工程的角度來看,我們知道,隨著制程工藝的收縮,電阻的作用會越來越突出。一方面,導線的電容保持大致相同(或至少采用相同的順序)。另一方面,電阻會變得越來越高。除此之外,在先進的工藝節點上,最上面兩個金屬層的電阻比其他層的電阻低得多。而這也意味著對于布局工具來說,決定哪些電線進入更高層,哪些電線仍留在較低層會越來越成問題。最受影響的,當然是加了緩沖的長線網。這就是為什么緩沖器面積會有這樣顯著的增長,而與長線網相關聯的時序會變差。

布局規劃階段(頂部)與應用系數后布局階段(底部)的綜合單元密度比較 (圖3)

我們發現,越來越多的電阻提供更好的面積相關性和時序相關性。不同設計用于實現良好相關性的因素各不相同。如上圖所示,將系數應用于阻力后,綜合與布局之間的相關性顯著改善。我們將綜合面積(頂部)與布局面積(底部)再次進行了比較。從布局圖像的橙色區域可以看出,仍有相當數量的高利用率負載,但比以前少得多。在這個示例中,準確度達到了5%左右,這是相當合理的,而且會實現良好、高效的工作流程。

把結果投入應用

我們已經看到,在先進工藝中,電阻對時序和面積有著巨大的影響。雖然從理論上來說物理綜合工具擁有關于布局的所有必要信息,但在實踐中它們仍必須非常小心地與實際布局數據關聯。這個過程可能比較耗時,但好處顯然超過了成本。在一天工作結束時,最好的做法是保持設計流程各步驟之間有一個可靠的相關性,從而獲得快速、靈活的設計,并且從一開始就對最終目標有一個明確的認識。

-

集成電路

+關注

關注

5426文章

12089瀏覽量

368704 -

后端設計

+關注

關注

0文章

14瀏覽量

8730

發布評論請先 登錄

評論