舵機(jī)

一個(gè)常見(jiàn)的舵機(jī)有三個(gè)連接線(xiàn)。

黑色:電源地

紅色:電源(5伏直流)

白色:控制引腳(PWM)

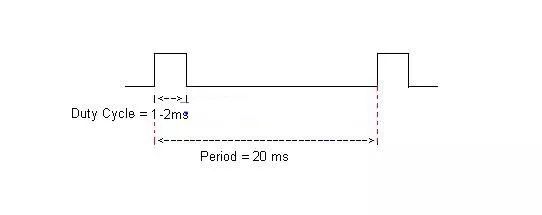

PWM控制舵機(jī)位置。伺服系統(tǒng)每20毫秒要有一個(gè)脈沖,以便獲得正確的角度信息。脈沖寬度決定了舵機(jī)的角度運(yùn)動(dòng)范圍。也就是說(shuō),我們可以通過(guò)發(fā)送1毫秒脈沖設(shè)置舵機(jī)到一端位置,發(fā)送2毫秒脈沖將其設(shè)置到另一個(gè)位置。

控制波形

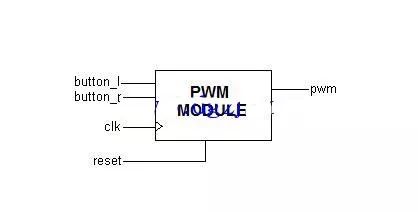

我們?cè)O(shè)計(jì)一個(gè)四個(gè)輸入,一個(gè)輸出的模塊,如下圖所示

控制模塊

reset:復(fù)位信號(hào)

button_l:用于PWM占空比的增加

button_r:用于PWM占空比的減小

Pwm:輸出信號(hào)驅(qū)動(dòng)舵機(jī)。

首先,應(yīng)該生成具有20毫秒周期的PWM信號(hào),由于使用50MHz的時(shí)鐘產(chǎn)生PWM,為了產(chǎn)生20ms信號(hào),我們將定義一個(gè)名為counter的變量和一個(gè)名為upper的常數(shù),它表示計(jì)數(shù)上邊界。

Upper boundary : 20ms/20ns = 1000 000

constant upper :integer:=1000000;

………………………..

process(clk,reset)

begin

if reset = '1' then

pwm_reg

counter

duty_cycle

elsif clk='1' and clk'event then

pwm_reg

counter

duty_cycle

end if;

end process;

counter_next

控制信號(hào)占空比的值應(yīng)是1毫秒至2毫秒之間。我們將定義兩個(gè)常數(shù)命名dcycle_max和dcycle_min說(shuō)明上下邊界。

dcycle_max:顯示脈沖寬度的最大值。

(2ms/clock period=2 ms/ 20 ns=100000)

dcycle_min:顯示脈沖寬度的最小值。

(1ms/clock period=1 ms/ 20 ns=50000)

脈寬(占空比)在每個(gè)PWM周期中改變,因此我們定義了一個(gè)稱(chēng)為tick的變量。當(dāng)tick為“1”時(shí),占空比將發(fā)生變化。

signal tick : std_logic;

tick

定義了一個(gè)稱(chēng)為duty_in的常數(shù),用于改變占空比。

VHDL代碼

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity servo_pwm is

Port ( clk : in STD_LOGIC;

reset : in STD_LOGIC;

button_l : in STD_LOGIC;

button_r : in STD_LOGIC;

pwm : out STD_LOGIC);

end servo_pwm;

architecture Behavioral of servo_pwm is

constant period:integer:=1000000;

constant dcycle_max:integer:=100000;

constant dcycle_min:integer:=50000;

constant duty_in:integer:=200;

signal pwm_reg,pwm_next:std_logic;

signal duty_cycle,duty_cycle_next:integer:=0;

signal counter,counter_next:integer:=0;

signal tick:std_logic;

begin

process(clk,reset)

begin

if reset = '1' then

pwm_reg

counter

duty_cycle

elsif clk='1' and clk'event then

pwm_reg

counter

duty_cycle

end if;

end process;

counter_next

tick

process(button_l,button_r,tick,duty_cycle)

begin

duty_cycle_next

if tick='1' then

if button_l ='1' and duty_cycle >dcycle_min then

duty_cycle_next

elsif button_r ='1' and duty_cycle

duty_cycle_next

end if;

end if;

end process;

pwm

pwm_next

end Behavioral;

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603010 -

控制模塊

+關(guān)注

關(guān)注

2文章

130瀏覽量

18852 -

舵機(jī)

+關(guān)注

關(guān)注

17文章

268瀏覽量

41014

原文標(biāo)題:FPGA控制舵機(jī)程序

文章出處:【微信號(hào):changxuemcu,微信公眾號(hào):暢學(xué)單片機(jī)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

舵機(jī)技術(shù)新突破,無(wú)線(xiàn)控制更自由!

舵機(jī)技術(shù)深度解析,讓機(jī)器人更智能!

FPGA加速深度學(xué)習(xí)模型的案例

FPGA做深度學(xué)習(xí)能走多遠(yuǎn)?

舵機(jī)在無(wú)人機(jī)中的應(yīng)用

探索智能動(dòng)力之源:揭秘舵機(jī)的無(wú)限可能

ESP32控制舵機(jī)的正反轉(zhuǎn)原理是什么

舵機(jī)是什么?舵機(jī)內(nèi)部結(jié)構(gòu)解析

舵機(jī)是否屬于伺服電機(jī)

機(jī)器人舵機(jī):關(guān)鍵要素解析與選擇指南

舵機(jī)三根線(xiàn)分別是什么?一文解析舵機(jī)各線(xiàn)纜對(duì)應(yīng)關(guān)系

如何使用單片機(jī)控制舵機(jī)的轉(zhuǎn)動(dòng)

舵機(jī)三根線(xiàn)分別是什么?一文解析舵機(jī)各線(xiàn)纜對(duì)應(yīng)關(guān)系

深度解析基于FPGA控制的舵機(jī)程序

深度解析基于FPGA控制的舵機(jī)程序

評(píng)論