引言:本文從I2C協(xié)議的概述開始,描述協(xié)議的歷史、不同速度模式、物理層和數(shù)據(jù)幀結(jié)構(gòu),最后介紹I2C混合電壓系統(tǒng)中電平兼容性以及上拉電阻大小計算。

1.概述

1.1 I2C協(xié)議歷史

I2C,通常被稱為I'two'C,代表集成電路間協(xié)議。I2C由飛利浦半導(dǎo)體公司(現(xiàn)為恩智浦半導(dǎo)體公司)于1982年開發(fā),是一種低速通信協(xié)議,用于連接微控制器和處理器等控制器設(shè)備與數(shù)據(jù)轉(zhuǎn)換器和其他外圍設(shè)備等目標(biāo)設(shè)備。

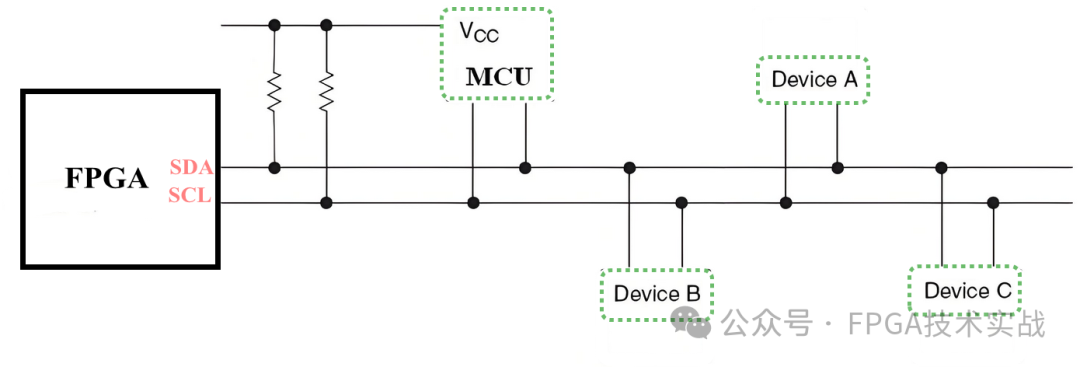

I2C是使用串行數(shù)據(jù)線(SDA)和串行時鐘線(SCL)的雙線串行通信協(xié)議。該協(xié)議支持通信總線上的多個目標(biāo)設(shè)備,還可以支持發(fā)送和接收命令和數(shù)據(jù)的多個控制器。

圖1:I2C總線典型應(yīng)用

由于該協(xié)議只需要兩條通信線路,I2C在很多工程中有廣泛的應(yīng)用,如數(shù)據(jù)采集領(lǐng)域的串行ADC、DAC、攝像頭配置,X射線管配置等。除此之外,由于I2C協(xié)議占用引腳特別少,硬件實現(xiàn)簡單,可擴(kuò)展型強(qiáng),現(xiàn)在被廣泛地使用在系統(tǒng)內(nèi)多個集成電路(IC)間的通信。

1.2 I2C的速度模式

I2C有5種速度模式,從標(biāo)準(zhǔn)模式(Sm),快速模式(Fm),快速模式+(Fm+)模式。這三種模式相對相似,使用相同的通信結(jié)構(gòu)。然而,所有模式都具有不同的時序規(guī)范,并且設(shè)備中I2C的硬件實現(xiàn)方式不同以適應(yīng)不同的速度。

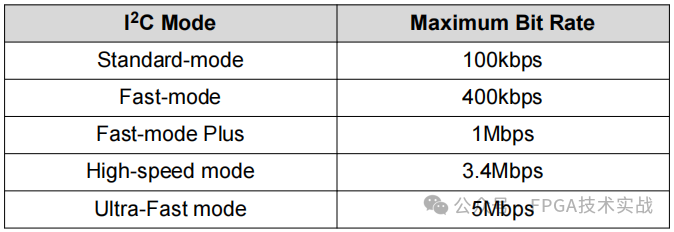

I2C還具有用于更高數(shù)據(jù)速率的另外兩種模式。高速模式(Hs模式)和超快模式(UFm)是最快的操作模式。表1-1顯示了不同的I2C模式及其各自的數(shù)據(jù)速率。

表1:不同I2C模式的最大傳輸速率

2. 物理層

2.12線通信

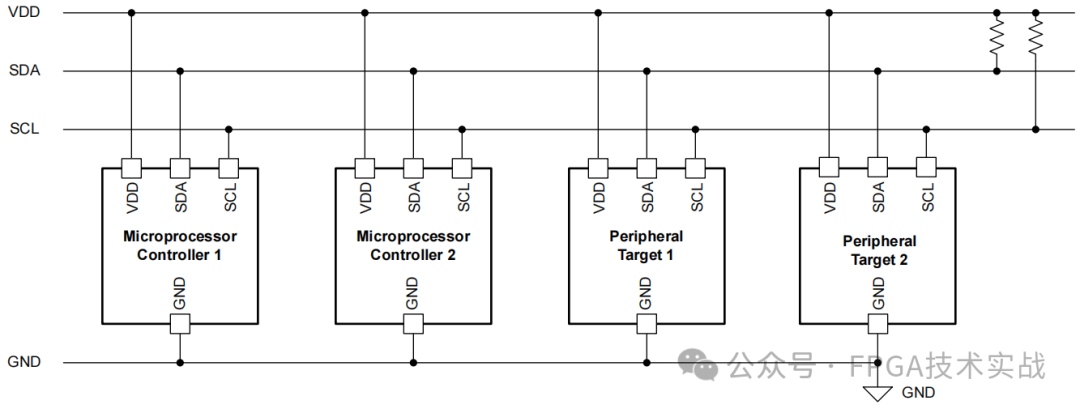

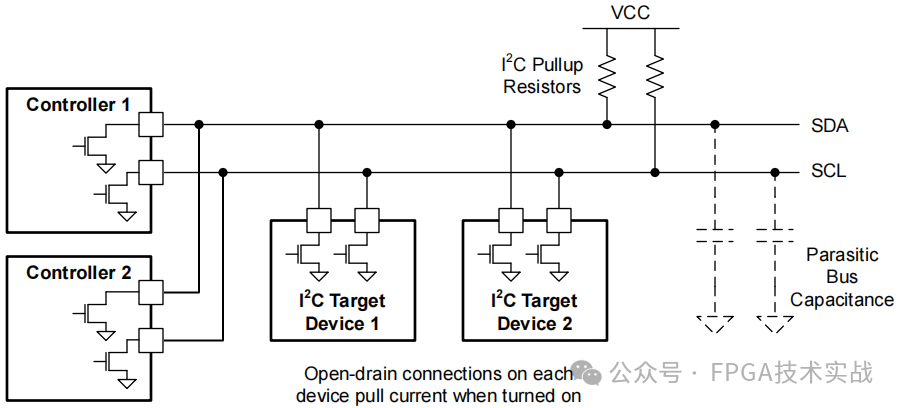

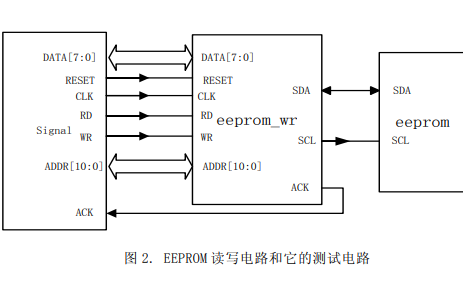

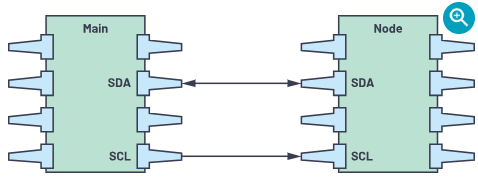

I2C系統(tǒng)的特點是為總線上的所有設(shè)備提供兩條共享通信線路。這兩條線路用于雙向半雙工通信。I2C允許多個控制器和多個目標(biāo)設(shè)備。這兩條線路上都需要上拉電阻器。圖2顯示了I2C物理層的典型實現(xiàn)。

圖2:典型的I2C實現(xiàn)

第一條線是SCL,它是主要由控制器設(shè)備控制的串行時鐘。SCL用于將數(shù)據(jù)同步地時鐘輸入或輸出目標(biāo)設(shè)備。

第二條線是SDA,它是串行數(shù)據(jù)線。SDA用于將數(shù)據(jù)傳輸?shù)侥繕?biāo)設(shè)備或從目標(biāo)設(shè)備傳輸數(shù)據(jù)。

I2C控制器設(shè)備啟動和停止通信,這消除了總線爭用的潛在問題。通過總線上的唯一地址發(fā)送與目標(biāo)設(shè)備的通信。這允許I2C總線上的多個控制器和多個目標(biāo)設(shè)備。

SDA和SCL線路具有到總線上所有設(shè)備的開漏連接。這需要一個上拉電阻到一個公共電壓源。

2.2 漏極開路連接

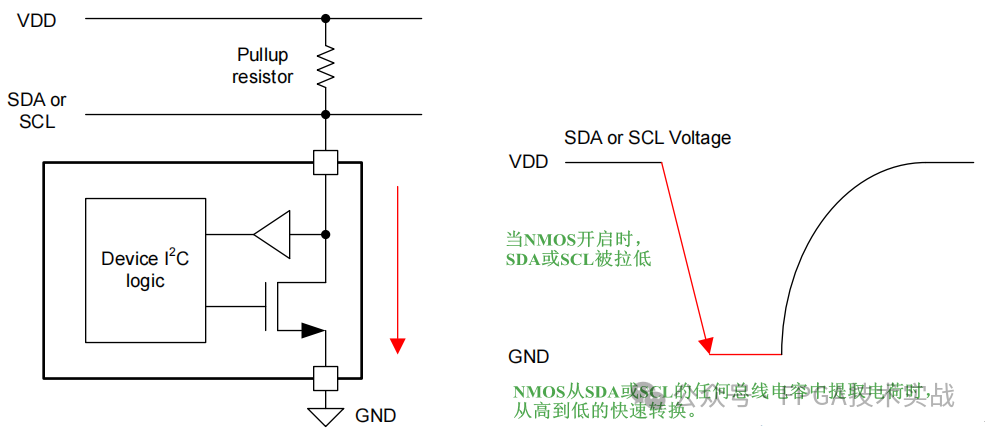

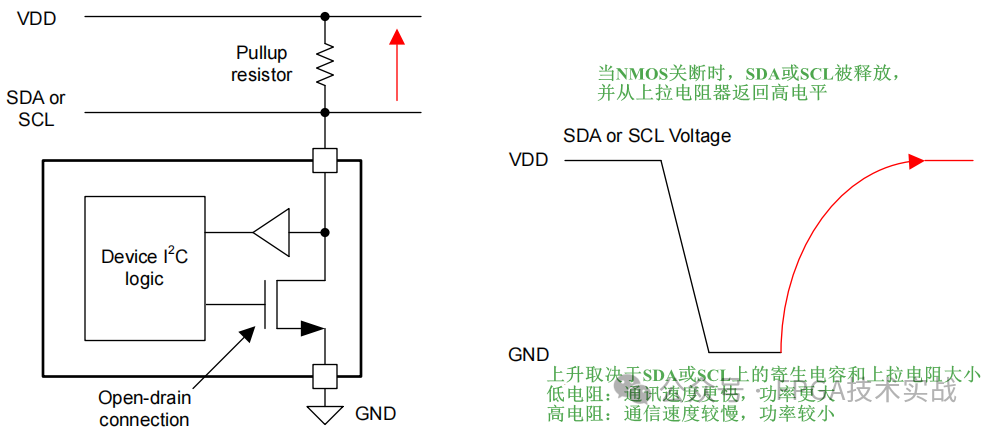

漏極開路連接用于SDA和SCL線路,并連接到NMOS晶體管。該漏極開路連接控制I2C通信線路并將線路拉低或釋放線路高。漏極開路指的是NMOS關(guān)閉時的NMOS總線連接。圖3顯示了NMOS打開時的漏極開路連接。

圖3:當(dāng)NMOS導(dǎo)通時,開路漏極連接將線路拉低

要設(shè)置SDA或SCL線的電壓電平,需將NMOS設(shè)置為打開或關(guān)閉。當(dāng)NMOS打開時,設(shè)備通過電阻器將電流拉到地。這將打開的NMOS拉低。通常,當(dāng)NMOS在SDA或SCL上下拉時,I2C從高到低的轉(zhuǎn)變是快速轉(zhuǎn)變。轉(zhuǎn)變的速度由NMOS驅(qū)動強(qiáng)度和SDA或SCL上的任何總線電容決定。

當(dāng)NMOS關(guān)閉時,器件停止拉電流,上拉電阻器將SDA或SCL線拉至VDD。圖2-3顯示了NMOS關(guān)閉時漏極開路。上拉電阻器將線路拉高。開路漏極線的轉(zhuǎn)變較慢,因為線是相對于總線電容上拉的,并且不是主動驅(qū)動的。

圖4:NMOS關(guān)斷時上拉電阻器將線路拉高

通過控制該漏極開路連接,SDA和SCL都可以設(shè)置為高電平和低電平,從而實現(xiàn)I2C通信。

由于I2C通信線路上的電容,SDA和SCL線路以指數(shù)穩(wěn)定RC時間常數(shù)放電,這取決于上拉電阻器的大小和I2C總線上的電容。更高的電容限制了I2C通信的速度、設(shè)備的數(shù)量以及總線上設(shè)備之間的物理距離。較小的上拉電阻器具有更快的上升時間,但需要更多的功率用于通信。較大的上拉電阻器具有較慢的上升時間,導(dǎo)致較慢的通信,但需要較少的功率。

2.3 非破壞性總線競爭

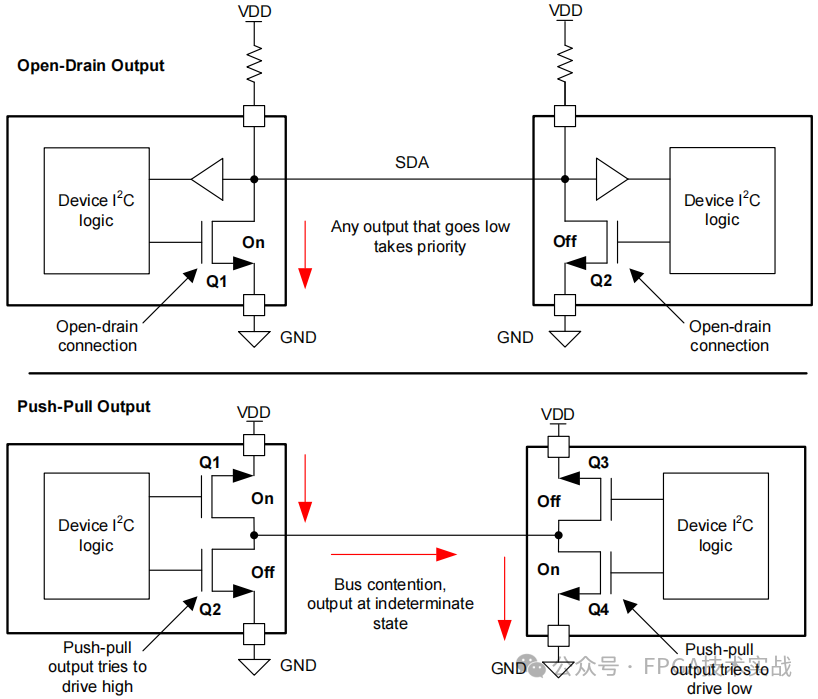

使用開放漏極的I2C的好處之一是總線爭用不會使總線進(jìn)入破壞狀態(tài)。通過開漏輸出,許多設(shè)備可以連接在一起,而不會發(fā)生破壞性爭用。對于該連接上的任何輸出,如果任何輸出將線路拉低,則線路為低。這種連接被稱為有線AND連接。當(dāng)連接在一起時,輸出是所有輸出的邏輯AND。

圖5:推挽式與開漏輸出的比較

如果輸出是推挽式的,那么在沒有破壞狀態(tài)的可能性的情況下,輸出就不能連接在一起。推挽輸出(通常用于SPI通信)具有互補(bǔ)的NMOS和PMOS晶體管,它們驅(qū)動輸出為高或低。圖5顯示了在爭用中開漏和推挽輸出之間的比較。

采用開放式漏極連接,任何設(shè)備都可以隨時將連接拉低。每當(dāng)任何設(shè)備將線路拉低時,線路都會顯示為低電平,但不會顯示為破壞性爭用。

在推挽輸出中,輸出也被連接在一起。如果總線上有兩個設(shè)備處于活動狀態(tài),并且一個輸出為高,另一個輸出低,則此總線爭用具有未確定的狀態(tài),可能在中間供電點處解決。此外,一個器件具有NMOS導(dǎo)通電流,而另一個器件則具有PMOS導(dǎo)通電流。這些器件通過非常低的阻抗路徑將電流從VDD供應(yīng)到GND,傳導(dǎo)晶體管允許的盡可能多的電流。這種爭用的結(jié)果可能是大量的電流,可能會損壞設(shè)備。

3. I2C協(xié)議

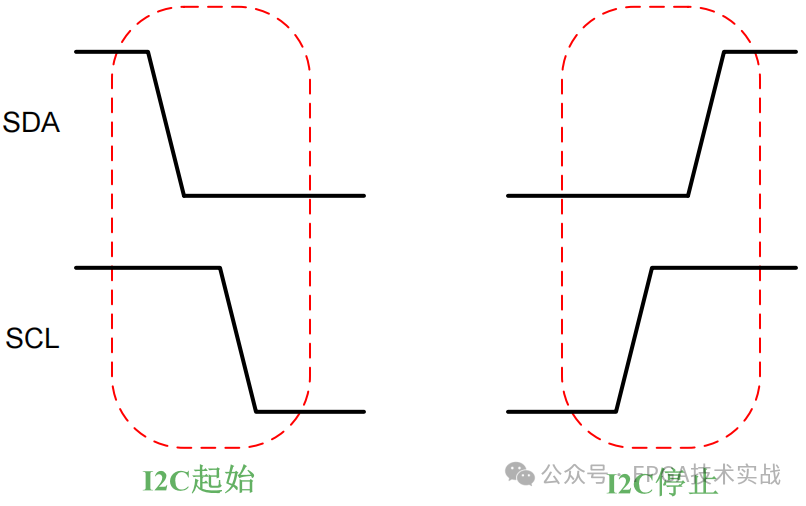

3.1 I2C起始和停止協(xié)議

I2C通信是在I2C啟動條件下從控制器設(shè)備啟動的。如果總線開路,I2C控制器通過發(fā)送I2C START來請求總線進(jìn)行通信。為此,控制器設(shè)備首先將SDA拉低,然后將SCL拉低。此序列表示控制器設(shè)備正在請求I2C總線進(jìn)行通信,從而迫使總線上的其他控制器設(shè)備保持其通信。

圖6:I2C啟動和停止協(xié)議

當(dāng)控制器設(shè)備已經(jīng)完成通信時,SCL釋放高電平,然后SDA釋放高電平。這表示I2C停機(jī)狀態(tài)。這釋放了總線以允許其他控制器通信或允許同一控制器與另一設(shè)備通信。圖6顯示了I2C啟動和停止的協(xié)議。

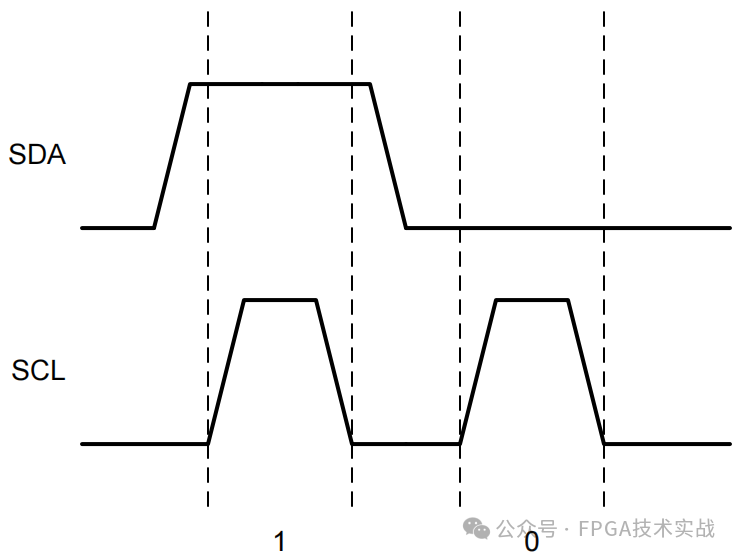

3.2 邏輯“1”和邏輯“0”

I2C使用1和0的序列進(jìn)行串行通信。SDA用于數(shù)據(jù)位,而SCL是對位序列進(jìn)行計時的串行時鐘。當(dāng)SDA釋放線路時,發(fā)送一個邏輯1,允許上拉電阻器將線路拉至高電平。當(dāng)SDA在線路上下拉時,將發(fā)送一個邏輯零,在接地附近設(shè)置一個低電平。圖7顯示了I2C通信的數(shù)字1和0的表示。

圖7:I2C數(shù)據(jù)邏輯“1”和邏輯“0”

當(dāng)SCL被脈沖化時,1和0被接收。對于有效位,SDA不會在該位的SCK的上升沿和下降沿之間變化。SDA在SCL的上升沿與下降沿之間的變化可以解釋為I2C總線上的START或STOP條件。

3.3 I2C通信幀格式

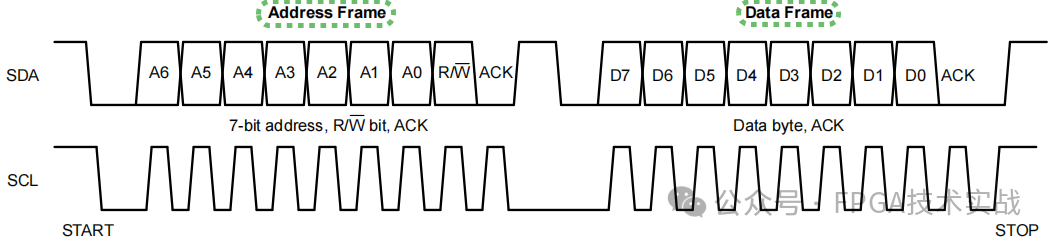

I2C協(xié)議被分解為多個幀。通信開始于控制器設(shè)備在START之后發(fā)送地址幀。地址幀后面跟著一個或多個數(shù)據(jù)幀,每個數(shù)據(jù)幀由一個字節(jié)組成。每個幀還具有一個確認(rèn)比特(ACK),以提醒控制器目標(biāo)設(shè)備或控制器設(shè)備已經(jīng)接收到通信。圖8顯示了兩個I2C通信幀的示意圖。

圖8:I2C地址和數(shù)據(jù)幀

在地址幀的開始,控制器設(shè)備啟動START條件。控制器設(shè)備首先將SDA拉低,然后將SCL拉低用于START。這允許控制器設(shè)備在沒有來自總線上的其他控制器設(shè)備的爭用的情況下請求總線。每個I2C目標(biāo)設(shè)備都具有相關(guān)聯(lián)的I2C地址。當(dāng)開始與特定目標(biāo)設(shè)備通信時,控制器使用目標(biāo)設(shè)備地址在I2C幀中發(fā)送或接收數(shù)據(jù)。I2C地址由I2C總線上的7個位和R/Wn組成,每個設(shè)備在總線上都有一個唯一的地址。

7位地址意味著128個唯一地址。然而,有幾個保留的I2C地址限制了可能的設(shè)備的數(shù)量。發(fā)送地址時,SDA作為數(shù)據(jù),SCL作為串行時鐘。

該幀地址后面的第8位是讀寫(R/W)位。如果該位為1,則控制器要求從目標(biāo)設(shè)備讀取數(shù)據(jù)。如果該位為0,則控制器要求將數(shù)據(jù)寫入目標(biāo)設(shè)備。

在任何通信字節(jié)之后,額外的第9位用于驗證通信是否成功。在地址字節(jié)通信結(jié)束時,目標(biāo)設(shè)備在SCL脈沖期間下拉SDA,以向控制器指示地址已被接收。這被稱為確認(rèn)(ACK)比特。如果該比特為高,則沒有目標(biāo)設(shè)備接收到該地址,并且通信不成功。如果比特是高的,這被稱為NACK,并且沒有ACK。

地址幀后面跟著一個或多個數(shù)據(jù)幀。這些幀一次發(fā)送一個字節(jié)。在每個數(shù)據(jù)字節(jié)被傳輸之后,會有另一個ACK。如果數(shù)據(jù)字節(jié)是對設(shè)備的寫入,則目標(biāo)設(shè)備將SDA拉低以確認(rèn)傳輸。如果數(shù)據(jù)字節(jié)是從設(shè)備讀取的,則控制器將SDA拉低以確認(rèn)數(shù)據(jù)已被接收。ACK是一個有用的調(diào)試工具。該位的缺失可以指示目標(biāo)外圍設(shè)備沒有接收到用于通信的適當(dāng)I2C地址,或者控制器外圍設(shè)備沒有收到期望的數(shù)據(jù)。

通信完成后,控制器發(fā)出I2C STOP條件。首先釋放SCL,然后釋放SDA。控制器使用STOP指示通信已完成,I2C總線已釋放。

這是控制器設(shè)備和目標(biāo)設(shè)備之間的任何I2C通信的基本協(xié)議。通信可以由多個字節(jié)的數(shù)據(jù)組成。在目標(biāo)設(shè)備具有多個數(shù)據(jù)和配置寄存器的某些情況下,從設(shè)備的讀取可以從對設(shè)備的寫入開始,以指示要讀取哪個寄存器。

4. I2C高級議題

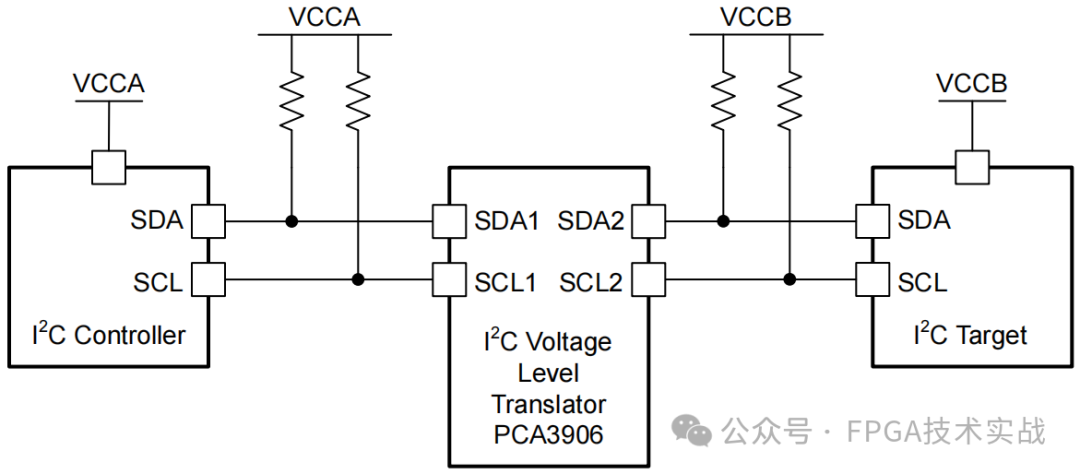

4.1 電壓電平轉(zhuǎn)換

設(shè)計大型系統(tǒng)的一個常見問題是系統(tǒng)內(nèi)不同電壓電平的混合。這些不同的電壓可以為不同的I2C控制器和目標(biāo)設(shè)備供電。電源中不匹配的電壓可能會中斷通信,甚至損壞設(shè)備。

圖9:PCA3906 I2C電壓電平轉(zhuǎn)換器

對于不匹配的電源電壓,最好的選擇是使用特殊設(shè)備橋接兩個電源電壓。圖9顯示了使用I2C電壓電平轉(zhuǎn)換器橋接兩個不同電源電壓之間通信的示例。有兩組上拉,每個電壓電平一組。作為一個通用的電壓轉(zhuǎn)換器,PCA9306允許不同電源電平之間的通信。

4.2 上拉電阻大小計算

為了設(shè)計系統(tǒng),使總線速度足夠快,以滿足協(xié)議總線速度,本節(jié)介紹如何計算上拉電阻的值。

對于SDA和SCL的漏極開路連接,從這些線路從高到低以及從低到高的轉(zhuǎn)換取決于器件漏極開路的電流吸收、總線電容和上拉電阻值。基于這些不同的參數(shù),可以計算I2C總線速度的最小和最大電阻。

圖10:影響上拉電阻大小的因素

推薦的正常上拉電阻為1kΩ至10kΩ。電阻越高,I2C通信越慢。由于電阻較低,I2C通信需要更多的功率。基于幾個不同的參數(shù),可以計算I2C總線速度的最小和最大電阻。

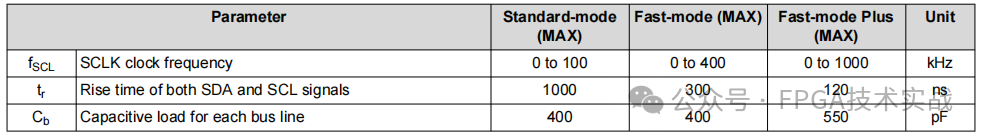

表2列出了I2C總線的比特率、總線的最大上升時間以及總線上的最大電容負(fù)載。所有這些參數(shù)都用于確定最小和最大上拉電阻值。

表2:I2C總線參數(shù)特性

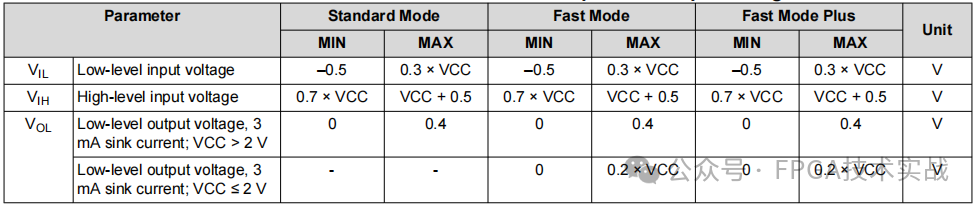

除了這些參數(shù)外,還考慮了I2C輸入和輸出電壓的最小值和最大值。表3描述了這些電壓。

表3:I2C總線參數(shù)特性

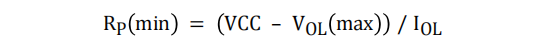

(1)最小上拉電阻計算

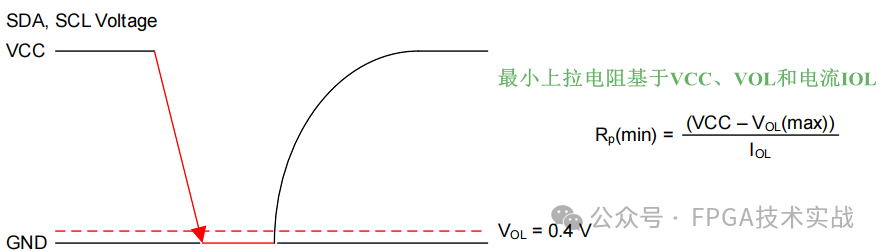

圖11顯示了I2C總線的漏極開路連接以及SDA或SCL的輸出波形。SDA和SCL總線從設(shè)備的電流拉低轉(zhuǎn)換為低電平。

圖11:基于下拉電流的最小上拉電阻

當(dāng)設(shè)備釋放SDA或SCL時,總線連接到VCC電壓。當(dāng)激活時,器件漏極將總線輸出拉到接近接地的位置。輸出必須下降到輸出低電平電壓VOL。該設(shè)備用電流IOL將總線拉低。VOL和IOL(3mA電流匯點)如表3所示。根據(jù)該電流,計算上拉所需的最小電阻。如果電阻較小,則輸出電流不能將總線的輸出電壓拉低到足以被識別為數(shù)字低。這如下公式所示。

求出最小上拉電阻,從3.3 V的電源電壓中減去0.4 V的輸出低電壓。然后除以3 mA的總線所拉的電流。這導(dǎo)致最小電阻為967Ω。

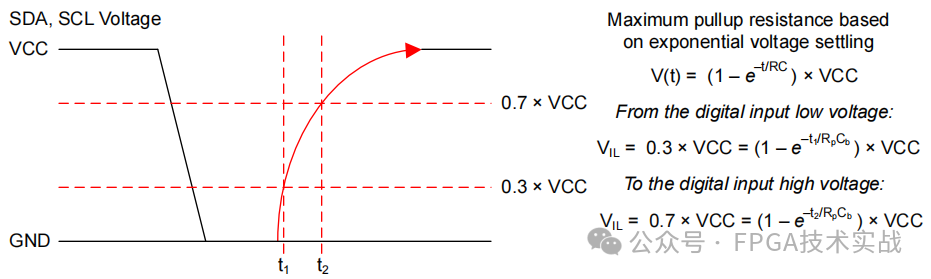

(2)最大上拉電阻計算

漏極開路連接釋放輸出電流后,上拉電阻將總線連接拉高。總線輸出波形具有指數(shù)穩(wěn)定。當(dāng)電阻器將電壓從地上拉時,電壓穩(wěn)定時間基于總線電容(CB)。由于I2C標(biāo)準(zhǔn)上升時間規(guī)范,最大上拉電阻受到總線電容的限制。對于更高的電阻,上拉輸出上升得太慢,并且沒有足夠快地達(dá)到邏輯高位。

圖12:最大上拉電阻計算

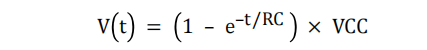

隨時間的指數(shù)方程如下公式所示:

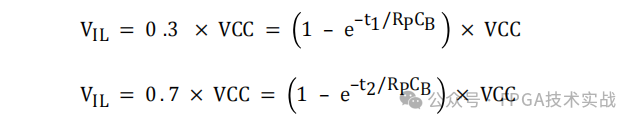

上升時間基于從電源電壓的0.3倍的數(shù)字輸入低電壓(VIL)到電源電壓的0.7倍的數(shù)字輸出高電壓(VIH)的轉(zhuǎn)變。上升時間如表2所示,而VIL和VIH如表3所示。

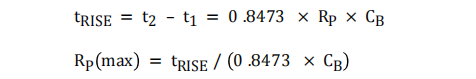

根據(jù)上述方程,可以根據(jù)最大上拉電阻和總線電容來求解上升時間。在這個例子中,計算是針對400pF的總線電容(針對最大總線電容)和3.3V的電源電壓。根據(jù)上升時間,然后求解最大上拉電阻。

上升時間取決于I2C模式。對于此示例,可以使用標(biāo)準(zhǔn)模式。取1000ns的上升時間,除以0.8473乘以400pF的量。這給出了2.95kΩ的最大電阻。

最小電阻為967Ω,最大電阻為2.95kΩ,這些值的電阻范圍似乎很窄。然而,這個小范圍是因為上拉電阻器的大小是在最大標(biāo)準(zhǔn)模式總線電容為400pF的情況下計算的。總線電容量異常大,尤其是對于板上的寄生電容而言。如果設(shè)計具有較低的總線電容(很可能),則可以增加最大電阻,從而減少I2C總線上的功耗。

5. 小結(jié)

I2C是一種常見的通信協(xié)議,本文對I2C協(xié)議的歷史、速度模式、物理層、數(shù)據(jù)幀結(jié)構(gòu)以及混合電壓系統(tǒng)中電平兼容性以及上拉電阻大小計算均進(jìn)行了詳細(xì)介紹。

本文轉(zhuǎn)載自FPGA技術(shù)實戰(zhàn)公眾號

-

微控制器

+關(guān)注

關(guān)注

48文章

7776瀏覽量

153051 -

集成電路

+關(guān)注

關(guān)注

5411文章

11802瀏覽量

365532 -

接口

+關(guān)注

關(guān)注

33文章

8832瀏覽量

152719 -

I2C協(xié)議

+關(guān)注

關(guān)注

0文章

26瀏覽量

8652

原文標(biāo)題:FPGA入門基礎(chǔ)之I2C接口設(shè)計(一)

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

I2C總線協(xié)議及其應(yīng)用

I2C最新協(xié)議標(biāo)準(zhǔn)

I2C通信協(xié)議應(yīng)該如何學(xué)習(xí)

I2C系列的合集,可以系統(tǒng)學(xué)習(xí)I2C協(xié)議

I2C基礎(chǔ)知識入門簡單介紹

STM32學(xué)習(xí)之I2C協(xié)議(讀寫EEPROM)

硬件I2C與模擬I2C

一文看懂I2C協(xié)議

I2C通信協(xié)議:了解I2C Primer、 PMBus和SMBus

使用I2C協(xié)議點亮OLED

評論