單個芯片性能提升的有效途徑

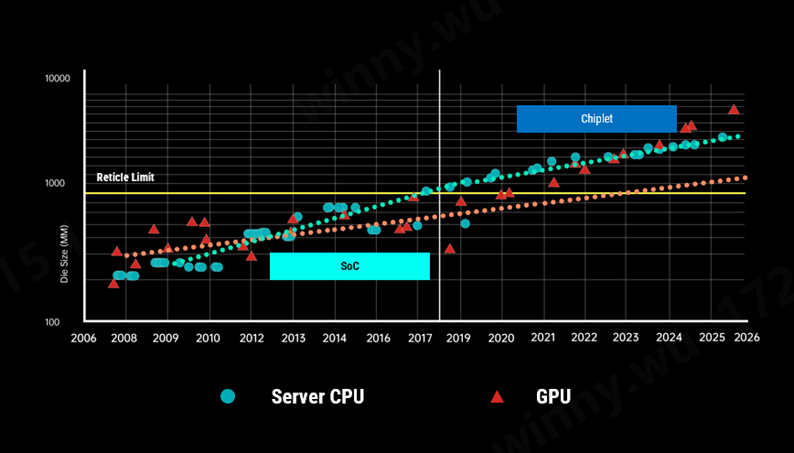

隨著半導(dǎo)體制程不斷逼近物理極限,越來越多的芯片廠商為了提升芯片性能和效率開始使用Chiplet技術(shù),將多個滿足特定功能的芯粒單元通過Die-to-Die互聯(lián)技術(shù)與底層基礎(chǔ)芯片封裝在一起,形成一個系統(tǒng)級芯片。

在單個芯片內(nèi)部,基于Chiplet架構(gòu)的IO Die、Die-to-Die互聯(lián)技術(shù)是增強(qiáng)單個芯片性能和性價比的關(guān)鍵途徑。片內(nèi)的高速互聯(lián)可以大大降低數(shù)據(jù)傳輸?shù)难舆t和功耗。通過高速的內(nèi)部互聯(lián),不同的功能模塊可以快速共享數(shù)據(jù),優(yōu)化內(nèi)存訪問和計算資源的分配,提高整體能效比。簡而言之,Chiplet架構(gòu)下的內(nèi)部高速互聯(lián),為芯片算力的提升開辟了新的可能。

AMD EPYC Zen 5系列Chiplet案例

(Source:AMD 5th Gen EPYC 處理器白皮書)

近期才發(fā)布的AMD 代號為“Turin” Zen 5 架構(gòu)的 EPYC 服務(wù)器處理器,使用臺積電3nm/4nm工藝制造,主頻高達(dá)5Ghz。Turin 有兩種版本:一種配備Zen 5 內(nèi)核(支持多達(dá)128內(nèi)核、256線程),另一種配備 Zen 5c內(nèi)核(支持多達(dá)192內(nèi)核,384線程)。AMD繼續(xù)沿用了Central IOD(IO Die)的設(shè)計架構(gòu),保持了上一代6nm的工藝。

(Source:AMD 5th Gen EPYC 處理器白皮書)

上圖所示,AMD運(yùn)用Chiplet技術(shù)將CPU與IO Die創(chuàng)新路徑解耦,這些芯片可以按照自己的制程進(jìn)行開發(fā)及演進(jìn)。通過模塊化方法,可以靈活擴(kuò)充/搭配CCD (CPU Die) 和IO Die,以創(chuàng)建滿足工作負(fù)載需求的專業(yè)處理器。(按需配置低配版8內(nèi)核到高配版192內(nèi)核的處理器)。

隨著CPU性能的提升,IO Die 也在不斷發(fā)展以適應(yīng)需求,更多的內(nèi)核需要更多的I/O帶寬從而支持12個DDR5-6000內(nèi)存控制器、PCIe Gen 5 I/O以及AMD Infinity Fabric互連。

隨著系統(tǒng)規(guī)模的不斷擴(kuò)大,我們需要將眾多不同的小單元(如計算單元、存儲單元、功能單元等)整合成更大規(guī)模的系統(tǒng)。為此,迫切需要一種從芯片內(nèi)部到整個系統(tǒng)層面的統(tǒng)一互聯(lián)架構(gòu)。雖然國際頂尖廠商已經(jīng)推出了各自的解決方案,但行業(yè)的發(fā)展趨勢表明,廠商之間的合作已成為主流。因此,實(shí)現(xiàn)不同廠商間的互操作性變得至關(guān)重要。這就要求我們構(gòu)建一個基于第三方產(chǎn)品的統(tǒng)一互聯(lián)架構(gòu),以及開放的標(biāo)準(zhǔn)和生態(tài)系統(tǒng)。通過這種分工協(xié)作的模式,我們可以打造一個開放且繁榮的生態(tài)系統(tǒng),使得各廠商能夠根據(jù)自己的專長(如計算、軟件開發(fā)、接口技術(shù)等)進(jìn)行有效合作,共同推動行業(yè)的進(jìn)步。

Die-to-Die片內(nèi)互聯(lián):UCIe互聯(lián)標(biāo)準(zhǔn)

Die-to-Die 互聯(lián)是Chiplet架構(gòu)的核心基礎(chǔ),它為芯片內(nèi)部不同Die之間的緊密協(xié)作提供了傳輸?shù)?a target="_blank">接口。Universal Chiplet Interconnect Express (UCIe) 是一種開放的行業(yè)互聯(lián)標(biāo)準(zhǔn),可在 Chiplet 之間提供高帶寬、低延遲、節(jié)能且經(jīng)濟(jì)高效的封裝內(nèi)連接。

自2012年成立以來,UCIe 的既定目標(biāo)是為Chiplet建立一個開放且無處不在的生態(tài)系統(tǒng)。無論這意味著簡單地將某些物理方面標(biāo)準(zhǔn)化以簡化制造,還是實(shí)現(xiàn)真正的混合匹配設(shè)置。在這樣的生態(tài)系統(tǒng)中,客戶可以自由地從多家芯片制造商那里挑選使用Chiplet構(gòu)建的芯片模塊,而這些都需要一個強(qiáng)大的基礎(chǔ)標(biāo)準(zhǔn)來支撐。

UCIe技術(shù)被用于連接多個芯片Die、內(nèi)存控制器和其他計算資源,形成一個高度集成的系統(tǒng)。這種集成方式允許不同的計算單元之間通過高速的數(shù)據(jù)通道進(jìn)行通信,從而提高整體系統(tǒng)的處理能力和效率。此外,使用UCIe技術(shù)還可以實(shí)現(xiàn)動態(tài)功耗管理,通過在不同計算單元之間動態(tài)調(diào)整功率分配,以優(yōu)化系統(tǒng)的能效比。

UCIe 1.1 于2023年8月發(fā)布覆蓋涵蓋了芯片到芯片之間的I/O 物理層、協(xié)議和軟件堆棧等規(guī)范。之后時隔1年,UCIe 2.0規(guī)范正式發(fā)布。UCIe 2.0規(guī)范引入了對可管理性標(biāo)準(zhǔn)化系統(tǒng)架構(gòu)的支持,并全面解決了系統(tǒng)級封裝(SiP)生命周期中跨多個芯粒的可測試性、可管理性和調(diào)試(DFx)的設(shè)計難題。

UCIE 2.0升級要點(diǎn)

1全面支持具有多個Chiplets的任何系統(tǒng)級封裝 (SiP) 結(jié)構(gòu)的可管理性、調(diào)試和測試。

2支持3D封裝,顯著提升帶寬密度和功率效率。

3改進(jìn)的系統(tǒng)級解決方案,其可管理性被定義為chiplet堆棧的一部分。

4針對互操作性和合規(guī)性測試優(yōu)化的封裝設(shè)計。

5完全向后兼容 UCIe 1.1 和 UCIe 1.0。

關(guān)于我們

AI網(wǎng)絡(luò)全棧式互聯(lián)架構(gòu)產(chǎn)品及解決方案提供商

奇異摩爾,成立于2021年初,是一家行業(yè)領(lǐng)先的AI網(wǎng)絡(luò)全棧式互聯(lián)產(chǎn)品及解決方案提供商。公司依托于先進(jìn)的高性能RDMA 和Chiplet技術(shù),創(chuàng)新性地構(gòu)建了統(tǒng)一互聯(lián)架構(gòu)——Kiwi Fabric,專為超大規(guī)模AI計算平臺量身打造,以滿足其對高性能互聯(lián)的嚴(yán)苛需求。

我們的產(chǎn)品線豐富而全面,涵蓋了面向不同層次互聯(lián)需求的關(guān)鍵產(chǎn)品,如面向北向Scale out網(wǎng)絡(luò)的AI原生智能網(wǎng)卡、面向南向Scale up網(wǎng)絡(luò)的GPU片間互聯(lián)芯粒、以及面向芯片內(nèi)算力擴(kuò)展的2.5D/3D IO Die和UCIe Die2Die IP等。這些產(chǎn)品共同構(gòu)成了全鏈路互聯(lián)解決方案,為AI計算提供了堅實(shí)的支撐。

奇異摩爾的核心團(tuán)隊匯聚了來自全球半導(dǎo)體行業(yè)巨頭如NXP、Intel、Broadcom等公司的精英,他們憑借豐富的AI互聯(lián)產(chǎn)品研發(fā)和管理經(jīng)驗,致力于推動技術(shù)創(chuàng)新和業(yè)務(wù)發(fā)展。團(tuán)隊擁有超過50個高性能網(wǎng)絡(luò)及Chiplet量產(chǎn)項目的經(jīng)驗,為公司的產(chǎn)品和服務(wù)提供了強(qiáng)有力的技術(shù)保障。我們的使命是支持一個更具創(chuàng)造力的芯世界,愿景是讓計算變得簡單。奇異摩爾以創(chuàng)新為驅(qū)動力,技術(shù)探索新場景,生態(tài)構(gòu)建新的半導(dǎo)體格局,為高性能AI計算奠定穩(wěn)固的基石。

-

處理器

+關(guān)注

關(guān)注

68文章

19259瀏覽量

229651 -

芯片

+關(guān)注

關(guān)注

455文章

50714瀏覽量

423138 -

封裝

+關(guān)注

關(guān)注

126文章

7873瀏覽量

142893 -

chiplet

+關(guān)注

關(guān)注

6文章

431瀏覽量

12584

原文標(biāo)題:線上直播 | AIGC時代:邀您共探Chiplet互聯(lián)趨勢與Die-to-Die接口技術(shù)

文章出處:【微信號:奇異摩爾,微信公眾號:奇異摩爾】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

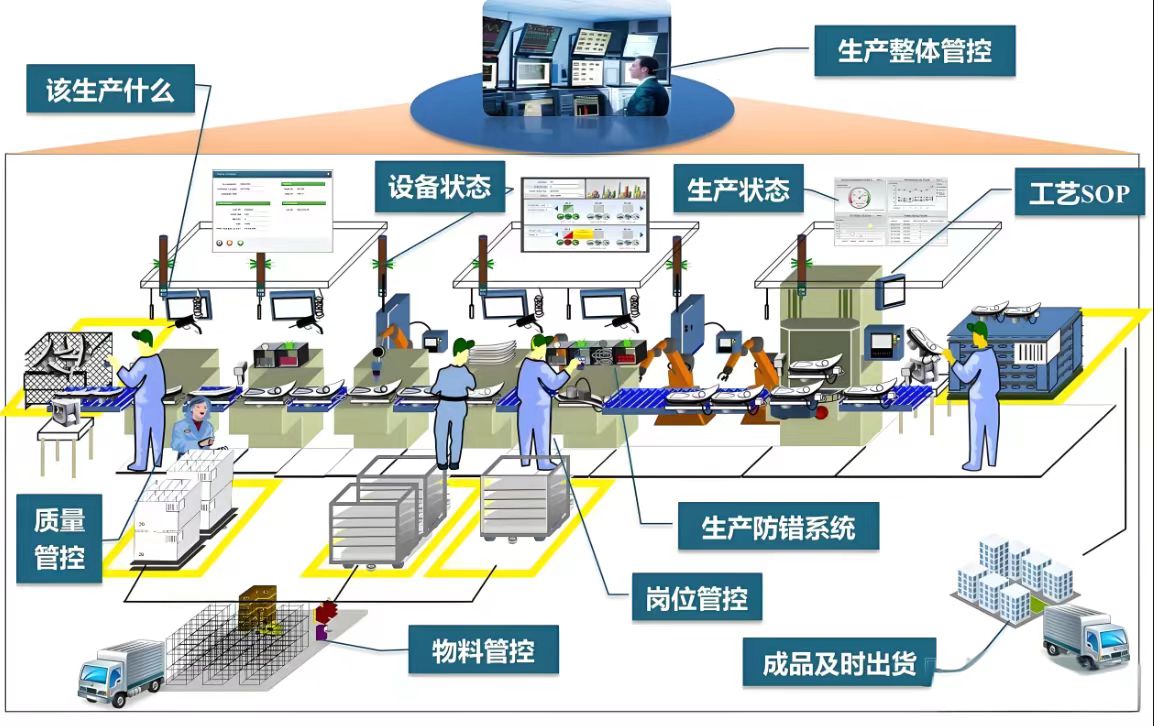

制造業(yè)數(shù)字化轉(zhuǎn)型:破局與騰飛之路

后摩爾定律時代,提升集成芯片系統(tǒng)化能力的有效途徑有哪些?

手機(jī)散熱器拆解

MES使用后對工廠車間產(chǎn)生的重大影響

基于PREEvision的線束設(shè)計工作流程優(yōu)化

ARM發(fā)布旗艦手機(jī)芯片:性能提升、AI性能增強(qiáng)、節(jié)能減耗

芯片封裝的力量:提升電子設(shè)備性能的關(guān)鍵

蘋果M3芯片性能提升

ZR機(jī)械手:提高生產(chǎn)效率,降低成本的有效途徑-速程精密

ITO薄膜光學(xué)性能受退火工藝溫度的影響

單個芯片性能提升的有效途徑

單個芯片性能提升的有效途徑

評論