引言:本文描述了一種簡單高效配置FPGA的方法,該方法利用微處理器從串行外圍接口(SPI)閃存配置FPGA設備。這種方法減少了硬件組件、板空間和成本。

1. 介紹

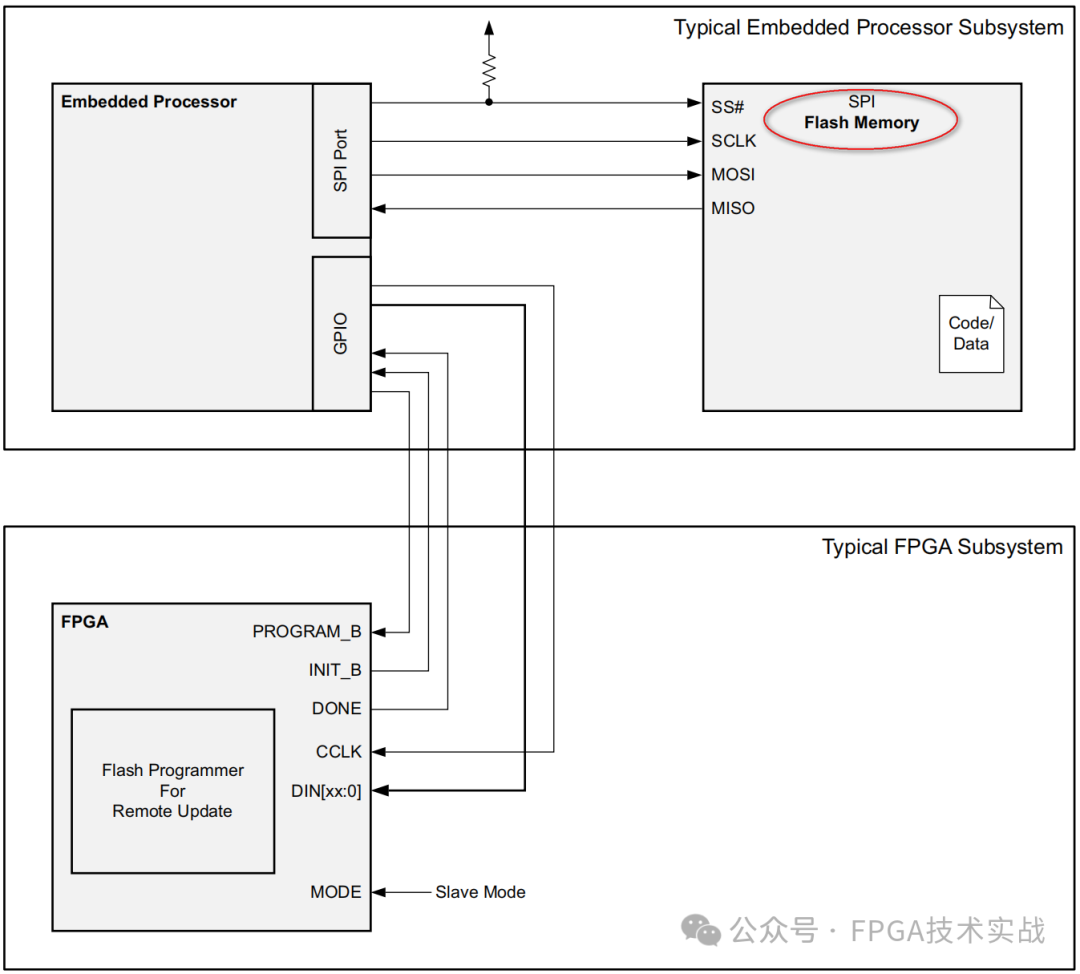

產品中包含分立的嵌入式微處理器和FPGA是常見的,帶FPGA的典型嵌入式微處理器系統如圖1所示。這些類型的系統包括兩個典型的子系統,子系統具有獨立的SPI Flash配置芯片。

圖1:帶FPGA的典型嵌入式微處理器系統配置方法

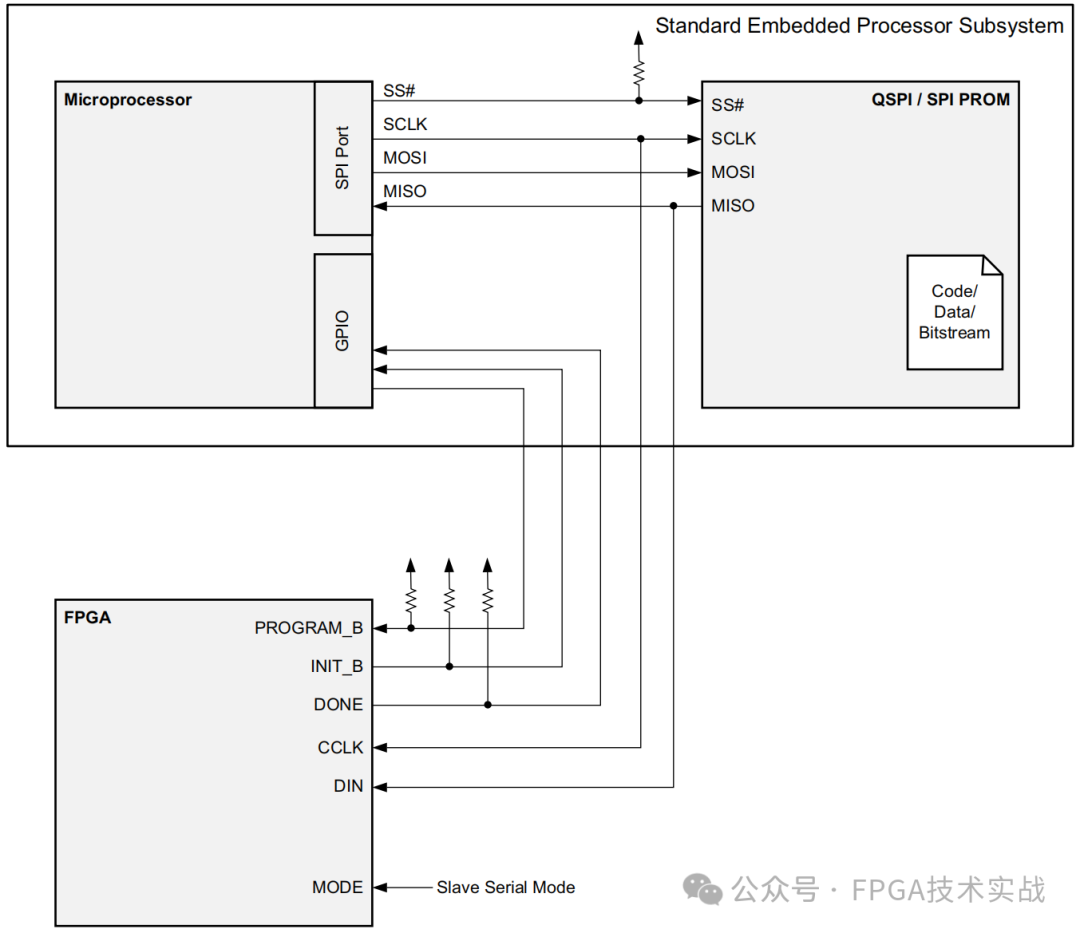

XAPP583中描述了利用微處理器配置FPGA的推薦方法。這種方法是將用戶固件以及配置位文件存儲在連接到微處理器的Flash設備上。微處理器通過SPI接口讀取比特文件,然后通過從串行或從SelectMAP接口將比特流發送到FPGA。這消除了對FPGA配置的額外PROM的需要。框圖如圖2所示。

圖2:XAPP583文檔配置嵌入式微處理器系統方法

本文描述的方法進一步簡化了配置方案。它利用了FPGA的從串行配置引腳與標準SPI總線信號之間的兼容性。圖3展示了微處理器、Flash和FPGA之間的連接。

圖3:本文檔配置嵌入式微處理器系統方法

如圖3所示,連接到微處理器的Flash存儲用戶固件和FPGA比特文件。然而,微處理器并不直接通過FPGA配置端口來配置FPGA。相反,FPGA從串行DIN和CCLK引腳連接到Flash和微處理器之間的SPI總線。通過這種方法進行配置是可能的,因為從串行接口和配置序列與SPI協議一致。操作和實施詳細信息部分更詳細地解釋了兼容性。

此方法可以使用兩個連接。您只需要連接以下引腳即可將配置位流傳輸到目標FPGA:

?FPGA CCLK引腳連接到SPI總線SCLK引腳。

?FPGA DIN引腳連接到SPI總線MISO引腳。

還可以包括用于配置控制或監控的附加信號。以下FPGA引腳應連接到微處理器GPIO引腳以啟用功能:

?PROGRAM_B:重置FPGA配置序列。

?INIT_B:檢查配置初始化或錯誤狀態。

?DONE:監控配置成功。

與圖1中所示的帶有嵌入式微處理器和Flash的傳統系統相比,此解決方案提供了多種優勢:

?減少了組件數量:系統只需要一個Flash;

?更少的微處理器GPIO和更少的代碼空間:與其他基于嵌入式微處理器的配置解決方案相比,可以改善配置時間。

?基于微處理器的FPGA配置控制和監控功能:超過了本地FPGA配置功能。

?系統內PROM更新:此解決方案支持在微處理器上使用標準Flash編程庫來更新存儲的比特流。

2. 操作和實施細節

本節介紹FPGA從串行配置接口和時序,以及使用Zynq-7000 AP SoC處理子系統配置FPGA的方法。

2.1 FPGA從串行配置模式

從串行模式(FPGA配置模式之一)由于其簡單性而高效。下面列出了它的一些關鍵屬性。本應用說明中描述的配置方法利用了這些屬性。

2.2 簡化配置方法

如果系統通電后只需要配置一次FPGA,那么配置方法可以很簡單,只需連接以下引腳即可:

?FPGA CCLK引腳連接到SPI總線SCLK引腳。

?FPGA DIN引腳連接到SPI總線MISO引腳。

在Zynq-7000 AP SoC開始配置之前,FPGA應準備好接收配置數據。換句話說,FPGA應該已經完成了從初始通電開始的配置空間的擦除階段。

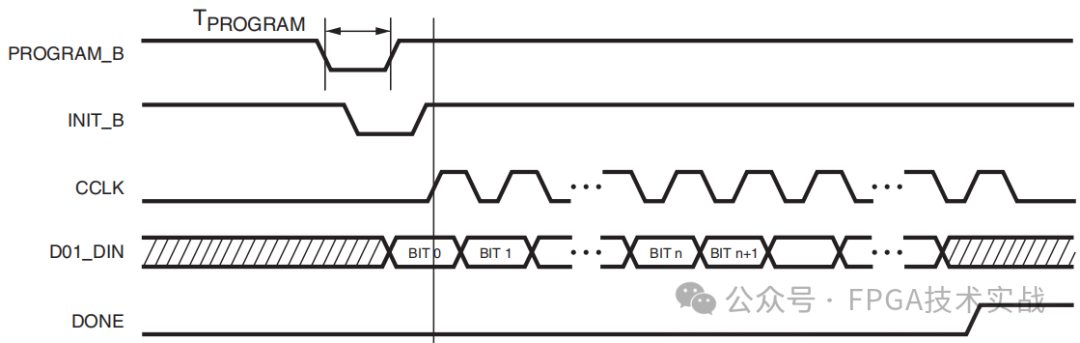

圖4:FPGA配置時序圖

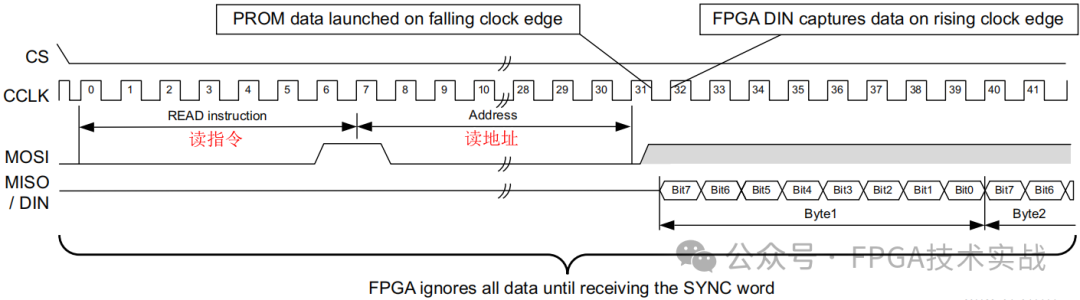

接下來,Zynq-7000 AP SoC向SPI Flash發送單個讀取命令,并從SPI Flash讀取整個比特流。在SPI Flash串行讀取操作期間,比特流也通過SPI總線MISO信號串行傳輸到FPGA DIN引腳。SPI Flash在SCLK/CCLK的下降沿上輸出每個串行數據位。FPGA在SCLK/CCLK的下一個上升沿捕獲串行數據位。在從SPI Flash讀取整個比特流時,FPGA被有效地配置。

FPGA配置接口的三個特性使FPGA DIN和CCLK引腳能夠直接連接到用于FPGA配置的SPI總線:

?SPI總線串行數據(MISO)和時鐘(SCLK)信號分別與FPGA從串行數據(DIN)和時鐘引腳兼容。

?FPGA配置接口在比特流讀取操作之前忽略所有SPI總線活動。因為FPGA丟棄所有傳入數據,直到它接收到有效的32位同步字,所以有效地忽略了所有SPI總線活動。

?配置操作完成后,FPGA配置接口忽略所有SPI總線活動。由于FPGA在配置完成后停止監測其DIN輸入,因此FPGA有效地忽略了位流讀取操作后的所有SPI總線活動。

圖5說明了SPI總線和FPGA配置事務的關系。

圖5:SPI與FPGA之間時序關系

2.3 帶有附加控件的配置方法

另一種增強配置操作和能力的方法是使用Zynq-7000 AP SoC來控制FPGA配置引腳。例如,Zynq-7000 AP SoC可以使用其GPIO引腳驅動FPGA PROGRAM_B引腳來清除FPGA配置Flash并重新啟動配置。這允許基于系統操作條件來重新配置用戶設計。它可以為某些用戶設計提供巨大的優勢,這些用戶設計受益于操作過程中的功能變化。

此外,Zynq-7000 AP SoC可以通過將其GPIO引腳連接到FPGA DONE和INIT_B引腳來監測FPGA配置準備情況和結果。INIT_B是一個配置錯誤或就緒信號。DONE信號是一個配置完成指示器。這些狀態信號為Zynq-7000 AP SoC提供信息,以做出有效決策,確保可靠配置。

例如,從配置故障中恢復的一種流行方案稱為配置回退。如果Flash中的目標位文件損壞,則用戶設計不進行配置,FPGA也不起作用。在這種情況下,固件通過檢查INIT_B和DONE信號來檢測情況。然后,它通過使用Flash中的已知良好(golden)位文件重新配置FPGA來緩解問題。這使FPGA達到已知的功能狀態,以避免災難性的系統故障。

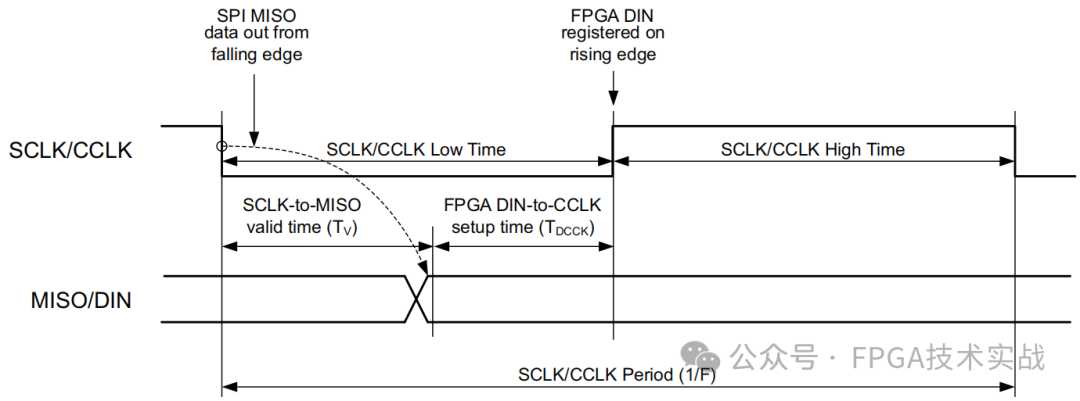

2.4 SPI總線SCLK最大頻率

SPI總線上的數據在相反的時鐘邊沿上被啟動和捕獲。SCLK頻率的限制因素是最小SCLK/CCLK低時間。如圖5所示,它由從SCLK的下降沿到CCLK的上升沿的SPI Flash MISO輸出數據有效時間和FPGA DIN輸入設置時間之和決定。

圖6:SPI總線到FPGA時序

以下等式估計SPI總線支持FPGA配置的最大SCLK頻率:

其中:

?TV=SPI Flash SCLK到MISO數據輸出有效時間。

?TDCCK=FPGA DIN輸入設置到CCLK設置時間。

?SCLKLow duty cycle %, minimum=時鐘周期內SCLK低的最小百分比。

為了獲得更準確的估計,SCLK/CCLK和MISO/DIN信號的PCB走線路徑和相應傳播延遲的適用分量應納入上述方程式。

此外,SCLK信號(FPGA CCLK引腳)的信號完整性至關重要。為了實現最大可能的時鐘頻率,請使用最佳實踐來設計并將此時鐘信號從Zynq-7000 AP SoC路由到SPI Flash和FPGA端點。

3.參考設計

本文提供了一個示范參考設計。它使用Zynq-7000全可編程SoC(AP SoC)和目標板上的FPGA實現了圖2所示的解決方案。您可以從Xilinx網站下載本應用說明的參考設計文件。表1顯示了參考設計矩陣。

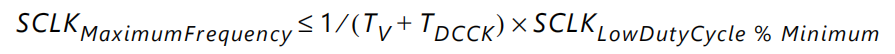

3.1 硬件設計

硬件設計基于Zynq-7000 AP SoC 7Z045 CLG484器件。AP SoC Quad SPI控制器連接到支持SPI x1、x2或x4寬度的多I/O存儲器設備。盡管Zynq Quad SPI控制器也可以支持x1、x2、x4和x8寬度,但此參考設計適用于使用單比特總線寬度的傳統SPI協議。下圖顯示了Zynq-7000 AP SoC、SPI PROM和Kintex-7 FPGA之間的硬件連接。

圖7:示例硬件原理圖

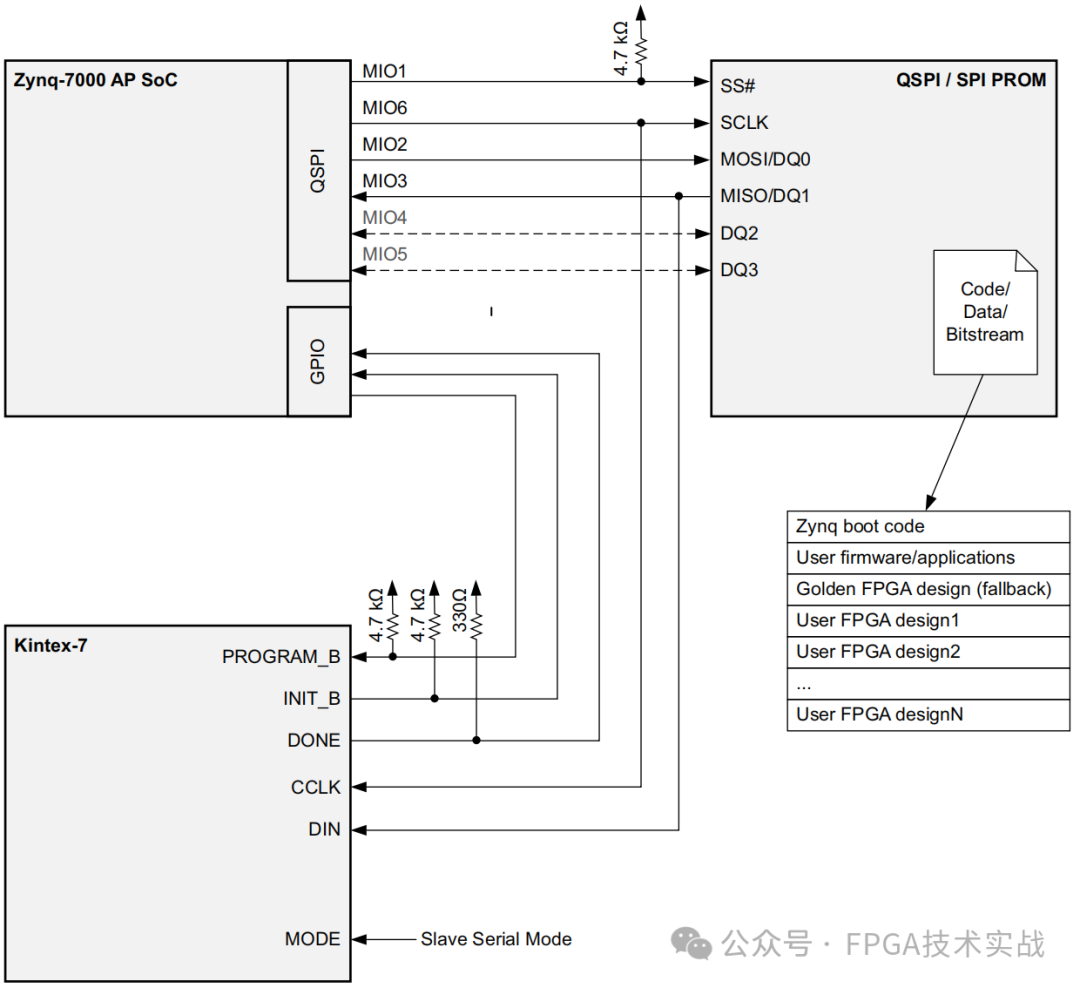

參考硬件設計在Vivadodesign Suite項目中提供。AP SoC內的系統框圖如圖8所示。

圖8:Vivado實現框圖

3.1 固件流程

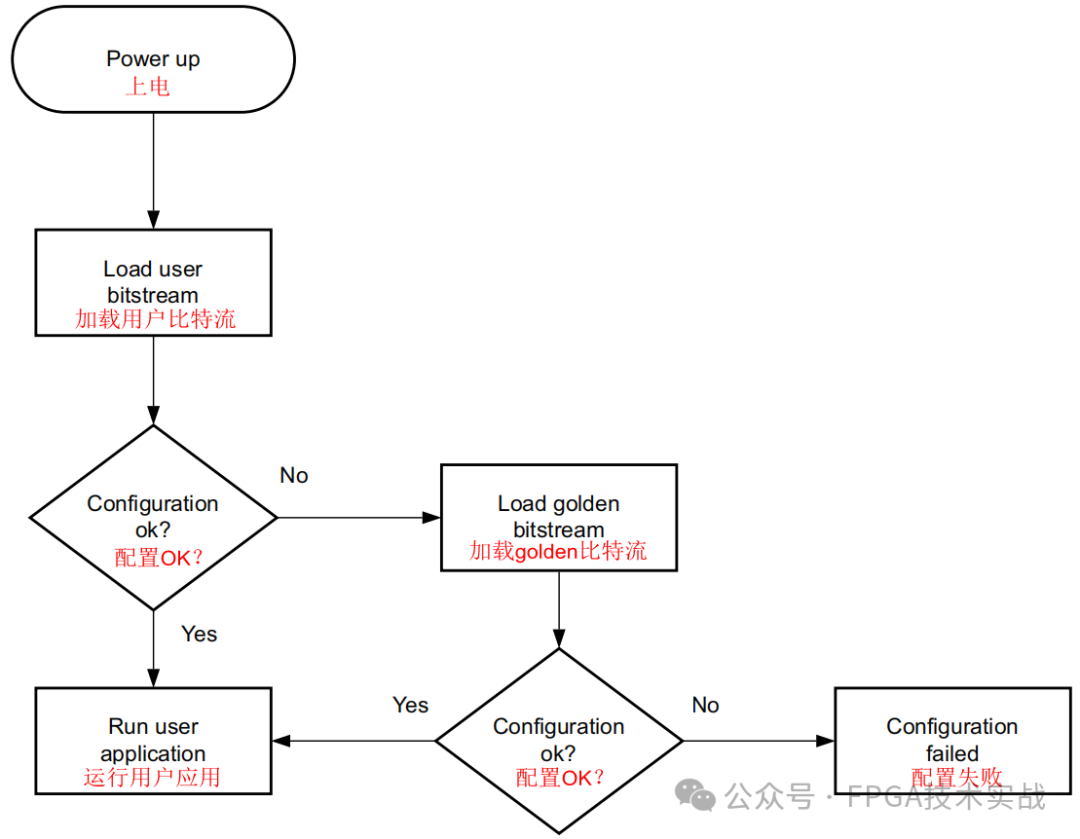

參考設計利用存儲在SPI Flash中的更新的(最新設計修訂版)比特流和Golden(已知良好的)比特流來實現嘗試和回退配置方案。Zynq-7000 AP SoC固件首先嘗試加載最新的預期比特流。然后,如果配置不成功,固件將重新啟動配置并加載黃金比特流。此過程稱為回退配置。固件流程圖如圖9所示。

圖9:固件加載流程圖

固件配置算法的詳細信息:

(1)將Zynq-7000AP SoC Quad SPI接口配置寄存器初始化為I/O模式。

?執行諸如設置時鐘分頻器、芯片選擇模式和啟用控制器等任務。

(2)清除FPGA配置內存。

?斷言PROGRAM_B的時間段至少比TPROGRAM長,然后取消斷言。

(3)等待INIT_B釋放。

?輪詢INIT_B引腳,以確保FPGA已完成房屋清潔階段。

(4)設置Quad SPI控制器傳輸功能。

?演示使用輪詢數據傳輸函數XQspiPs_PolledTransfer()。功能原型為:int XQspiPs_PolledTransfer(XQspiPInstancePtr,u8SendBufTr,u8*RecvBufPtr,unsigned ByteCount);

?InstancePtr是指向Quad SPI實例的指針

?SendBufPtr和RecvBufPtr分別是發送和接收緩沖區指針。此功能要求發送和接收緩沖器的字節數與將重新配置FPGA的比特流的長度相同。

?ByteCount是要傳輸的字節數。

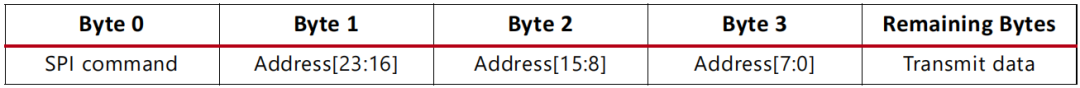

?發送緩沖區的第一個字包含命令和地址,如表2所示。第一個字節包含用于Quad SPI存儲器設備的命令。在這種情況下,它將發送讀取字節命令(0x03)。只需要一個命令即可完成整個操作。目標比特流的24比特起始地址被劃分為三個字節。緩沖區其余部分的內容是未定義的,因為這是一個讀取操作。

表2:Quad SPI寫入緩沖區定義

(5)呼叫輪詢傳輸功能

?調用該函數后,Quad SPI控制器將發送緩沖區的內容發送到Quad SPI存儲器。同時,它讀取的字節數與比特流的大小相同。由于FPGA的DIN和CCLK引腳連接到SPI控制器的MISO和SCK信號,當檢測到SYNC字時,FPGA(設置為從串行配置模式)將開始配置。FPGA是在比特流被完全讀取時配置的。

(6)檢查錯誤

?配置FPGA后,如果INIT_B和DONE被斷言,則這表示成功讀取結束。

?但是,如果INIT_B和/或DONE引腳保持低位,固件將加載已知的良好配置(即Golden比特流)并重新配置FPGA。這被稱為配置回退。

4.結論

本文介紹的FPGA配置解決方案降低了包含微處理器、SPI Flash和FPGA的典型系統的硬件和固件要求。它利用了FPGA串行配置模式和SPI存儲器之間的兼容性。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

602986 -

嵌入式

+關注

關注

5082文章

19104瀏覽量

304799 -

FlaSh

+關注

關注

10文章

1633瀏覽量

147939 -

微處理器

+關注

關注

11文章

2258瀏覽量

82403 -

SPI

+關注

關注

17文章

1706瀏覽量

91502

原文標題:基于微處理器實現SPI Flash配置FPGA設計

文章出處:【微信號:FPGA技術實戰,微信公眾號:FPGA技術實戰】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一種基于FPGA的UART實現方法設計

Nexar如何為FPGA設計提供一種全新的方法?

一種密鑰可配置的DES加密算法的FPGA

一種基于SRAM的FPGA的加密方法

一種通用SPI接口的FPGA設計與實現

一種簡單高效配置FPGA的方法

一種簡單高效配置FPGA的方法

評論