引言:本文繼續介紹Verilog HDL基礎知識,重點介紹賦值語句、阻塞與非阻塞、循環語句、同步與異步、函數與任務語法知識。

1. 賦值語句

在Verilog中,有兩種進行賦值的方法,即連續賦值語句和過程賦值語句(塊)。

1.1 連續賦值語句

連續賦值用于表示組合邏輯。左側必須是Net數據類型即wire和tri類型。

連續賦值始終處于活動狀態,這意味著,對右側值的任何更改都會導致賦值左側值被更新。

//連續賦值方法1 wire [15:0] adder_out = mult_out + out; //連續賦值方法2 wire [15;0] adder_out; assign adder_out = mult_out + out;在仿真測試中,可以對連續賦值語句分配延遲,但在綜合時,該延遲被忽略。

assign#5adder_out=mult_out+out;//延遲5ns

1.2 過程賦值語句(塊)

過程賦值語句包括initial和always兩種。intial語句用于初始化仿真使用,always使用行為功能描述電路功能。

每個always和initial塊都是并行運行的,但每個塊內部是順序執行的。

圖1:過程賦值語句示例

2. 阻塞賦值和非阻塞賦值

always和initial過程塊有種類型賦值即阻塞賦值(=)和非阻塞賦值(<=)。

過程賦值的左側必須是變量數據類型,可以是reg、integer、real或time或realtime。賦值的右側可以是任何有效的表達式或信號。

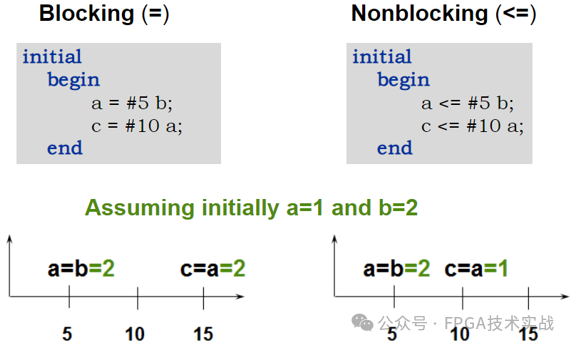

阻塞賦值和非阻塞賦值示例如下圖所示。

圖2:阻塞賦值和非阻塞賦值示例

如圖2左側阻塞賦值,兩條語句同時執行,延遲#5時,a=b=2,再延遲#10時,c=a=2,即賦值語句立即執行,執行完畢后才執行下一條語句,左側值在賦值語句執行完后立即改變。如圖2右側非阻塞賦值,延遲#5時,a=b=2,而再延遲#5時,c=a=1,即c值并未立即為a的新值。

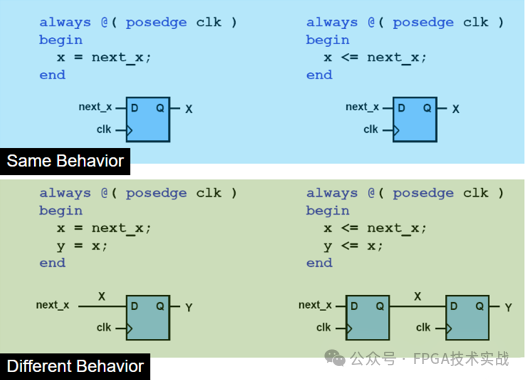

圖3展示了阻塞賦值和非阻塞賦值綜合后的RTL電路舉例。

圖3:阻塞賦值和非阻塞賦值綜合后的RTL電路舉例

阻塞賦值和非阻塞賦值使用規則

組合電路一般使用阻塞賦值,時序電路使用非阻塞賦值,這可以避免混淆,提高代碼可讀性。

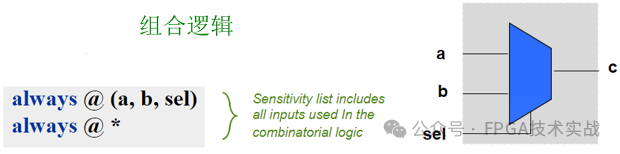

3. 兩種類型RTL處理:組合邏輯處理和時序邏輯處理

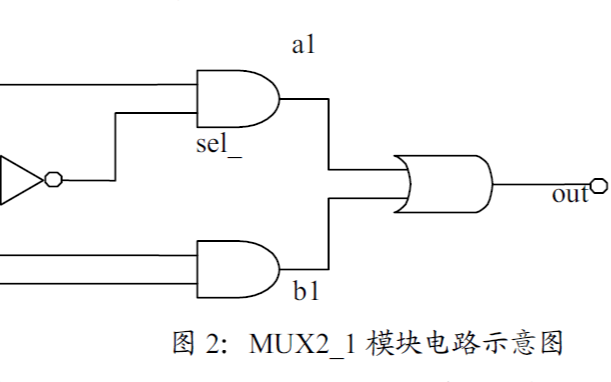

組合邏輯處理:對所有輸入列表信號敏感,用于組合邏輯。

圖4:組合邏輯處理

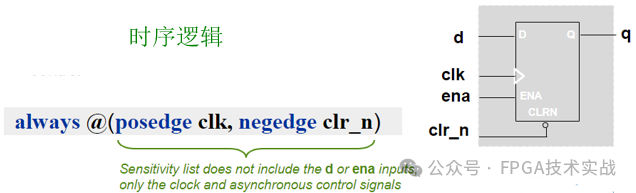

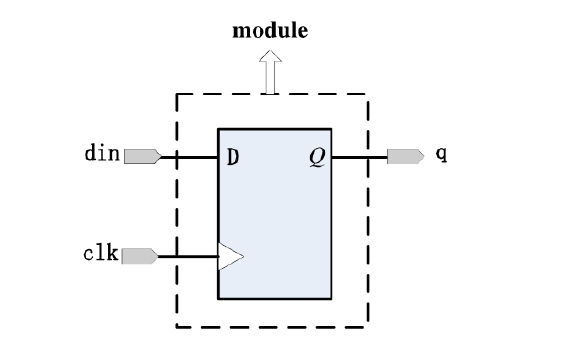

時序邏輯處理:對時鐘信號或者控制信號沿敏感(通過添加posedge或者negedge關鍵字),用于時序邏輯。

圖5:時序邏輯處理

4. 過程塊語句

initial和always過程塊中有三種常用語句:if-esle、case和循環語句。

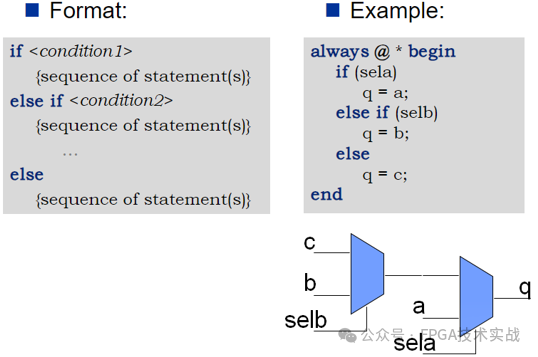

4.1 if-else語句

語句以關鍵字if開頭,后跟一個條件,然后是條件為true時要執行的語句序列。else子句(如果存在)將在條件為false時執行。

圖6:if-else示例

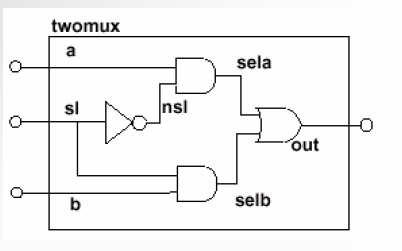

可以看到if語句合成為兩個輸入復用器。可以看到,多個if語句會導致多個復用,從而產生優先級。如果不需要在你的電路中進行優先級排序,case語句會更有效率。

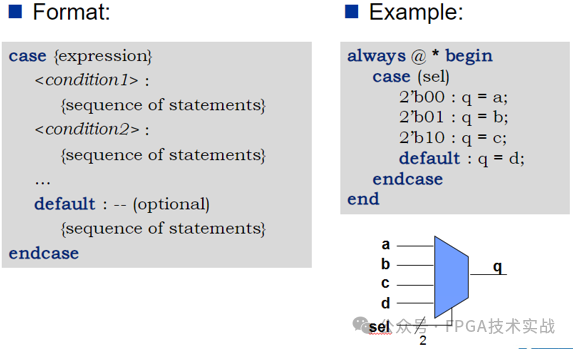

4.2 case語句

在case語句中,所有條件都將根據表達式進行檢查。這導致一個多路復用器具有多個輸入。

圖7:case語句示例

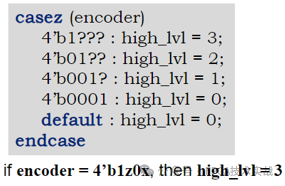

casez語句將表達式或條件中的所有'z'值視為不關心。

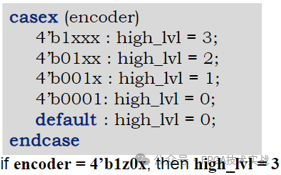

casex語句將所有“x”和“z”值視為不關心,而不是邏輯值。

圖8:casez和casex語句示例

4.3 循環語句

(1)forever循環語句示例

initialbegin clk = 0; forever#25clk=~clk; end

以上示例為周期為#50的clk時鐘,注意該語句不可綜合,只能用于仿真。

(2)repeat循環語句

if(rotate == 1) repeat(8)begin//循環8次 temp=data[15]; data = {data <<1,temp}; ??end ?

repeat語句可以設置循環的次數,該語句可以用于綜合,要具有明確的循環表達式和循環條件。

(3)while循環語句

initial begin cnt = 0; while(cnt

cnt循環計數100次,在cnt為101時退出循環,該語句可以用于綜合,要具有明確的循環表達式和循環條件。

(4)for循環語句

integer i; always @(inp,cnt) begin result[7:4] = 0; result[3:0] = inp; if(cnt==1)begin for(i=4;i<=7;?i=i+1)?begin ??????result[i]?=?result[i-4]; ????end ? ??end end

以上for循環語句實現4bit左移位功能,for語句可以進行綜合,實現硬件電路。

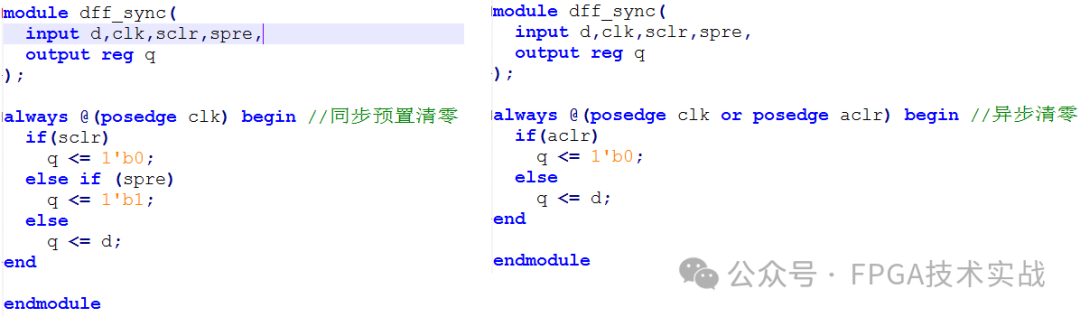

5. 同步邏輯和異步邏輯

圖9:同步邏輯及異步邏輯

always敏度列表表達方式將導致控制信號是同步的或異步的。上圖中左側代碼具有同步預置和觸發器清除功能,該代碼僅在時鐘上升沿敏感,右側代碼敏感列表包含時鐘和異步清除信號,如果aclr上升沿觸發,就會引起q清零,不受時鐘控制。

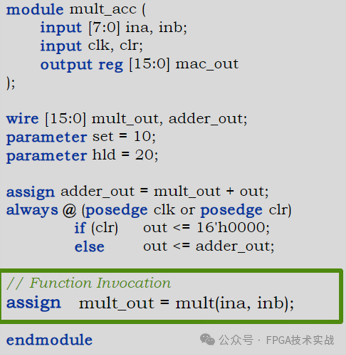

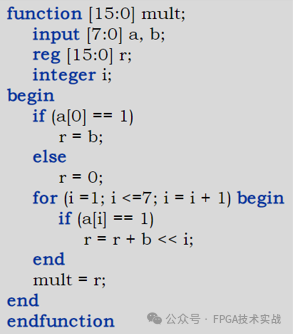

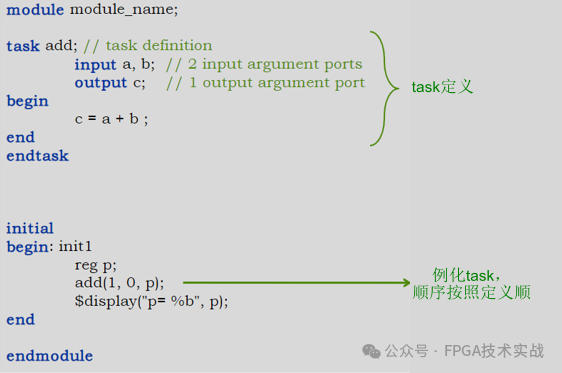

6. 函數(function)和任務(task)

Verilog HDL有兩種子程序,函數和任務。它們都必須在模塊中定義。函數根據其輸入返回一個值。函數通常產生組合邏輯,并用于assign表達式中。

任務和函數對于模塊中的重復代碼非常有用。它們提高了代碼的可讀性。

圖10:function示例

圖11:task示例

function和task的異同點

相同點:

(1)任務和函數必須在模塊內定義,其作用范圍僅適用于該模塊,可以在模塊內多次調用;

(2)任務和函數中可以聲明局部變量,如寄存器,時間,整數,實數和事件,但是不能聲明線網類型的變量;

(3)任務和函數中只能使用行為級語句,但是不能包含always和initial塊,設計者可以在always和initial塊中調用任務和函數。

差異點:

(1)函數能調用另一個函數,但是不能調用任務,任務可以調用另一個任務,也可以調用函數;

(2)函數總是在仿真時刻0開始 ,任務可以在非零時刻開始執行;

(3)函數一定不能包含任何延遲,事件或者時序控制聲明語句,任務可以包含延遲,事件或者時序控制聲明語句;

(4)函數至少要有一個輸入變量,也可以有多個輸入變量,任務可以沒有或者有多個輸入,輸出,輸入輸出變量;

(5)函數只能返回一個值,函數不能有輸出或者雙向變量,任務不返回任何值,或者返回多個輸出或雙向變量值。

-

仿真

+關注

關注

50文章

4070瀏覽量

133552 -

Verilog

+關注

關注

28文章

1351瀏覽量

110074 -

HDL

+關注

關注

8文章

327瀏覽量

47376 -

循環語句

+關注

關注

0文章

10瀏覽量

4859

原文標題:Verilog HDL基礎知識(二)

文章出處:【微信號:FPGA技術實戰,微信公眾號:FPGA技術實戰】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA就業培訓

FPGA就業培訓班

【干貨】史上最全的硬件描述語言Verilog學習資料(FPGA工程師進階必學)

Verilog數字系統設計教程(第3版)

Verilog HDL基礎知識

Verilog HDL綜合實用教程

Verilog HDL的基礎知識

Verilog HDL的基礎知識詳細說明

Verilog教程之Verilog HDL數字集成電路設計方法和基礎知識課件

Verilog HDL的基礎知識詳細概述

Verilog HDL的基礎知識

Verilog HDL的基礎知識

評論