不用重新布局布線,更新時序約束,如何快速查看時序報告?

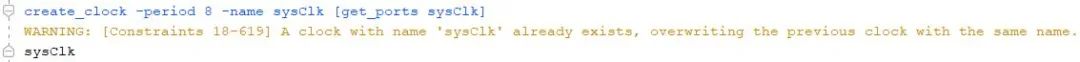

有時我們對時序約束進行了一些調整,希望能夠快速看到對應的時序報告,而又不希望重新布局布線。這時,我們可以打開布線后的dcp,直接在Vivado Tcl Console里輸入更新后的時序約束。如果調整后的約束在之前版本中已存在,那么Vivado會給出警告信息,顯示這些約束會覆蓋之前已有的約束;如果是新增約束,那么就會直接生效。例如,我們需要把時鐘周期由10ns調整為8ns,就可以進行如下圖所示的操作:

執行上述命令后,就可以重新生成時序報告了。需要說明的是這種方法只是用來快速查看時序報告以評估時序性能。如果把調整后的時序約束添加到工程中重新布局布線,得到的結果很有可能跟這種方式看到的不一樣,這是因為布局布線本身是受時序驅動的。

如何查看當前布線結果在更高速度等級芯片上的時序性能?

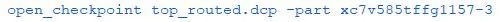

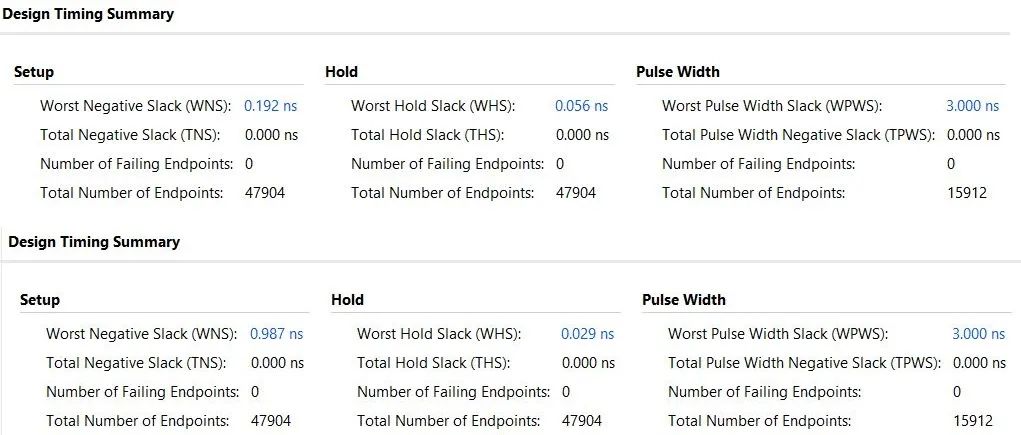

例如我們在速度等級為-2的芯片上完成了布局布線,需要進一步評估在速度等級為-3的芯片上時序裕量會有多大的提升,或者觀察一下在速度等級為-1的芯片上時序能否收斂。這時我們只需用Vivado打開布線后的dcp,只是在打開dcp時選擇芯片型號對應的速度等級為-3,其余封裝保持不變,這需要借助Tcl命令open_checkpoint完成,如下圖所示。在此基礎上生成時序報告即可對比時序性能的變化。

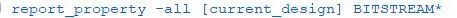

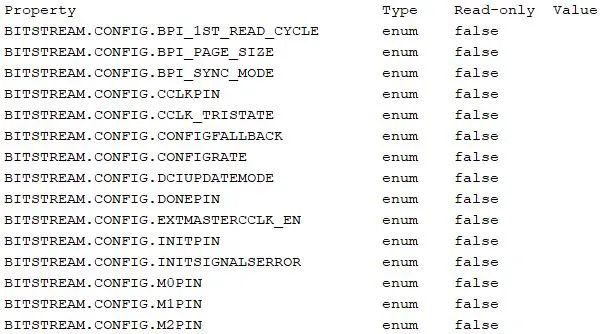

如何查看當前設計BITSTREAM屬性信息?

可以使用如下Tcl命令生成BITSTREAM屬性信息,需要打開布線后的網表文件。第1列為屬性名,第2列為屬性值的類型,第3列為屬性是否只讀,第4列為屬性值。

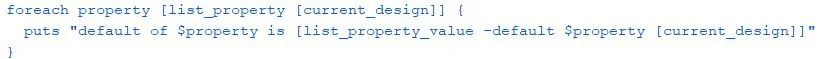

如果要知道屬性的默認值,可采用如下圖所示的Tcl腳本。

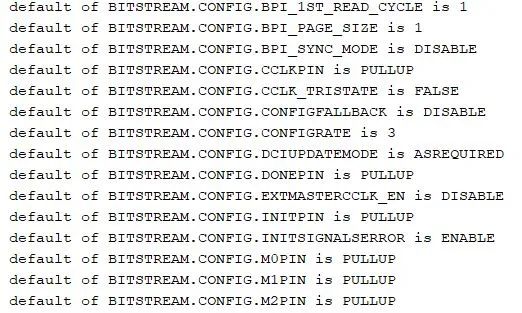

Vivado 2023.1 Pblock大小不合規報錯怎么處理呢?

在Vivado 2023.1中,如果Pblock大小不合規就會報錯,如下圖所示。這其實是合理的,Vivado 2023.1及之后的版本都會如此處理。而2022.2及之前版本則不會報錯,那是因為工具會自動進行調整,但這種調整只是保證Pblock大小合法,并不能保證一定符合用戶預期。正因此,2023.1版本開始就更為嚴格了。

-

芯片

+關注

關注

459文章

51901瀏覽量

433369 -

時序約束

+關注

關注

1文章

117瀏覽量

13570 -

布局布線

+關注

關注

1文章

89瀏覽量

15303 -

Vivado

+關注

關注

19文章

823瀏覽量

67879

原文標題:Vivado使用小技巧

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Vivado 實現

探索Vivado HLS設計流,Vivado HLS高層次綜合設計

Vivado 2017.1和Vivado 2016.4性能對比分析

Vivado獲取License的步驟教程

Tcl在Vivado中的基礎應用

xilinx Vivado工具使用技巧

關于Vivado 2019.1的Dashboard功能詳解

使用Vivado License Manager時Vivado的錯誤信息

【FPGA Vivado】基于 FPGA Vivado 的流水燈樣例設計

如何升級Vivado工程腳本

Vivado調用Modelsim仿真

Vivado設計套件用戶:使用Vivado IDE的指南

評論