前言

用RAM實(shí)現(xiàn)一個(gè)DDS,從原理上來說很簡(jiǎn)單,在實(shí)際使用的時(shí)候,可能沒有直接使用官方提供的IP核來的方便。這個(gè)博客就記錄一下,最近使用到的這個(gè)DDS IP。

1 基于相位截?cái)嗟腄DS

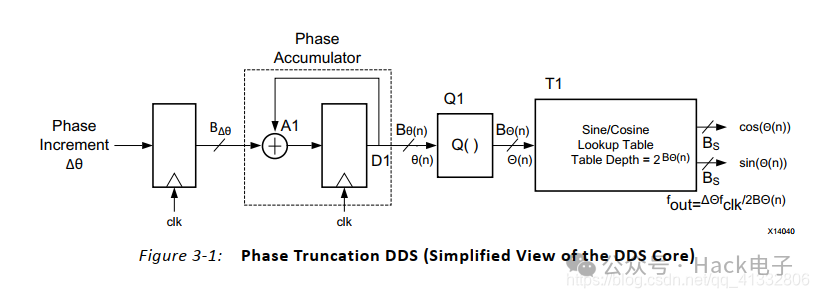

DDS IP核的內(nèi)部的基本結(jié)構(gòu)如下圖所示,主要是一個(gè)基于相位截?cái)嗟腄DS。在數(shù)字信號(hào)處理中,經(jīng)常會(huì)使用到DDS,其內(nèi)部主要有一個(gè)相位累加器,一個(gè)ROM存儲(chǔ)這正弦波的查找表。相位累加器在時(shí)鐘的作用下對(duì)相位進(jìn)行累加,每次的累加值是通過phase increment 來指定的。累加得到的結(jié)果,通過量化器,取其高位,低位舍去,再將這個(gè)量化后的相位值,輸出到查找表,從查找表中得到最終的波形。

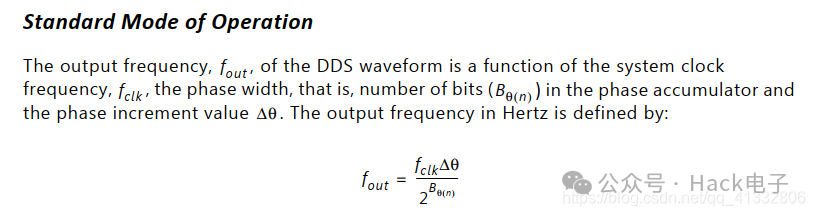

DDS的最終輸出的信號(hào)的頻率和系統(tǒng)時(shí)鐘,相位寬度和相位自增量之間滿足如下關(guān)系:

其中ΔΘ 是相位自增量,BΘ(n)是相位的位寬,也就對(duì)應(yīng)這查找表的深度為2^BΘ(n)

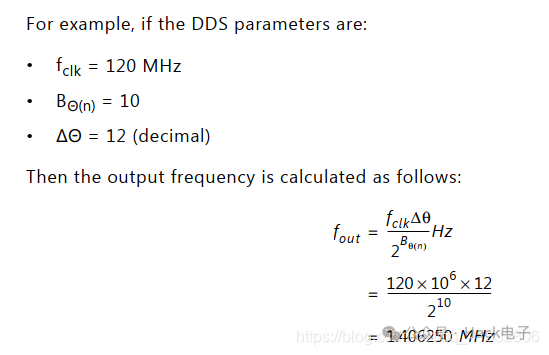

手冊(cè)中也給出了一個(gè)例子,來舉例說明DDS的輸出頻率和這幾個(gè)系統(tǒng)參數(shù)之間的關(guān)系,其中系統(tǒng)時(shí)鐘120MHz,相位寬度為10bit,相位增量為12,輸出的頻率通過上面的式子就可以計(jì)算出來。

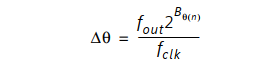

在實(shí)際的工程中,一般希望DDS能夠生成不停頻率的信號(hào),例如在DDC或者DUC中,希望產(chǎn)生一個(gè)高頻的載波頻率,通常使用DDS來產(chǎn)生一個(gè)高頻的正弦信號(hào)。因此在實(shí)際使用的時(shí)候更加關(guān)注DDS的相位增量。因?yàn)橥ㄟ^控制相位增量就能過后產(chǎn)生不同的頻率。相位增量的計(jì)算公式如下。

下面以一個(gè)具體的例子來說明DDS是如何工作的。

2 DDS IP的使用和參數(shù)配置

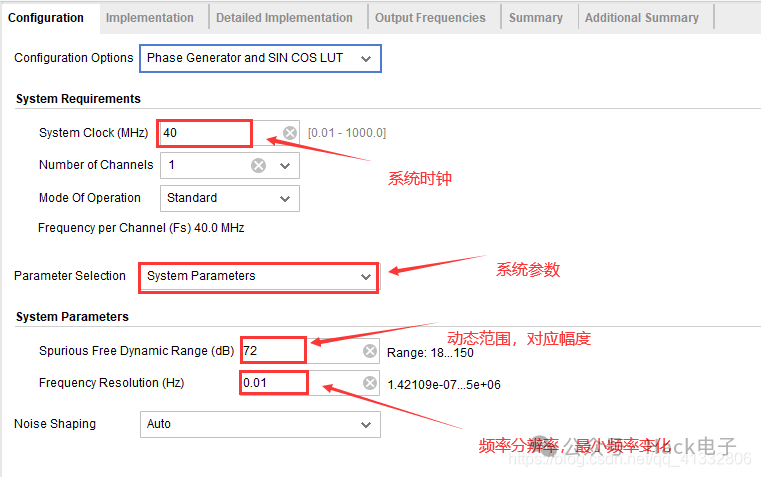

在配置這一TAB,需要設(shè)置系統(tǒng)的時(shí)鐘,這個(gè)時(shí)鐘也就是上面公式當(dāng)中的參考時(shí)鐘,然后可以選通道數(shù)和模式,這里就保持默認(rèn)就可以了。

再之后就是期望最終生成的信號(hào)的一些參數(shù)的設(shè)置。可選選擇系統(tǒng)參數(shù)模式,或者選擇硬件參數(shù)模式,一般都選擇系統(tǒng)參數(shù)模式,直接方便。

在系統(tǒng)參數(shù)中,動(dòng)態(tài)范圍最終對(duì)應(yīng)這輸出信號(hào)的幅度,其計(jì)算公式如下:20lg(Amp),其中AMP就是信號(hào)的幅度。比如下圖中,動(dòng)態(tài)范圍為72,那么他就可以表示幅度為4096的一個(gè)正弦信號(hào)。[20lg(4096)] = 72dB;

在下面是頻率分辨率,對(duì)應(yīng)這最小的頻率變化,是由系統(tǒng)時(shí)鐘和相位深度計(jì)算得到的,比如系統(tǒng)時(shí)鐘40MHz,相位寬度為32bit,那么計(jì)算的頻率分辨率就是[40*106/(232)] = 0.01。

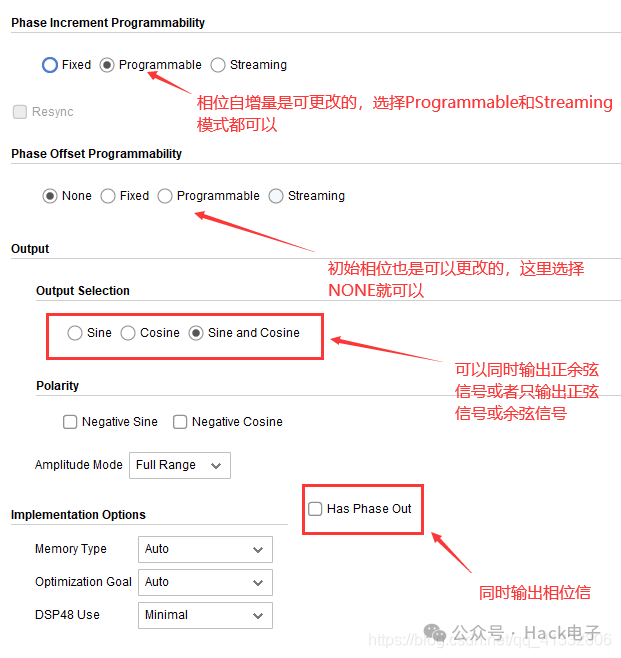

在實(shí)現(xiàn)這一TAB,可以設(shè)置相位增量是固定的還是可以更改的,相位增量能夠控制輸出的正余弦信號(hào)的頻率,這里選擇可更改的,便于在之后的使用中生成不同頻率的信號(hào)。需要注意的時(shí)候,生成的信號(hào)需要滿足奈奎斯特抽樣定理,也就是抽樣時(shí)鐘必須是被采樣信號(hào)頻率的兩倍。以這個(gè)例子來說,系統(tǒng)時(shí)鐘為40M,那么,最多可以生成頻率為20MHz的正余弦信號(hào)。

除了相位自增量外,初始的相位也是可以通過參數(shù)來修改的,在這里就默認(rèn)不修改了。

在輸出信號(hào)的時(shí)候,可以同時(shí)輸出正余弦信號(hào),這在正交調(diào)制解調(diào)的過程中十分有用。

除此之外,還可以輸出當(dāng)前的相位。

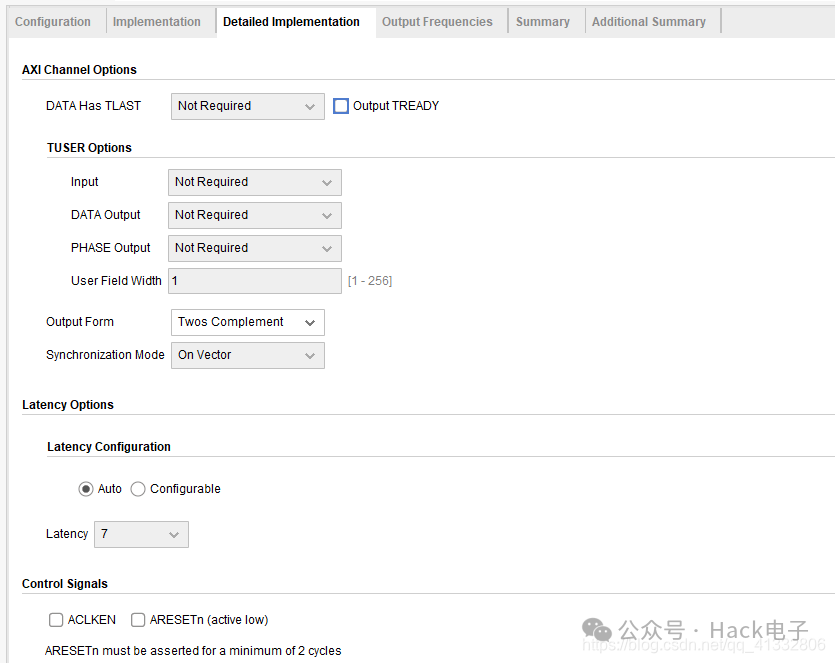

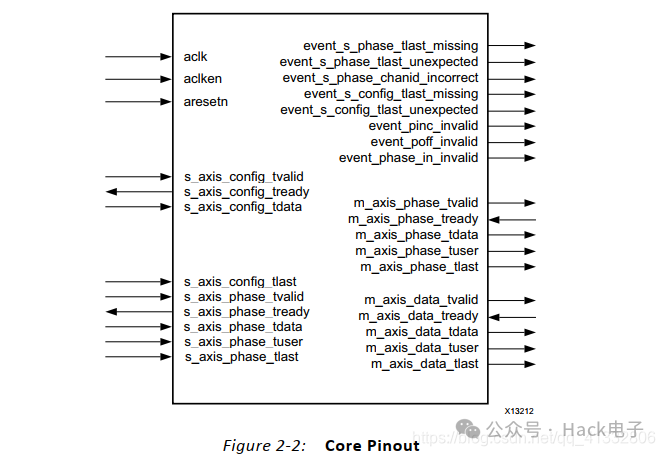

在具體實(shí)現(xiàn)這一TAB中,保持默認(rèn)就可以,是用來配置接口。根據(jù)手冊(cè)上描述的,可以選擇這些信號(hào)來生成不同類型的接口。這些接口都是AXI-Stream 類型的接口,只需要滿足AXIS的規(guī)則就好了。

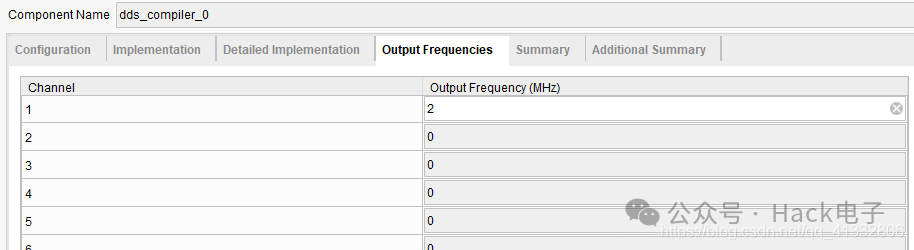

在輸出頻率這一TAB,可以輸入期望的輸出頻率,若有多個(gè)通道,可以選擇給多個(gè)通道設(shè)定初始的頻率輸出值。這個(gè)期望頻率在前面選擇了相位增量式可編程的時(shí)候就沒什么用了。因?yàn)樽罱K輸出的信號(hào)的頻率是通過相位增量來控制的。

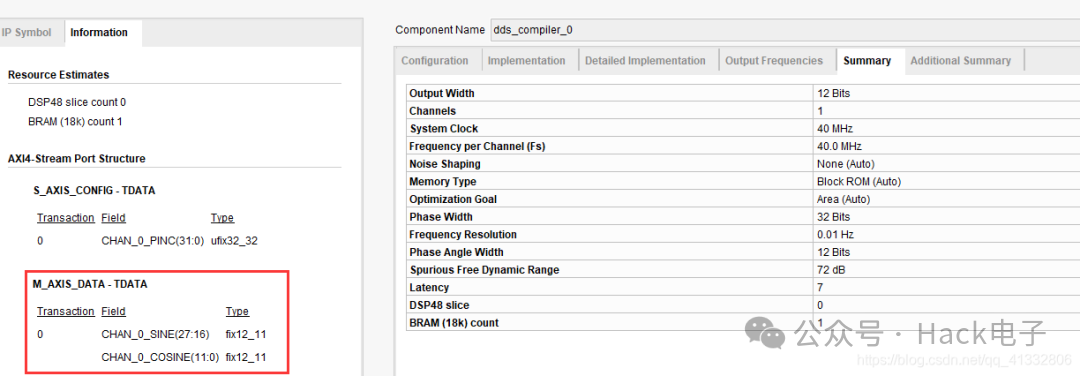

到這里這個(gè)IP基本就配置完了。可以看一下總結(jié),和最終輸出信號(hào)的接口信息。需要特別注意的就是輸出的正余弦信號(hào)在輸出總線上所占據(jù)的bit‘位。DDS IP通過一個(gè)AXIS接口同時(shí)輸出正弦信號(hào)和余弦信號(hào)。就比如在這個(gè)例子中,m_axis_data[11:0]傳輸?shù)木褪怯嘞倚盘?hào),其中m_axis_data[11]是余弦信號(hào)的符號(hào)位。

m_axis_data[27:16]傳輸?shù)氖钦倚盘?hào),其中m_axis_data[27]是正弦信號(hào)的符號(hào)位。

3 DDS IP測(cè)試

寫個(gè)Testbench測(cè)試一下:

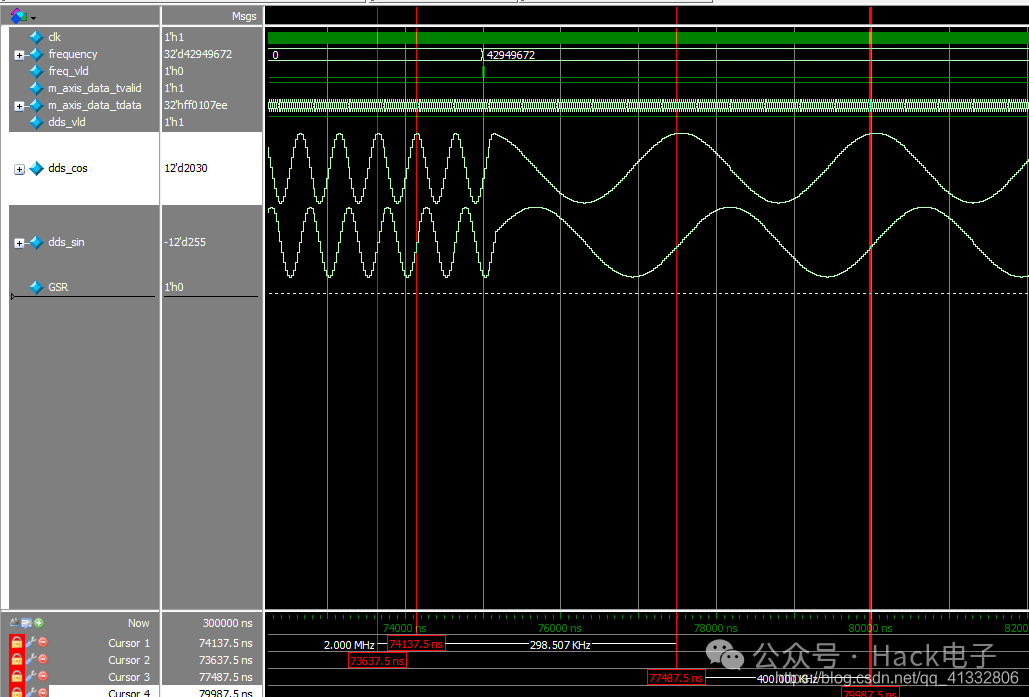

`timescale1ns/1ps moduletb_test_dds(); regclk; reg[31:0]frequency; regfreq_vld; wirem_axis_data_tvalid; wire[31:0]m_axis_data_tdata; wiredds_vld; wire[11:0]dds_cos; wire[11:0]dds_sin; assigndds_vld=m_axis_data_tvalid; assigndds_cos=m_axis_data_tdata[11:0]; assigndds_sin=m_axis_data_tdata[27:16]; //parameterSYS_CLK=40000000;//systemclock40M //parameterCLK_6M=6000000;//frequency6M //parameterCLK_400K=400000;//frequency400K //parameterCLK_2M=2000000;//frquency2M //parameterPHASE_WIDTH=32;//相位寬度為32bit //clock initialbegin clk=0; forever#(12.5)clk=~clk;//40Msystemclokc end initialbegin frequency='d0; freq_vld=1'b0; repeat(3000)@(posedgeclk); //產(chǎn)生一個(gè)頻率為400KHz的復(fù)指數(shù) frequency=32'd42949672;//CLK_400K*(2^PHASE_WIDTH)/SYS_CLK freq_vld=1'b1; @(posedgeclk) freq_vld=1'b0; repeat(3000)@(posedgeclk); //產(chǎn)生一個(gè)頻率為4MHz的復(fù)指數(shù) frequency=32'd214748364;//CLK_4M*(2^PHASE_WIDTH)/SYS_CLK freq_vld=1'b1; @(posedgeclk) freq_vld=1'b0; repeat(3000)@(posedgeclk); //產(chǎn)生一個(gè)頻率為6M的復(fù)指數(shù) frequency=32'd644245094;//CLK_6M*(2^PHASE_WIDTH)/SYS_CLK freq_vld=1'b1; @(posedgeclk) freq_vld=1'b0; end dds_compiler_0inst_dds( .aclk(clk),//inputwireaclk .s_axis_config_tvalid(freq_vld),//inputwires_axis_config_tvalid .s_axis_config_tdata(frequency),//inputwire[31:0]s_axis_config_tdata .m_axis_data_tvalid(m_axis_data_tvalid),//outputwirem_axis_data_tvalid .m_axis_data_tdata(m_axis_data_tdata)//outputwire[31:0]m_axis_data_tdata ); endmodule

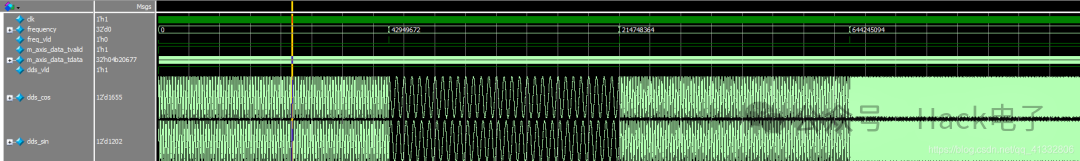

可以看到生成了不同頻率的正余弦信號(hào)。一開時(shí)的時(shí)候。沒有給出相位增量,所以固定輸出2M的信號(hào),之后給出了相位增量后,輸出了400K 信號(hào)。

-

Xilinx

+關(guān)注

關(guān)注

73文章

2181瀏覽量

124323 -

DDS

+關(guān)注

關(guān)注

22文章

671瀏覽量

154005 -

IP核

+關(guān)注

關(guān)注

4文章

338瀏覽量

50444

原文標(biāo)題:Xilinx DDS IP使用

文章出處:【微信號(hào):Hack電子,微信公眾號(hào):Hack電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

我用的是xilinx ISE 12.4 ,想問一個(gè)關(guān)于dds IP 核的問題

基于FPGA的IP核的DDS信號(hào)發(fā)生器如何用IP核

xilinx dds IP核輸出能不能改為無符號(hào)數(shù)

ip核使用問題

xilinx FPGA的FFT IP核的調(diào)用

如何使用DDS IP核生成任意波形?

基于FPGA的DDS IP核設(shè)計(jì)方案

Xilinx Vivado的使用詳細(xì)介紹(3):使用IP核

關(guān)于Xilinx中DDS IP的運(yùn)用與講解

關(guān)于Ultra96的Xilinx DDS編譯器IP教程

Xilinx Vivado DDS IP使用方法

如何申請(qǐng)xilinx IP核的license

評(píng)論