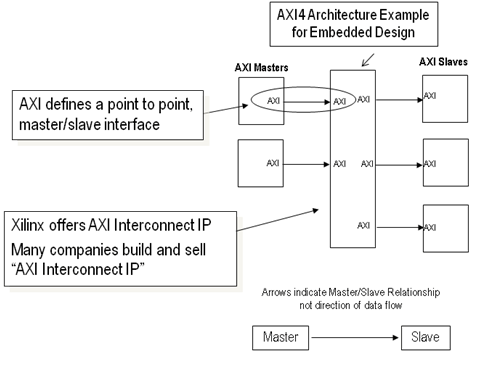

AMBA AXI4(高級(jí)可擴(kuò)展接口 4)是 ARM 推出的第四代 AMBA 接口規(guī)范。AMD Vivado Design Suite 2014 和 ISE Design Suite 14 憑借半導(dǎo)體產(chǎn)業(yè)首個(gè)符合 AXI4 標(biāo)準(zhǔn)的即插即用型 IP 進(jìn)一步擴(kuò)展了 AMD 平臺(tái)設(shè)計(jì)方法。 對(duì)于依靠 IP 來推動(dòng) UltraScale、7 系統(tǒng)、Zynq 7000、Virtex 6 和 Spartan 6 型設(shè)計(jì)上市進(jìn)程的客戶而言,AXI4 即插即用型 IP 提供了統(tǒng)一的標(biāo)準(zhǔn)接口,能顯著簡(jiǎn)化 IP 集成。AMD 提供了一系列豐富的基于 AXI4 的 IP,為嵌入式、DSP 以及邏輯領(lǐng)域提供了統(tǒng)一的開放式標(biāo)準(zhǔn)接口。

更高的生產(chǎn)率

通過將多種不同的接口整合到一個(gè)接口(AXI4)中,用戶僅需了解單個(gè)系列的接口即可。

簡(jiǎn)化了不同領(lǐng)域 IP 的集成,并使自身或第三方合作伙伴 IP 的開發(fā)工作更簡(jiǎn)單易行。

由于 AXI4 IP 已為實(shí)現(xiàn)最高性能、最大吞吐量以及最低時(shí)延進(jìn)行了優(yōu)化,從而使設(shè)計(jì)工作進(jìn)一步獲得簡(jiǎn)化。

更大的靈活性

支持嵌入式、DSP 及邏輯版本用戶。

調(diào)節(jié)互連機(jī)制,滿足系統(tǒng)要求:性能、面積及功耗。

幫助您在目標(biāo)市場(chǎng)中構(gòu)建最具號(hào)召力的產(chǎn)品。

廣泛的 IP 可用性

AMD 同 ARM 密切合作,共同為基于 FPGA 的高性能系統(tǒng)和設(shè)計(jì)定義了 AXI4 規(guī)范。作為我們推廣 AXI4 工作的一部分,AMD 已采用 AXI4 作為 UltraScale、7 系統(tǒng)、Zynq 7000、Spartan 6、Virtex 6 以及未來產(chǎn)品系列發(fā)展的新一代 IP 互連標(biāo)準(zhǔn)。

AXI4 目標(biāo)設(shè)計(jì)平臺(tái)幫助客戶加速嵌入式處理、DSP和連接功能設(shè)計(jì)開發(fā)。

AXI4 參考指南可指導(dǎo)用戶向 AXI4 標(biāo)準(zhǔn)過渡。

行業(yè)生態(tài)系統(tǒng)(Ecosystem)支持

第三方 IP 和 EDA 廠商普遍采用開放式 AXI4 標(biāo)準(zhǔn),從而使該接口獲得了更廣泛的應(yīng)用。

Cadence Design Systems, Inc. 、CAST, Inc.、Denali Software、Mentor Graphics Corp.、Northwest Logic、OMIINO ltd.、Sarance Technologies, Inc.、Synopsys, Inc. 以及 Xylon d.o.o. 紛紛宣布支持可滿足 AXI4 接口標(biāo)準(zhǔn)的 IP 及工具。

這能夠確保構(gòu)建基于 AXI4 的系統(tǒng)設(shè)計(jì)能夠獲得強(qiáng)大的行業(yè)生態(tài)系統(tǒng)支持,從而實(shí)現(xiàn)終極生產(chǎn)率,并加速產(chǎn)品上市進(jìn)程。

AXI4 接口的主要優(yōu)勢(shì)

隨著 IP 通用用戶接口普遍采用 AXI4 標(biāo)準(zhǔn),AMD 用戶將從中受益。AXI4 具有:

一致性:所有接口子集都使用相同的傳輸協(xié)議。

全面規(guī)范化:便于客戶采用。

標(biāo)準(zhǔn)化:配套提供標(biāo)準(zhǔn)模型和檢查器以供設(shè)計(jì)人員使用。

接口去耦化:互連電路與接口之間有去耦機(jī)制。

可擴(kuò)展性:AXI4 是一種可滿足未來需求的開放式標(biāo)準(zhǔn)。

其它優(yōu)勢(shì):

支持存儲(chǔ)器映射型和串流型接口。

為通信、視頻、嵌入式以及 DSP 功能提供統(tǒng)一化 IP 接口。

簡(jiǎn)便易用,并具有自動(dòng)流水線例程化等特性,可幫助用戶輕松實(shí)現(xiàn)既定性能目標(biāo)。

諸如 fMAX、LUT 使用、時(shí)延以及帶寬等關(guān)鍵屬性相當(dāng)于或優(yōu)于當(dāng)前的解決方案。

使 AMD 能在所有應(yīng)用領(lǐng)域高效提供增強(qiáng)型本地存儲(chǔ)器、外部存儲(chǔ)器接口以及存儲(chǔ)器控制器解決方案。

AXI 詳情AXI4

AXI4 協(xié)議是 AXI3 的升級(jí),旨在提高多個(gè)主系統(tǒng)使用時(shí)的互連性能和互連利用率。其包括了如下增強(qiáng)功能:

支持高達(dá) 256 個(gè)突發(fā)長(zhǎng)度

服務(wù)質(zhì)量信令

支持多個(gè)區(qū)域接口

AXI4-Lite

AXI4-Lite 是 AXI4 協(xié)議的子集,旨在與組件中較小較簡(jiǎn)單的控制寄存器型接口實(shí)現(xiàn)通信。AXI4-Lite 接口主要特性為:

所有處理的突發(fā)長(zhǎng)度為 1

所有數(shù)據(jù)存取的大小等同于數(shù)據(jù)總線寬度

不支持獨(dú)占訪問

AXI4-Stream

AXI4-Stream 協(xié)議旨在實(shí)現(xiàn)從主系統(tǒng)向從系統(tǒng)進(jìn)行單向數(shù)據(jù)傳輸,從而顯著減少信號(hào)傳輸。該協(xié)議的主要優(yōu)勢(shì)包括:

使用相同的共享線集支持單數(shù)據(jù)流和多數(shù)據(jù)流

在同一互連中支持多數(shù)據(jù)寬度

FPGA 實(shí)現(xiàn)的理想選擇

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

602986 -

嵌入式

+關(guān)注

關(guān)注

5082文章

19104瀏覽量

304804 -

接口協(xié)議

+關(guān)注

關(guān)注

5文章

41瀏覽量

18534 -

AMBA

+關(guān)注

關(guān)注

0文章

68瀏覽量

14980 -

AXI4

+關(guān)注

關(guān)注

0文章

20瀏覽量

8887

原文標(biāo)題:AMBA AXI4 接口協(xié)議

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

看看在SpinalHDL中AXI4總線互聯(lián)IP的設(shè)計(jì)

學(xué)習(xí)架構(gòu)-AMBA AXI簡(jiǎn)介

SoC Designer AXI4協(xié)議包的用戶指南

AMBA 4 AXI4、AXI4-Lite和AXI4-流協(xié)議斷言用戶指南

AMBA 3.0 AXI總線接口協(xié)議的研究與應(yīng)用

AXI4協(xié)議五個(gè)不同通道的握手機(jī)制

FPGA AXI4協(xié)議學(xué)習(xí)筆記(二)

FPGA AXI4協(xié)議學(xué)習(xí)筆記(三)

AXI4-Lite協(xié)議簡(jiǎn)明學(xué)習(xí)筆記

Xilinx FPGA AXI4總線(一)介紹【AXI4】【AXI4-Lite】【AXI-Stream】

漫談AMBA總線-AXI4協(xié)議的基本介紹

Xilinx NVMe AXI4主機(jī)控制器,AXI4接口高性能版本介紹

AMBA AXI4接口協(xié)議概述

AMBA AXI4接口協(xié)議概述

評(píng)論