聯華電子(UMC,TWSE: 2303)與ASIC設計服務暨IP研發銷售廠商智原科技(Faraday Technology Corporation,TWSE:3035)今日共同發表智原科技于聯電55納米超低功耗工藝(55ULP)的 PowerSlash 基礎IP方案。智原 PowerSlash 與聯電工藝技術相互結合設計,為超低功耗的無線應用需求技術進行優化,滿足無線物聯網產品的電池長期壽命需求。

智原科技營銷暨投資副總于德洵表示:“物聯網應用建構過程中,效能往往受制于低功耗技術。而今透過聯電55納米超低功耗技術以及智原 PowerSlash IP 的加速模式(Turbo Mode)功能,為物聯網應用環境帶來至關重要的解決方案,除了省電更提供絕佳的效能。再次,聯電和智原共同締造了成功的芯片服務技術。”

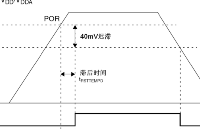

智原 PowerSlash IP 包含多重臨界電壓組件庫、內存編譯器和電源管理組件,能夠充分利用聯電 55ULP 的優勢在0.81V至1.32V廣域電壓下運作。此外,新的加速模式功能可以有效調升性能曲線,幫助 MCU 核心達到2倍效能,在相同額定頻率下減少約40%的動態功耗。

聯電硅智財研發暨設計支持處的莫亞楠資深處長也表示: “ 物聯網芯片設計師對于有效的節能解決方案有高度的需求。聯電擁有晶圓代工業界中最健全的物聯網專屬55納米技術平臺,結合完整的硅智財方案,可以支持物聯網產品的不間斷低功耗要求。藉由智原在我們的 55ULP 平臺上發表的 PowerSlash IP,能夠讓客戶使用完善的工藝平臺,協助提供物聯網產品的獨特需求。”

PowerSlash IP 結合智原的低功耗設計系統、系統芯片超低功耗控制組件與 FIE3200 FPGA 平臺,可以使用在低功耗集成電路的前端設計或后端開發階段。聯電的 55ULP 技術能夠支持較低的操作電壓及 sub-pA 裝置漏電,為含有鈕扣電池的產品提供理想的的晶圓工藝。智原與聯電合力的超低功耗解決方案,為超低功耗集成電路設計平臺帶來新的基準。

-

物聯網

+關注

關注

2930文章

46201瀏覽量

391710 -

IP

+關注

關注

5文章

1802瀏覽量

152448 -

聯華電子

+關注

關注

0文章

56瀏覽量

16958

發布評論請先 登錄

評論