積分電路 Integrator circuit

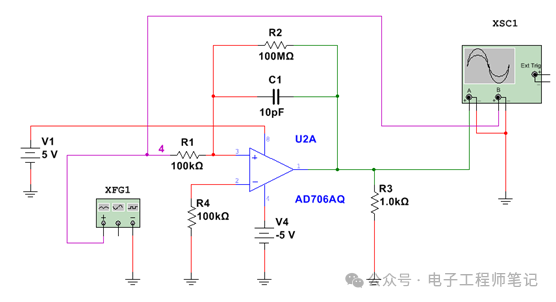

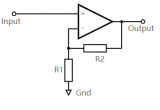

在運算放大器積分器電路中,電容器插入反饋環路中,并在反相輸入端與R1一起產生一個RC時間常數。

積分的物理意義

積分的物理意義我們經常會使用到,例如下面的幾個例子。

1、加速度對時間的積分就是速度;

2、速度對時間的積分就是路程;

3、功率對時間的積分就是功。

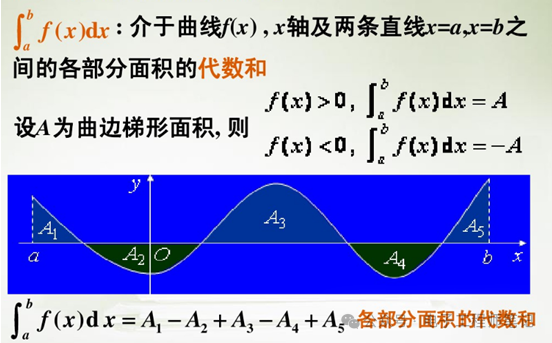

積分的幾何意義

幾何意義來自于我們的數學基礎概念,比如幾何處理等問題,如下所示。

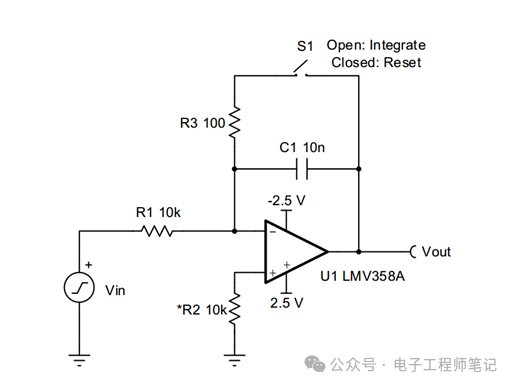

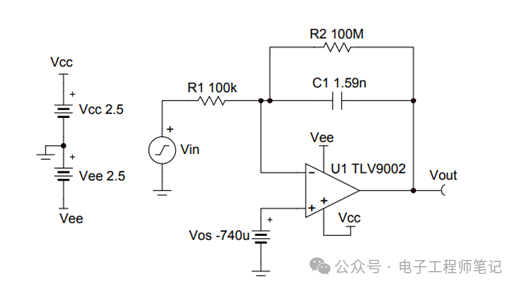

積分電路

積分器電路根據電路時間常數和放大器的帶寬,在一個頻率范圍內輸出輸入信號的積分。

輸入信號被施加到反相輸入,因此輸出相對于輸入信號的極性反相。理想的積分器電路將飽和到電源軌,具體取決于輸入失調電壓的極性并需要增加一個反饋電阻R2,以提供穩定的直流工作點。反饋電阻器限制了執行積分功能的較低頻率范圍。

設計須知

1.對于反饋電阻,請使用盡可能大的值。

2.選擇一個CMOS運算放大器,以最小化輸入偏置電流的誤差。

3.放大器的增益帶寬積(GBP)將設置積分器功能的上限頻率。

集成功能的有效性通常在距放大器帶寬約十年的時間開始降低。

4.需要將一個可調基準電壓連接到運算放大器的同相輸入,以消除輸入失調電壓,否則較大的DC噪聲增益將導致電路飽和。具有非常低的失調電壓的運算放大器可能不需要這樣做。

積分電路如下所示:

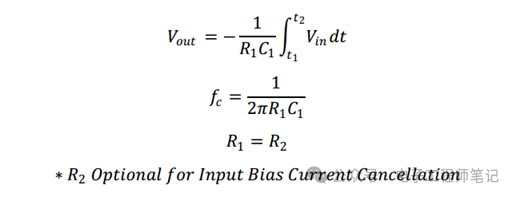

積分電路計算

積分電路輸出電壓Vout計算

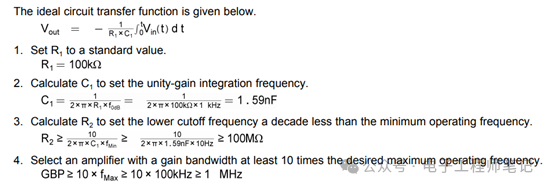

如何設計

1、我們需要先設定電阻值,即就是上圖中的R1;

2、計算C1以設置單位增益積分頻率。

3、計算R2將下限截止頻率設置為比最小工作頻率低十倍。

4、選擇增益帶寬至少為所需最大工作頻率的10倍的放大器。

增益帶寬積

假設運算放大器的增益帶寬積為1 MHz,它意味著當頻率為1 Mhz時,器件的增益下降到單位增益。即此時A=1。同時說明這個放大器最高可以以1 MHz的頻率工作而不至于使輸入信號失真。由于增益與頻率的乘積是確定的,因此當同一器件需要得到10倍增益時,它最高只能夠以100 kHz的頻率工作。

單位增益帶寬

單位增益帶寬定義為,運放的閉環增益為1倍條件下,將一個頻率可變恒幅正弦小信號輸入到運放的輸入端,隨著輸入信號頻率不斷變大,輸出信號增益將不斷減小,當從運放的輸出端測得閉環電壓增益下降3db(或是相當于運放輸入信號的0.707)時,所對應的信號頻率乘以閉環放大倍數1所得的增益帶寬積。

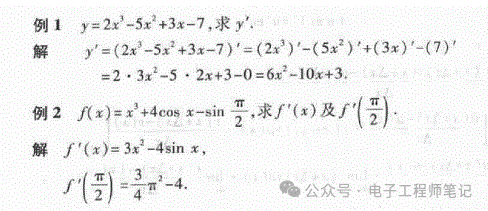

導數的運算

因為我們在高等數學里面是先講到的導數相關運算,再講述的是積分運算。

簡單函數:

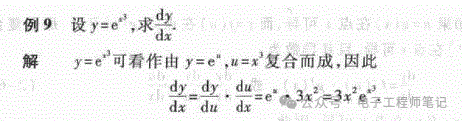

復合函數:

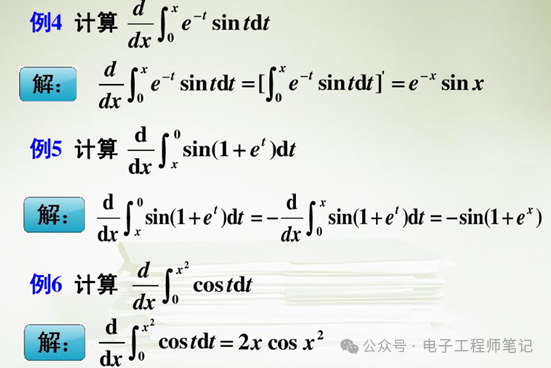

積分的運算

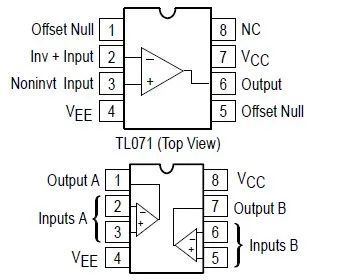

VOS 輸入失調電壓

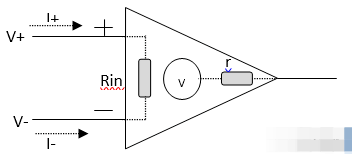

輸入失調電壓定義為集成運放輸出端電壓為零時。兩個輸入端之間所加的補償電壓。輸入失調電壓實際上反映了運放內部的電路對稱性。對稱性越好。輸入失調電壓越小。輸入失調電壓是運放的一個十分重要的指標,特別是精密運放或是用于直流放大時。輸入失調電壓與制造工藝有一定關系。當中雙極型工藝(即上述的標準硅工藝)的輸入失調電壓在±1~10mV之間。

IB 輸入偏置電流

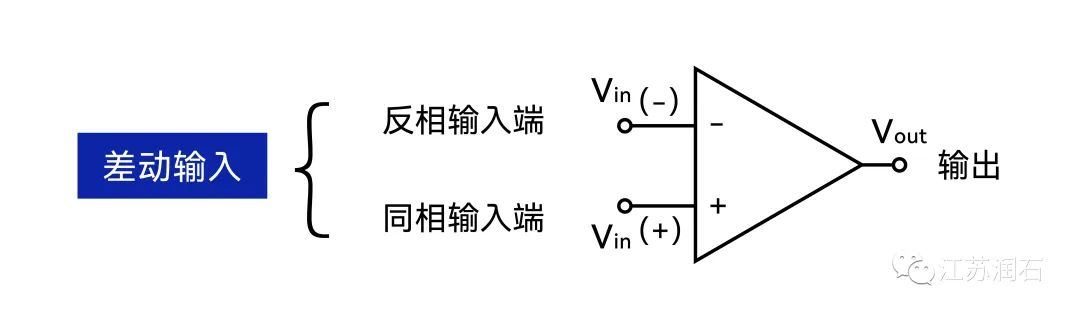

運放兩個輸入端偏置電流的平均值, 確切地說是運算放大器工作在線性區時流入輸入端的平均電流。用于衡量差分放大對管輸入電流的大小。

IOS 輸入失調電流

在零輸入時,差分輸入級的差分對管基極電流之差,II0=|IB1-IB2|。用于表征差分級輸入電流不對稱的程度。通常,Ios為(0.5~5)nA,高質量的可低于 1nA。

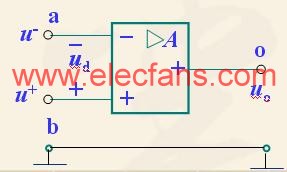

AOL 開環電壓增益

開環電壓增益參數Aol被定義為輸出電壓的改變量與兩個輸入端之間電壓該變量之比。

運算放大器的靜態輸入指標及動態技術指標:輸入失調電壓、輸入失調電流、輸入偏置電流、共模抑制比、單位增益帶寬、轉換速率、壓擺率、輸入阻抗、輸出阻抗。

積分電路的應用:

1、積分電路可以使輸入方波轉換成三角波或者斜波;

2、積分電路電阻串聯在主電路中,電容在干路中;

3、積分電路的時間常數t要大于或者等于10倍輸入脈沖寬度;

4、積分電路輸入和輸出成積分關系

積分電壓波形

我們經常所了解到的方波轉為三角波;

R2如果不增加將會導致輸出出現積分飽和,也就是電容無法放電,導致輸出異常甚至可能達到和供電電源一樣的電壓,因此需要增加這個大的并聯電容;

積分電路分析分析

如果現在施加到Vin的方波進入其正半周期并在Vin處產生穩定的正DC電壓,則電流將流過R1并開始對C1充電。

由于R1和C1的交界處的電壓(LM324的反相輸入)保持在虛擬地,因此,運放輸出(連接至C1的右面板)的電壓將開始以一定速率下降由CR時間常數控制。

輸出電壓將繼續下降,試圖達到一個等于Vin且與Vin相反的負電壓。此動作導致輸出端出現相對線性的負向斜率,直到(遠在一個時間常數結束之前),輸入方波突然改變極性。

在輸入方波的負向半周期開始時將Vin的電壓更改回較低的水平將導致C1開始放電,并將反相輸入保持在0V,運算放大器輸出的電壓將開始以線性方式增加。

這一直持續到下一個周期開始時輸入突然再次變為正。

為了在輸出三角波形上產生線性斜坡,積分器電路的CR時間常數應類似于或長于輸入波周期時間的一半。

在圖所示的情況下,時間常數R1 x C1(100exp3 x 10exp-9)= 220μs將周期為1 / 2exp3Hz = 500μs / 2 = 250μs的1kHz方波轉換為合理的線性三角波波。

-

CMOS

+關注

關注

58文章

5710瀏覽量

235416 -

運算放大器

+關注

關注

215文章

4929瀏覽量

172839 -

積分電路

+關注

關注

11文章

85瀏覽量

36967 -

積分器

+關注

關注

4文章

100瀏覽量

28444

原文標題:運算放大器積分電路及積分電路設計

文章出處:【微信號:電子工程師筆記,微信公眾號:電子工程師筆記】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

運算放大器的工作原理和基本電路 使用運算放大器的電路設計

求帶有微分積分電路的運算放大器接三極管分析

運算放大器權威指南和基于運算放大器和模擬集成電路的電路設計及OP放大器應用技巧100例PDF分享

求助運算放大器PID電路應該怎樣調節積分電路

【專輯精選】電路設計之運算放大器設計學習資料匯總

如何設計運算放大器 運算放大器同相放大器電路設計技巧有哪些

運算放大器積分電路設計

運算放大器積分電路設計

評論