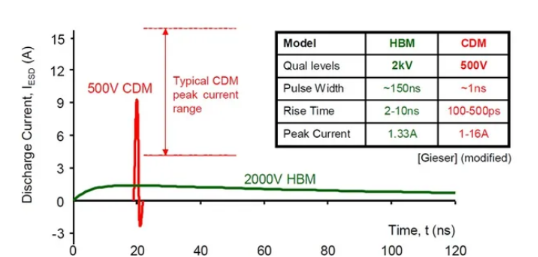

CDM(Charged Device Model)作為一種獨(dú)特的ESD(Electrostatic Discharge)模擬方式,與HBM(Human Body Model)和MM(Machine Model)有所區(qū)別。此模型專(zhuān)注于模擬電子設(shè)備在生產(chǎn)或物流環(huán)節(jié)中積累的靜電,在接觸地面或其他導(dǎo)電物體時(shí)引發(fā)的快速電荷釋放現(xiàn)象。CDM放電事件的特點(diǎn)是極其迅速的電流上升階段,通常在0.1至0.5納秒之間,整個(gè)放電過(guò)程大約持續(xù)6至8納秒,其電流峰值相較于HBM模型在相同ESD條件下可達(dá)到數(shù)倍之高。

在金鑒實(shí)驗(yàn)室,我們了解CDM模型對(duì)于電子元件的重要性,以及其與其他放電模型的區(qū)別。我們提供專(zhuān)業(yè)的ESD測(cè)試服務(wù),包括針對(duì)CDM模型的測(cè)試,以確保電子元件在面臨靜電放電時(shí)的可靠性和穩(wěn)定性。通過(guò)我們的測(cè)試和評(píng)估,客戶(hù)可以更好地了解其產(chǎn)品在實(shí)際應(yīng)用中可能遇到的挑戰(zhàn),并采取相應(yīng)的措施來(lái)保護(hù)其設(shè)備免受ESD損害。

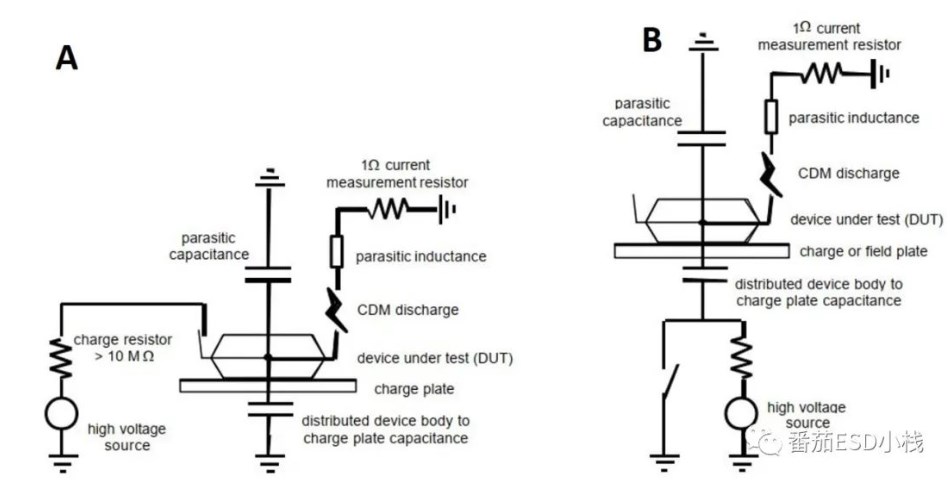

CDM測(cè)試裝置

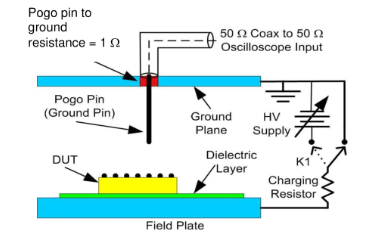

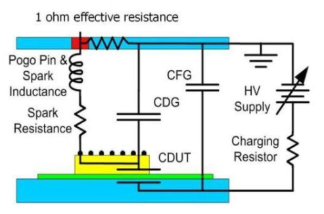

CDM測(cè)試裝置主要由一個(gè)與高壓電源相連的充電板Field Plate和一個(gè)接地的Pogo pin構(gòu)成,Pogo pin能夠在待測(cè)IC(DUT)的引腳間移動(dòng),以模擬實(shí)際的ESD事件。圖1展示了實(shí)際的測(cè)試模塊,而圖2則為等效電路圖,其中CDUT代表DUT與場(chǎng)板之間的電容,CDG代表DUT與地平面之間的電容,CFG代表場(chǎng)板與地平面之間的電容。

圖1:實(shí)際測(cè)試各模塊

圖2:等效電路(CDUT是DUT和場(chǎng)板間的電容,CDG是DUT和地平面間的電容,CFG是場(chǎng)板和地平面間電容。)

CDM測(cè)試規(guī)范

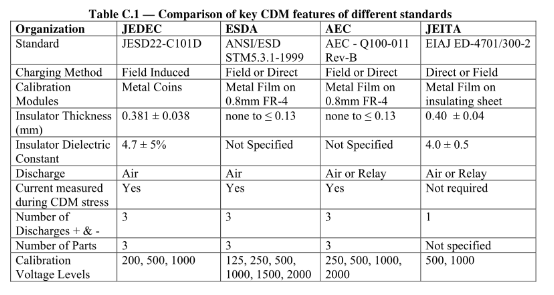

在CDM測(cè)試規(guī)范統(tǒng)一化之前,存在多個(gè)參考標(biāo)準(zhǔn),包括JESD22-C101、ESDA S5.3.1、AEC Q100-011和EIAJ ED-4701/300-2等,這些標(biāo)準(zhǔn)在校準(zhǔn)平臺(tái)、示波器帶寬和波形驗(yàn)證參數(shù)等方面存在差異。金鑒實(shí)驗(yàn)室緊跟行業(yè)動(dòng)態(tài),能夠根據(jù)客戶(hù)需求提供符合不同標(biāo)準(zhǔn)的定制化測(cè)試服務(wù),確保客戶(hù)產(chǎn)品的合規(guī)性。

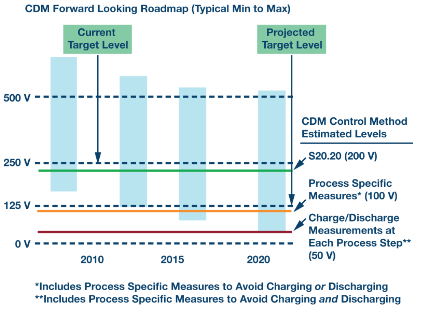

技術(shù)進(jìn)步帶來(lái)了晶體管性能的提升和更高的IO性能需求。隨著IC芯片對(duì)高速I(mǎi)O的需求增加,以及在單一封裝中集成更多功能的趨勢(shì),封裝尺寸的增加對(duì)維持JEP157中推薦的CDM放電級(jí)別提出了挑戰(zhàn)。考慮到不同測(cè)試設(shè)備的充電電阻差異,ESD協(xié)會(huì)(ESDA)在2020年的路線(xiàn)圖中建議可能需要重新評(píng)估CDM放電目標(biāo)級(jí)別。

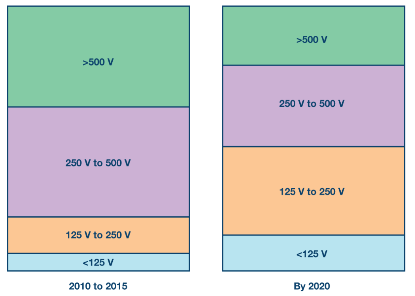

隨著電子設(shè)備性能的提高,對(duì)ESD保護(hù)的需求也在增加,金鑒實(shí)驗(yàn)室提供專(zhuān)業(yè)的ESD測(cè)試服務(wù),幫助客戶(hù)評(píng)估其產(chǎn)品在靜電放電環(huán)境下的表現(xiàn),并根據(jù)最新的標(biāo)準(zhǔn)和建議提供定制化的解決方案。通過(guò)金鑒的測(cè)試服務(wù),客戶(hù)能夠更準(zhǔn)確地掌握產(chǎn)品的ESD性能,確保產(chǎn)品在實(shí)際使用中的可靠性和穩(wěn)定性。如圖3和圖4所示,分別展示了歷年CDM放電目標(biāo)級(jí)別的變化和CDM ESD目標(biāo)級(jí)別的預(yù)期分布變化。

圖3:歷年來(lái)CDM放電的目標(biāo)級(jí)別

圖4:CDM ESD目標(biāo)級(jí)別的分布預(yù)期的變化

CDM測(cè)試標(biāo)準(zhǔn)調(diào)整的原因

金鑒實(shí)驗(yàn)室在此領(lǐng)域的深厚積累,使我們能夠?yàn)榭蛻?hù)提供專(zhuān)業(yè)的建議和解決方案,幫助他們?cè)诿鎸?duì)新標(biāo)準(zhǔn)時(shí),及時(shí)調(diào)整產(chǎn)品設(shè)計(jì)和測(cè)試策略。JEP157標(biāo)準(zhǔn)中對(duì)CDM放電能力要求的降低反映了幾個(gè)關(guān)鍵因素:

1. IC元件引腳數(shù)量和封裝尺寸的顯著增加

在固定的預(yù)充電壓下,限制了芯片的CDM放電能力,尤其是封裝尺寸。引腳數(shù)量和封裝尺寸的增加意味著IC能夠存儲(chǔ)更多的電荷,導(dǎo)致CDM放電時(shí)峰值電流迅速上升。因此,在相同的峰值電流限制下,引腳數(shù)量和尺寸的增加會(huì)導(dǎo)致CDM能力的降低。

2. IC工藝技術(shù)的進(jìn)步導(dǎo)致CDM放電能力的降低

隨著工藝尺寸的縮小,CDM放電能力顯著降低。工藝尺寸的縮小使得有源器件變得更小、更脆弱,金屬互連變得更薄、電阻性增加,降低了ESD保護(hù)電路的魯棒性。這使得在相同的電流水平下,實(shí)現(xiàn)CDM保護(hù)變得更加困難。

3. 隨著高速數(shù)字、射頻模擬和其他性能敏感引腳的混合信號(hào)IC變得更加普遍,對(duì)ESD保護(hù)提出了新的要求

在高頻電路中,直接將ESD保護(hù)器件連接到I/O引腳可能會(huì)導(dǎo)致射頻功能的顯著降低,因此需要將射頻保護(hù)結(jié)構(gòu)與核心電路隔離。這通常通過(guò)在ESD保護(hù)器件和引腳之間插入并聯(lián)電感/電容網(wǎng)絡(luò)來(lái)實(shí)現(xiàn),該網(wǎng)絡(luò)在低頻ESD事件中提供接近零的阻抗,在正常高頻操作中提供高阻抗。金鑒實(shí)驗(yàn)室致力于為客戶(hù)提供專(zhuān)業(yè)的ESD測(cè)試服務(wù),幫助他們理解和評(píng)估其產(chǎn)品在面對(duì)靜電放電時(shí)的表現(xiàn),并提供針對(duì)性的解決方案,以確保其產(chǎn)品具有足夠的可靠性和穩(wěn)定性。

-

ESD

+關(guān)注

關(guān)注

48文章

2029瀏覽量

172929 -

CDM

+關(guān)注

關(guān)注

0文章

30瀏覽量

12234 -

模擬電子

+關(guān)注

關(guān)注

58文章

660瀏覽量

81722

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

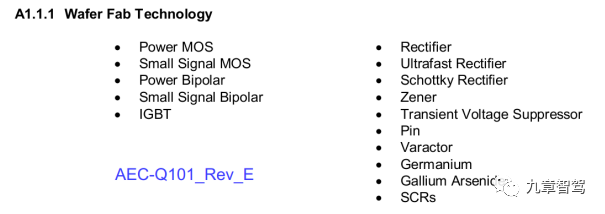

車(chē)電零部件可靠性驗(yàn)證(AEC-Q)

AEC-Q100汽車(chē)級(jí)驅(qū)動(dòng)器

哪些組件需要AEC-Q200標(biāo)準(zhǔn)

什么是AEC-Q100認(rèn)證?

什么是小尺寸集成電路CDM測(cè)試?

AEC-Q103測(cè)試標(biāo)準(zhǔn)解讀

小尺寸集成電路CDM測(cè)試

AEC Q102(一文讀懂車(chē)規(guī)級(jí)AEC-Q認(rèn)證)

CDM的測(cè)試與失效分析

功率器件AEC-Q101如何選擇測(cè)試項(xiàng)目?認(rèn)證準(zhǔn)備及流程有哪些?

車(chē)規(guī)芯片的AEC-Q100測(cè)試標(biāo)準(zhǔn)

AEC-Q100 H版標(biāo)準(zhǔn)學(xué)習(xí)

關(guān)于汽車(chē)電子AEC-Q200測(cè)試,您了解哪些?

什么是AEC-Q-CDM測(cè)試?

什么是AEC-Q-CDM測(cè)試?

評(píng)論