以下文章來源于ExASIC,作者陳鋒

介紹幾種自動生成verilog代碼的方法。

f = open('mytest.v', 'w')

# rtl = ...

f.write(rtl)

說明:這種方法相當簡單樸素,python做出需要的字符串,寫到文件。好處是不需要技巧,壞處是python代碼可維護性較差。

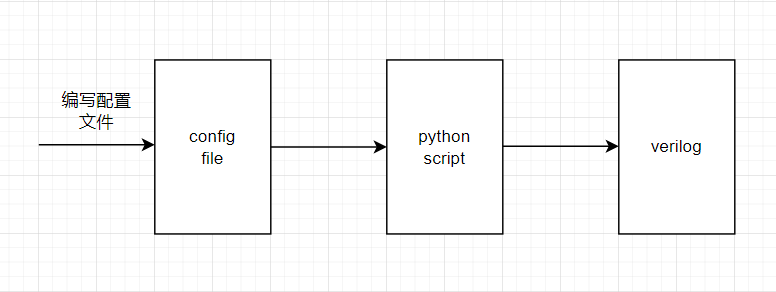

第二種:讀配置文件再生成

與第一種的差異是,把各種可配置的信息存到配置文件里,如excel、json、yaml,在腳本里讀取配置文件再用第一種方法生成字符串。

這種方法的好處是腳本相對固定,只需要修改配置文件就可以重新生成verilog代碼。但python腳本還是相對較亂,因為從配置參數到目標verilog中間需要各種字符串處理,如正則替換,format,進制轉換等。當目標verilog的格式要求一變,python腳本還是需要重寫。

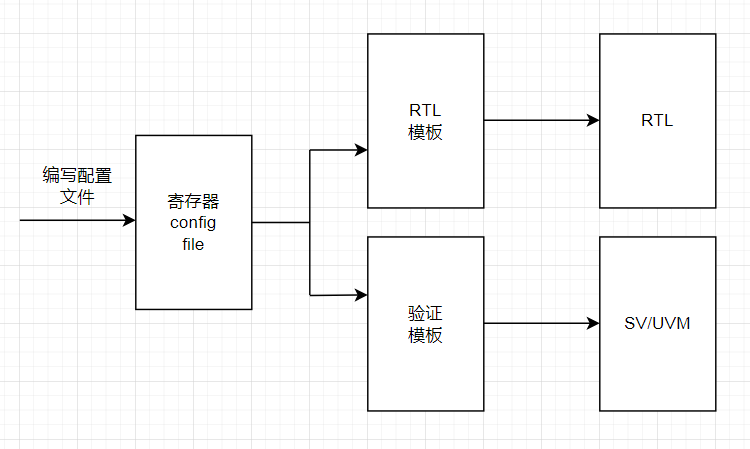

第三種:利用模板語言

現在我們來利用模板語言,比如jinja2,(https://docs.jinkan.org/docs/jinja2),把配置參數與目標verilog格式拆分開來。

如下圖,有兩個模板,RTL模板和驗證模板,用同一個配置參數經過不同的模板,就可以得到不同的代碼。配置參數與模板轉換的過程是由模板引擎來實現,不需要我們再重新造輪子。

這種方法的好處是只需要把精力花了編寫模板身上,而其它部分都是由現成的庫來實現,這樣就只需要寫很少量的python代碼了。缺點是這種模板語言與Verilog語言本身有比較大的差異,需要稍微學習一下。

第四種:Verilog里內嵌python

在Verilog代碼注釋里嵌入幾行python代碼,而保持大部分Verilog不動。比如下面的例子:

always@(posedge clk, negedge rst_n) if(!rst_n) q[7:0] <= 8'b0; else begin // PYTHON_BEGIN // import random // data = [] // for i in range(8) // data.append(random.randint(0, 1)) // for i in range(8): // print('q[{}]'.format(data[i])) // PYTHON_END end

可見,這串代碼的注釋中用PYTHON_BEGIN和PYTHON_END括起了一段python代碼。我們需要提取出這段python,把python的執行結果替換到原處。

當然為了保證代碼可以再次生成,我們不能刪除python源碼,而是需要在注釋下方生成。重新生成時會先刪除PY_VLG_BEGIN和PY_VLG_END之間的verilog代碼。

always@(posedge clk, negedge rst_n)

if(!rst_n)

q[7:0] <= 8'b0;

else begin

// PYTHON_BEGIN

// import random

// data = []

// for i in range(8)

// data.append(random.randint(0, 1))

// for i in range(8):

// print('q[{}] <= {};'.format(i, data[i]))

// PYTHON_END

// PY_VLG_BEGIN

q[0] <= 0;

q[1] <= 1;

q[2] <= 0;

q[3] <= 0;

q[4] <= 1;

q[5] <= 1;

q[6] <= 1;

q[7] <= 0;

// PY_VLG_END

end

這個“提取->執行->替換”的腳本具有通用性,編寫起來比較簡單。不需要頻繁修改。

當verilog里內嵌的python功能接近,或者有共性時,就可以把這種處理函數寫到一個py庫里,用時import進來。

優勢:只需要維護一份verilog文件(不需要額外的python腳本了),對設計工程師友好。缺點:每個公司都需要建立自己的共用py庫,當庫越來越龐大時,新人或者換工作后就需要重新學習或者重新零開始。

第五種:第四種基礎上把常用規則提煉,做成開源工具

每個人單獨搞一套就會變得不可持續。可以以開源項目的方式,愛好者共同開發和維護,不斷迭代,形成行業規范。例如:HDLGen(https://github.com/WilsonChen003/HDLGen)。

但很可能貢獻者有限,停止維護,慢慢荒廢。

第六種:利用DSL來編寫代碼

比如SpinalHDL(https://thucgra.github.io/SpinalHDL_Chinese_Doc)、Chisel(https://www.chisel-lang.org)這種基于Scala的硬件開發工具。優點:有規范,行業標準。缺點:創新得太徹底,學習成本非常高,遇到問題很難找到地方咨詢。并與現有的Verilog開發流程差異較大,DSL自成一套設計和驗證的方法。

-

Verilog

+關注

關注

28文章

1351瀏覽量

110074 -

字符串

+關注

關注

1文章

578瀏覽量

20506 -

代碼

+關注

關注

30文章

4779瀏覽量

68521 -

python

+關注

關注

56文章

4792瀏覽量

84627

原文標題:幾種自動生成verilog代碼的方法

文章出處:【微信號:芯司機,微信公眾號:芯司機】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

LFSR代碼自動生成工具v1.20 beta

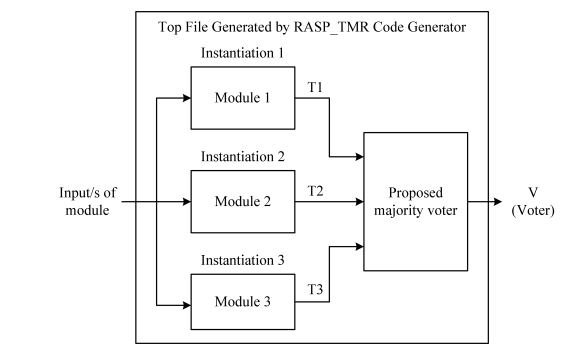

用于實現和評估TMR方法的自動快速可綜合Verilog代碼生成器工具介紹

如何自動生成verilog代碼

如何自動生成verilog代碼

評論