以下文章來(lái)源于OpenFPGA,作者碎碎思

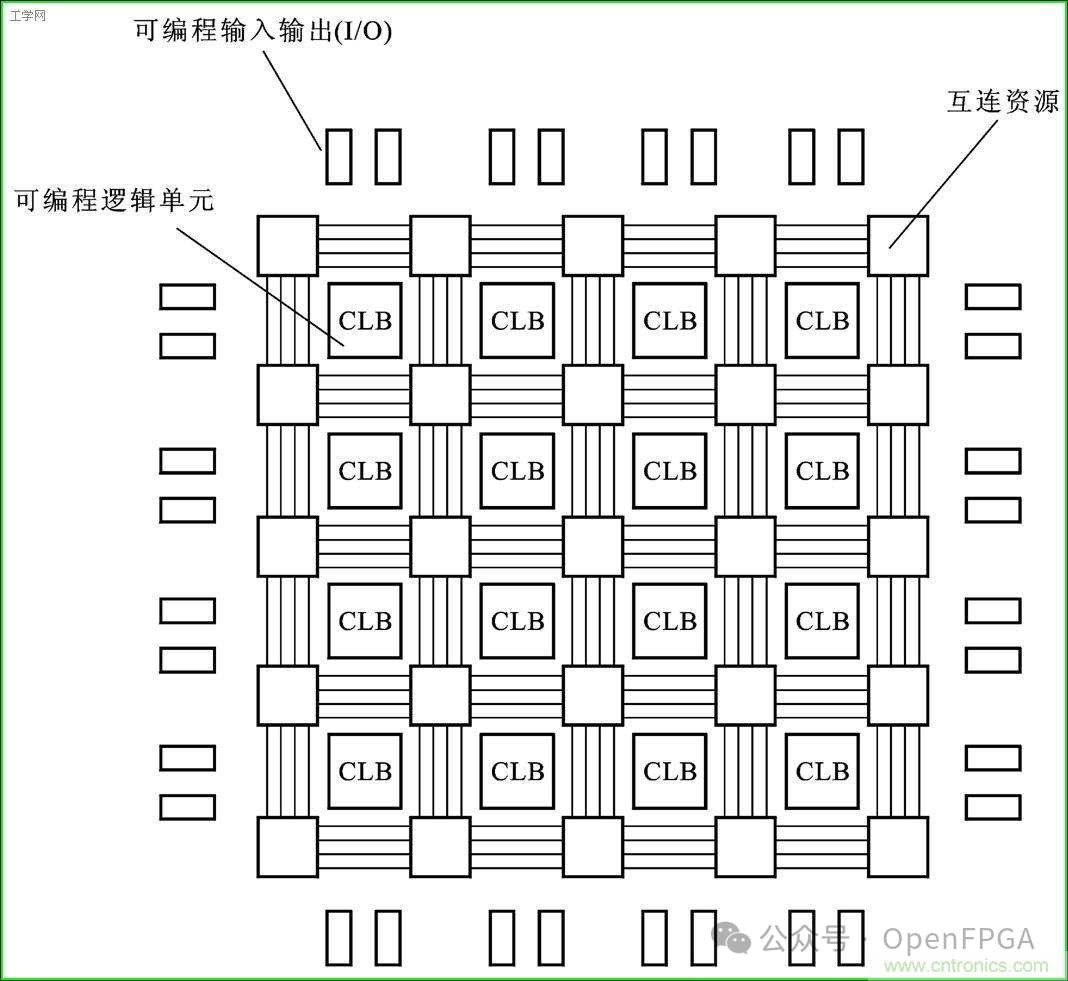

FPGA 允許在單個(gè)芯片中實(shí)現(xiàn)大量數(shù)字邏輯,其運(yùn)行速度相對(duì)較高,并且只需很少或不需要在 CPU 內(nèi)核上運(yùn)行的傳統(tǒng)順序程序即可完成其工作。

這種數(shù)字邏輯可以實(shí)現(xiàn)任何東西,從簡(jiǎn)單的UART到由數(shù)十個(gè)CPU內(nèi)核組成的架構(gòu),每個(gè)CPU內(nèi)核都運(yùn)行自己的小程序,并在共享任務(wù)上相互通信。或者,它可以是幾組不同的邏輯在處理完全獨(dú)立的任務(wù),這些任務(wù)彼此之間可以沒(méi)有關(guān)系。

1、數(shù)字邏輯實(shí)現(xiàn)

基本上,F(xiàn)PGA 允許放置下圖中所有這些較小的黑色芯片:

只需 1 個(gè)芯片,就可以立即使用新設(shè)計(jì)以任何想要的方式重新連接所有這些芯片。誠(chéng)然,設(shè)計(jì)過(guò)程是......比較困難!

FPGA 擅長(zhǎng)同時(shí)執(zhí)行多項(xiàng)任務(wù),可以將該功能實(shí)現(xiàn)為單獨(dú)的數(shù)字邏輯,從最簡(jiǎn)單的組合邏輯一直到復(fù)雜的 CPU 處理器。除了邏輯元件的數(shù)量和它們之間的互連之外,幾乎沒(méi)有什么限制。

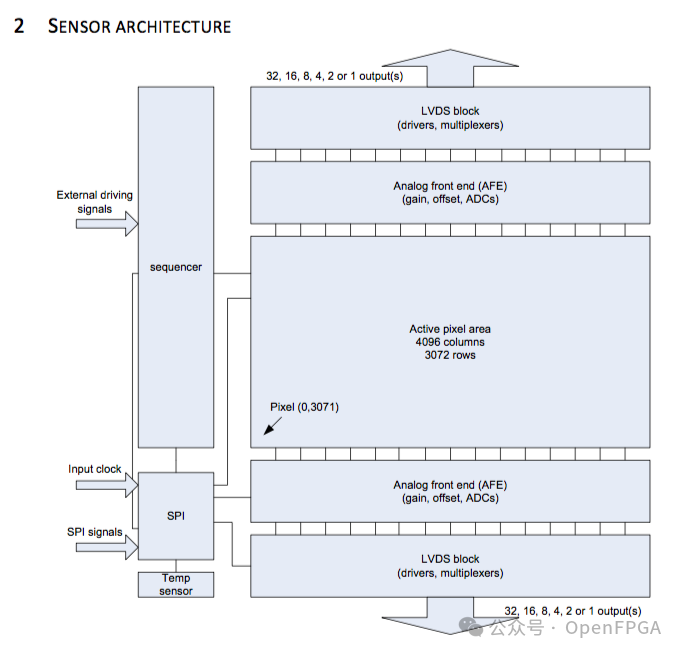

2、高速率高帶寬數(shù)據(jù)處理

一個(gè)典型的例子:

看到頂部和底部有多達(dá) 32 個(gè) LVDS 串行輸出。

LVDS信號(hào)是串行數(shù)據(jù)的一對(duì)差分線(用于獲得高速和抗噪性)。圖像數(shù)據(jù)將從每個(gè)LVDS對(duì)中輸出。

這種高速串行輸出數(shù)據(jù)的原因是為了讓整個(gè)圖像盡快從傳感器中取出,并進(jìn)入后續(xù)處理階段(可能在FPGA中)。完成此操作的速度越快,幀速率就越高。如果想要一個(gè)能夠達(dá)到 120fps 幀速率的運(yùn)動(dòng)相機(jī),那么就需要將整個(gè)幀數(shù)據(jù)輸出 - 在以 18 位分辨率模式運(yùn)行時(shí),此傳感器為單幀數(shù)據(jù)量為 12 MB - 每秒 120 幀,超過(guò) 2 GBytes/s 的數(shù)據(jù)量!

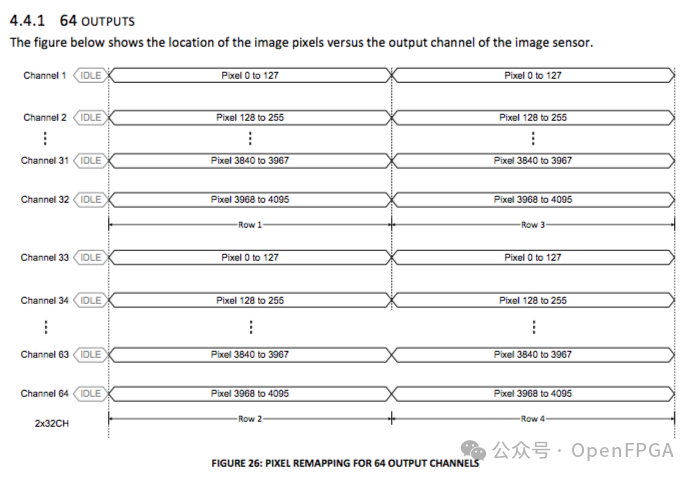

實(shí)現(xiàn)這一目標(biāo)的一種方法是使用大量LVDS輸出,并將每個(gè)輸出分配給幀的特定部分。這基本上是“分而治之”。

問(wèn)題在于,接收數(shù)據(jù)后需要重組這些LVDS數(shù)據(jù),組成一個(gè)圖像傳感器的一幀數(shù)據(jù)。唯一可行的方法是在硬件中實(shí)現(xiàn),因?yàn)椋海╝)沒(méi)有微控制器/處理器具有那么多串行LVDS,(b)即使有,處理負(fù)擔(dān)也會(huì)很大,并且可能永遠(yuǎn)無(wú)法達(dá)到所需的幀速率。

這只是使用FPGA的一個(gè)“經(jīng)典”示例,它將來(lái)自每個(gè)LVDS輸入的所有數(shù)據(jù)重新組合到圖像的單個(gè)相干幀中。然而,它并沒(méi)有就此結(jié)束。后續(xù)的ISP處理等操作都可以在同一個(gè)FPGA中進(jìn)行。

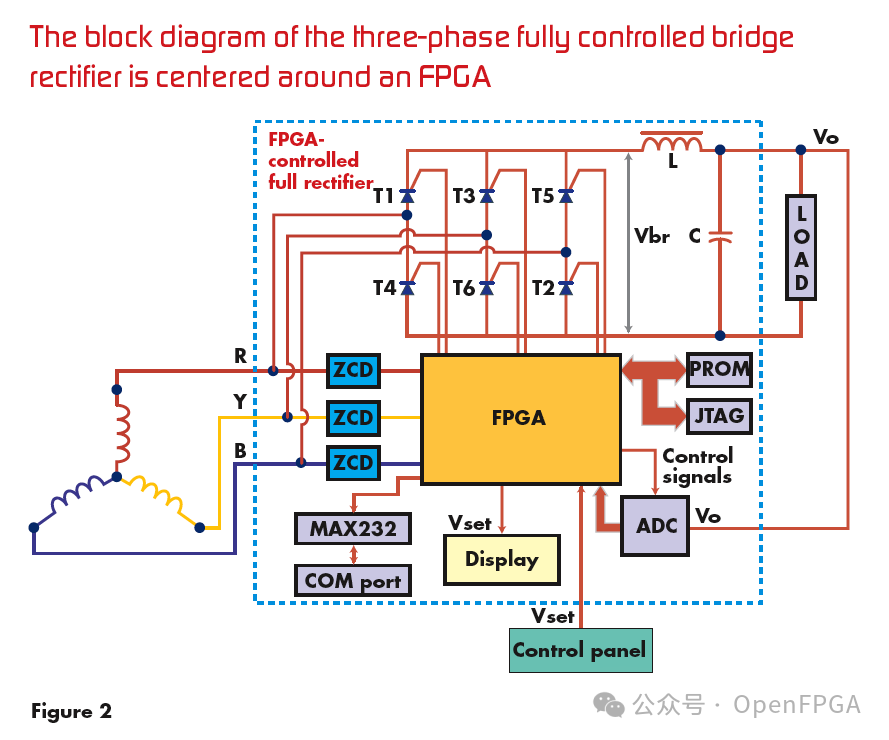

3、保證時(shí)間精確控制

FPGA的另一個(gè)重要用途:在需要“保證”響應(yīng)的情況下,或者需要確定地滿足“硬”時(shí)序約束。實(shí)時(shí)控制系統(tǒng)的挑戰(zhàn)之一是保證實(shí)際上能夠滿足這些時(shí)間限制。

在大多數(shù)通過(guò)微處理器/微控制器上的順序編程實(shí)現(xiàn)的非平凡的控制系統(tǒng)中,有時(shí)主要“應(yīng)用程序”會(huì)被中斷,要么是切換到其他輔助任務(wù),要么是處理 I/O 中斷,尤其是需要大量計(jì)算資源且自身具有時(shí)序限制的現(xiàn)代通信協(xié)議。由于所有這些其他任務(wù)和職責(zé)都在爭(zhēng)奪 CPU 時(shí)間,嵌入式系統(tǒng)開(kāi)發(fā)人員已經(jīng)提出了幾種技術(shù)來(lái)應(yīng)對(duì)這些挑戰(zhàn),但是順序編程系統(tǒng)可以實(shí)現(xiàn)的功能是有限的。

FPGA 是專用電路、狀態(tài)機(jī)以及控制和數(shù)據(jù)流“編程”的絕佳解決方案,精度低至納秒級(jí),幾乎沒(méi)有系統(tǒng)“錯(cuò)過(guò)”事件或不符合設(shè)計(jì)時(shí)序約束的風(fēng)險(xiǎn)。

一個(gè)常見(jiàn)示例是通過(guò)多相電機(jī)或橋式整流器進(jìn)行相位控制或PWM控制,或使用H橋晶體管驅(qū)動(dòng)器配置時(shí)進(jìn)行的。

在這些場(chǎng)景中,不僅可以以數(shù)十kHz甚至高達(dá)MHz的速度開(kāi)關(guān)電源,而且還可能根據(jù)其他控制信號(hào)調(diào)制PWM - 可能是一組3個(gè)正弦波,用于三相對(duì)準(zhǔn),在這種情況下,需要相對(duì)PWM時(shí)序的精細(xì)分辨率。

在FPGA中實(shí)現(xiàn)這種控制可以滿足非常精細(xì)的時(shí)序約束。

4、其他

FPGA 還有無(wú)數(shù)其他用途。

就在我常用的一種工具-Saleae邏輯分析儀:

Xilinx Spartan 6 FPGA 執(zhí)行所有高速工作,捕獲其數(shù)字輸入的時(shí)間序列狀態(tài),然后通過(guò) USB 將其發(fā)送到PC。通過(guò)在 PC 上的分析來(lái)查找自己的數(shù)字電路設(shè)計(jì)中的錯(cuò)誤。

數(shù)據(jù)中心:

在過(guò)去的幾年里,微軟、亞馬遜和谷歌在云服務(wù)器基礎(chǔ)設(shè)施中使用FPGA引起了很多關(guān)注,其中每個(gè)服務(wù)器都有一個(gè)FPGA,允許一些傳統(tǒng)上通過(guò)線性編程完成的計(jì)算任務(wù),在專用的定制FPGA數(shù)字邏輯中完成。

這使得服務(wù)器可以相對(duì)快速且輕松地重新配置,以便針對(duì)在其上運(yùn)行的特定應(yīng)用程序進(jìn)行優(yōu)化。這些應(yīng)用程序可以是加密計(jì)算,或是OpenCV視覺(jué)算法,或是AI/ML推理,或是復(fù)雜的網(wǎng)絡(luò)數(shù)據(jù)包過(guò)濾,或者其他我們不知道的操作!

最后,F(xiàn)PGA 通常被用作原型設(shè)計(jì)的一種方式,該設(shè)計(jì)最終將被“鎖定”到自己的IC芯片設(shè)計(jì)中。

本文轉(zhuǎn)載自O(shè)penFPGA公眾號(hào)

-

處理器

+關(guān)注

關(guān)注

68文章

19259瀏覽量

229651 -

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

602986 -

芯片

+關(guān)注

關(guān)注

455文章

50714瀏覽量

423137 -

內(nèi)核

+關(guān)注

關(guān)注

3文章

1372瀏覽量

40276 -

cpu

+關(guān)注

關(guān)注

68文章

10854瀏覽量

211576

原文標(biāo)題:FPGA可以解決哪些問(wèn)題?

文章出處:【微信號(hào):FPGA研究院,微信公眾號(hào):FPGA研究院】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

淺析Altera公司Stratix V FPGA芯片

FPGA/CPLD同步設(shè)計(jì)若干問(wèn)題淺析

微波暗室的主要用途

各波段無(wú)線電波的主要用途

GPS的主要用途有哪些?

液晶拼接屏主要用途有哪些

寬帶固定衰減器的主要用途和指標(biāo)

液晶拼接屏主要用途有哪些

施密特觸發(fā)器的主要用途有哪些

Jtti:Windows服務(wù)器在企業(yè)環(huán)境中的主要用途和應(yīng)用場(chǎng)景是什么?

頂堅(jiān)單北斗井下防爆手機(jī)的重要用途

淺析FPGA的重要用途

淺析FPGA的重要用途

評(píng)論