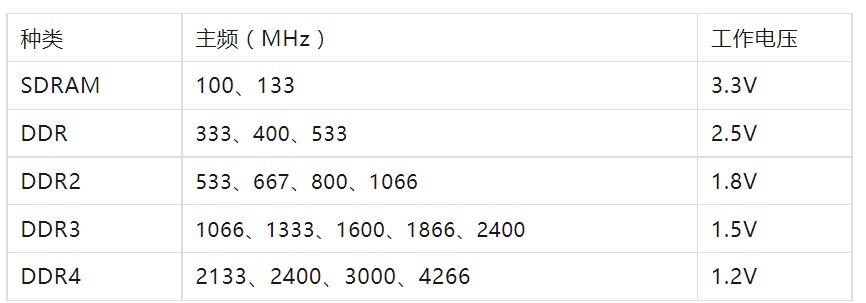

SDRAM是做嵌入式系統(tǒng)中,常用是的緩存數(shù)據(jù)的器件。基本概念如下(注意區(qū)分幾個主要常見存儲器之間的差異):

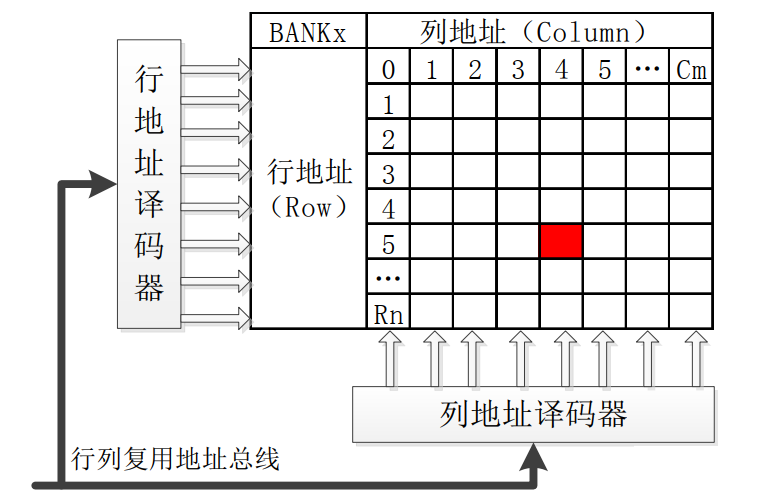

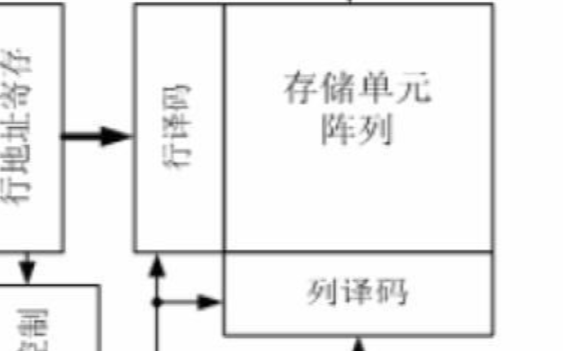

SDRAM(Synchronous Dynamic Random Access Memory),同步動態(tài)隨機(jī)存儲器。同步是指 Memory工作需要同步時鐘,內(nèi)部的命令的發(fā)送與數(shù)據(jù)的傳輸都以它為基準(zhǔn);動態(tài)是指存儲陣列需要不斷的刷新來保證存儲的數(shù)據(jù)不丟失,因?yàn)镾DRAM中存儲數(shù)據(jù)是通過電容來工作的,大家知道電容在自然放置狀態(tài)是會有放電的,如果電放完了,也就意味著SDRAM中的數(shù)據(jù)丟失了,所以SDRAM需要在電容的電量放完之前進(jìn)行刷新;隨機(jī)是指數(shù)據(jù)不是線性依次存儲,而是自由指定地址進(jìn)行數(shù)據(jù)的讀寫。

1. 注意事項(xiàng)

以下是我在學(xué)習(xí)過程中總結(jié)的一些容易理解錯誤的細(xì)節(jié),如果對其中有些概念不太明確,建議先學(xué)習(xí)基本概念。

1.1 突發(fā)長度(Burst Length)

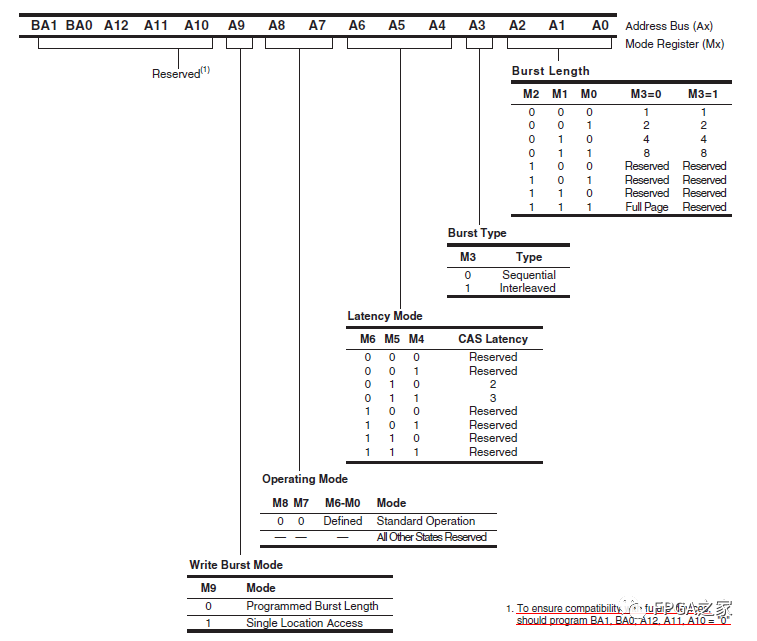

突發(fā)傳輸是指:在行地址指定后,只要指定起始列地址與突發(fā)長度,內(nèi)存就會依次地自動對后面相應(yīng)數(shù)量的存儲單元進(jìn)行讀/寫操作而不再需要控制器連續(xù)地提供列地址。

對SDRAM器件的讀和寫是面向突發(fā)的,而突發(fā)長度(BL)則是可編程的。

突發(fā)長度決定了給定讀寫命令可以訪問的最大的列位置的個數(shù)。

不管是順序(Sequential)還是交叉(Interleaved)突發(fā)類型,其突發(fā)長度均可為1,2,4,8或連續(xù)。對于順序突發(fā)類型,還適用于連續(xù)的頁面突發(fā)。

連續(xù)頁面突發(fā)與BURST TERMINATE命令一起使用以產(chǎn)生任意突發(fā)長度。

保留狀態(tài)不應(yīng)使用,因?yàn)檫@會導(dǎo)致未知操作或與未來的版本不匹配。

當(dāng)讀或?qū)懨钐峤粫r,一個等于突發(fā)長度的列的塊被有效選擇。所有對該突發(fā)的訪問發(fā)生在本塊之內(nèi),意味著當(dāng)遇到邊界時,突發(fā)會在該塊之內(nèi)循環(huán)(wraps within the block)。當(dāng)BL=2時,該塊唯一地被A[8:1]所選擇,當(dāng)BL=4時,A[8:2],BL=8時,A[8:3]。其余的地址位被用于選擇塊內(nèi)的起始地址。

1.2 自動刷新AS(Auto Refresh)和自刷新SR(Self Refresh)

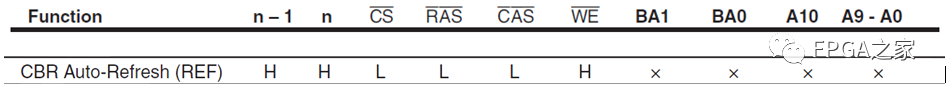

刷新操作分為兩種:自動刷新(Auto Refresh,簡稱AR)與自刷新(Self Refresh,簡稱SR)。不論是何種刷新方式,都不需要外部提供行地址信息,因?yàn)檫@是一個內(nèi)部的自動操作。

對于AR, SDRAM內(nèi)部有一個行地址生成器(也稱刷新計(jì)數(shù)器)用來自動的依次生成行地址。由于刷新是針對一行中的所有存儲體進(jìn)行,所以無需列尋址,或者說CAS在RAS之前有效。所以,AR又稱CBR(CAS Before RAS,列提前于行定位)式刷新。由于刷新涉及到所有L-Bank,因此在刷新過程中,所有L-Bank都停止工作,而每次刷新所占用的時間為9個時鐘周期(PC133標(biāo)準(zhǔn)),之后就可進(jìn)入正常的工作狀態(tài),也就是說在這9 個時鐘期間內(nèi),所有工作指令只能等待而無法執(zhí)行。64ms之后則再次對同一行進(jìn)行刷新,如此周而復(fù)始進(jìn)行循環(huán)刷新。顯然,刷新操作肯定會對SDRAM的性能造成影響,但這是沒辦法的事情,也是DRAM相對于SRAM(靜態(tài)內(nèi)存,無需刷新仍能保留數(shù)據(jù))取得成本優(yōu)勢的同時所付出的代價(jià)。

SR則主要用于休眠模式低功耗狀態(tài)下的數(shù)據(jù)保存,這方面最著名的應(yīng)用就是STR(Suspend to RAM,休眠掛起于內(nèi)存)。在發(fā)出AR命令時,將CKE置于無效狀態(tài),就進(jìn)入了SR模式,此時不再依靠系統(tǒng)時鐘工作,而是根據(jù)內(nèi)部的時鐘進(jìn)行刷新操作。在SR期間除了CKE之外的所有外部信號都是無效的(無需外部提供刷新指令),只有重新使CKE有效才能退出自刷新模式并進(jìn)入正常操作狀態(tài)。

2. 操作說明

我們以SDRAM芯片IS42S16320D為例,盡可能詳細(xì)的說明一下對其實(shí)現(xiàn)操作的方法。相關(guān)的Verilog代碼在后面給出。

2.1 時序

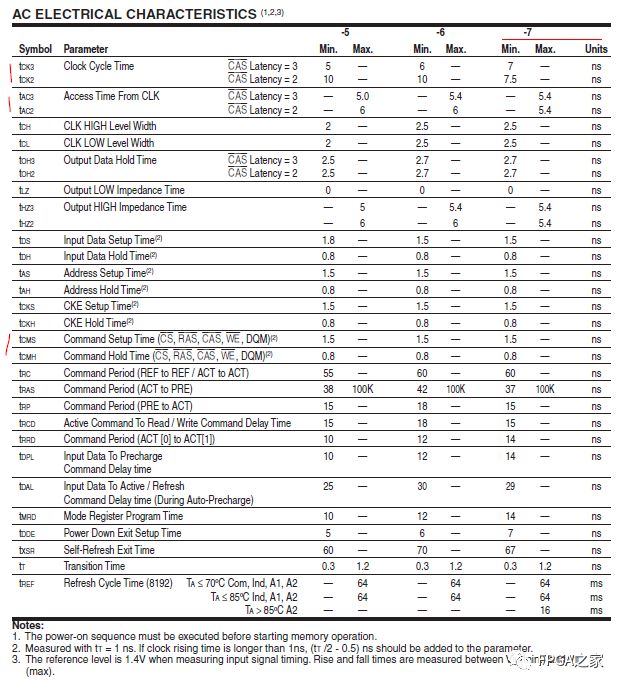

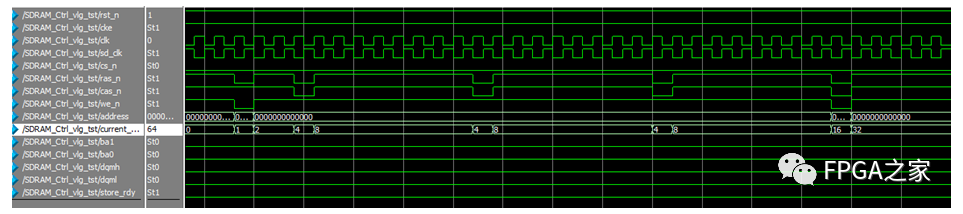

時序圖如下圖所示,在操作過程中,每個命令的執(zhí)行或者數(shù)據(jù)的讀寫,都要滿足相應(yīng)的時序要求,一定要仔細(xì)。

為滿足命令鎖存所需的建立時間tCMS和保持時間tCMH,需要對SD_clk采用與clk反向或者分頻機(jī)制。

系統(tǒng)時鐘clk為100MHz

2.2 刷新時間

SDRAM內(nèi)部電容保存數(shù)據(jù)的最長時間是64ms,而我們一個BANK有8K行,64ms/8k~=7.8us,也就是說為了保證SDRAM內(nèi)部的數(shù)據(jù)不被丟失,兩次刷新之間的最大時間間隔為7.8us,所以為了能讓SDRAM有更多的時間進(jìn)行讀或者寫,并且留夠余量,我們就設(shè)定SDRAM刷新的周期為7.7us。

從時序上看,在讀寫過程中如果需要刷新,則先進(jìn)入PRECHARGE然后進(jìn)入IDLE,再進(jìn)行刷新。

因此我們要保證的是 刷新時間+需要等待的時間<=7.8us.

如果是讀,則需要等待的時鐘周期為 激活時間(tRCD)+ CAS Latency (tCL)+ 讀一頁的時間 +預(yù)充電的時間(tRP)

如果是寫,則需要等待的時鐘周期為 激活時間(tRCD)+ 寫一頁的時間 + 預(yù)充電的時間(tRP)

在實(shí)現(xiàn)上,可以采用定時和手動控制刷新兩種方式結(jié)合。7.7us的定時計(jì)數(shù)器不斷地進(jìn)行,如果沒計(jì)時到7.7us,有收到刷新請求信號,那么開始刷新,并且計(jì)數(shù)器重新計(jì)數(shù)。這樣就可以實(shí)現(xiàn),每讀/寫一次(讀寫完整時間應(yīng)該滿足上述要求),手動刷新。如果長期等待,則靠計(jì)數(shù)器定時刷新。

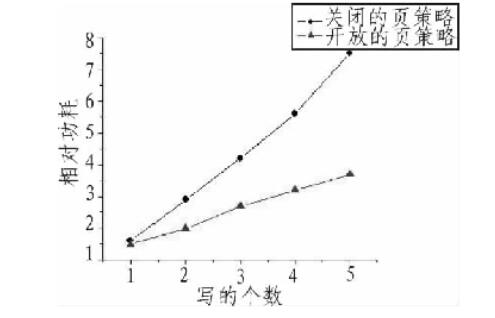

2.3 頁操作(full page)

一般而言,要實(shí)現(xiàn)快速大數(shù)據(jù)的讀寫,可以采用頁操作,即突發(fā)長度設(shè)計(jì)為full page。

SDRAM在頁操作模式下必須使用突發(fā)停止命令停止其操作。這回要發(fā)揮頁模式的靈活性和高效性,那么就要做成一個由外部輸入數(shù)據(jù)控制其一次性操作的字節(jié)數(shù),也就是說,外部在讀寫數(shù)據(jù)前事先控制一個寄存器,往寄存器寫入需要操作的字節(jié)數(shù),而進(jìn)入讀寫操作后,SDRAM控制器根據(jù)外部給出的字節(jié)數(shù)在適當(dāng)?shù)臅r候發(fā)出突發(fā)停止命令,這樣做到了SDRAM的讀寫操作的字節(jié)可以在1-256范圍內(nèi)靈活調(diào)整,增強(qiáng)了通用性。

2.4 狀態(tài)機(jī)

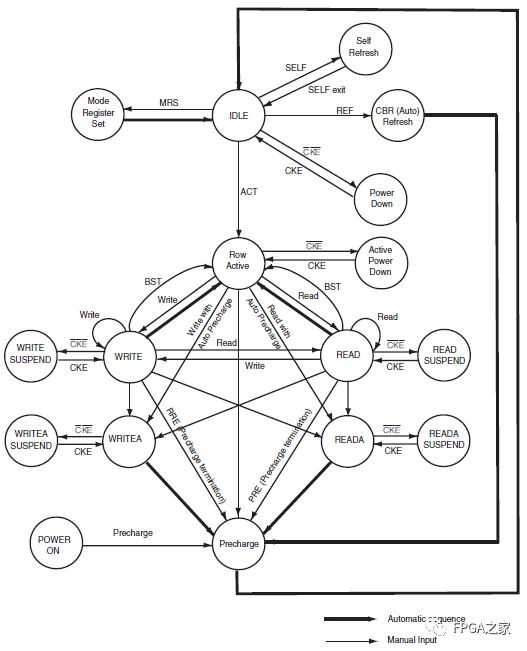

IS42S16320D手冊里面給出的狀態(tài)圖,仔細(xì)理解每個狀態(tài)的流程及跳變條件。

3. 詳細(xì)操作

IS42S16320D的操作主要包括上電初始化、空閑、讀、寫、刷新等狀態(tài)。

3.1 初始化

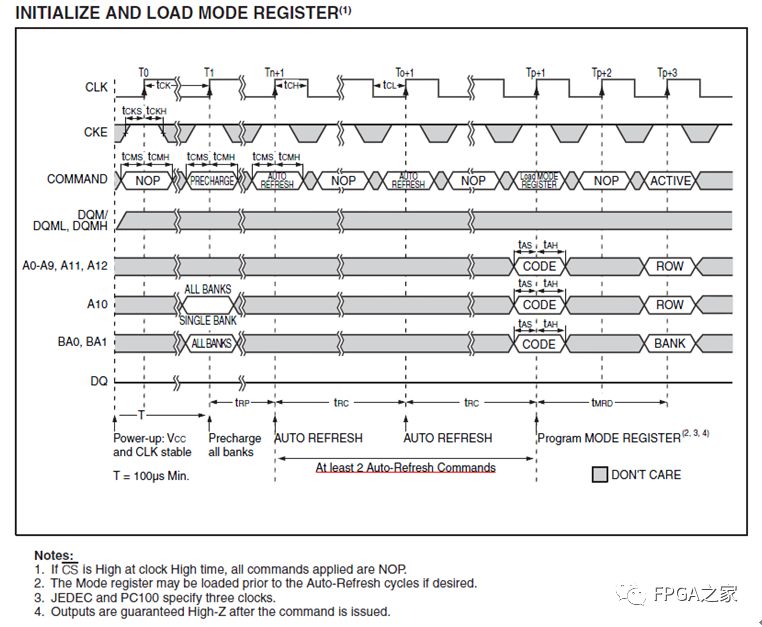

芯片在上電之后有一些固定的操作,手冊里面已經(jīng)明確的說明,如下圖。

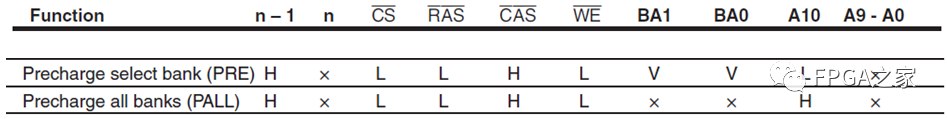

主要包括以下幾個步驟的操作,圖表里面代表操作引腳的狀態(tài)。

上電延遲

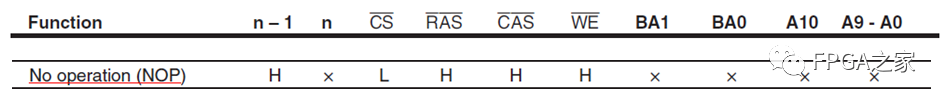

上電后,芯片有個100us的延遲(其他RAM一說200us),期間命令指令設(shè)置為NOP或者COMMAND INHIBIT。CKE的狀態(tài)呢(不管還是一直為高),貌似一直為高才行,因?yàn)槊钜蕾囉赾lk的上升沿,而要使clk有效,必須置高CKE?

預(yù)充電

電延遲以后,對所有bank進(jìn)行預(yù)充電。Bank關(guān)閉現(xiàn)有工作行,準(zhǔn)備打開新行的操作就是預(yù)充電(Precharge)。

自動刷新

充電完成后,間隔tRP Command Period (PRE to ACT) 最小15ns,進(jìn)行第一次自動刷新,再過tRC Command Period (REF to REF / ACT to ACT) 最小60ns,進(jìn)行第二次自動刷新。

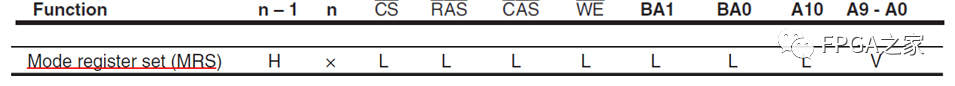

模式寄存器配置

第二次自動刷新后,間隔tRC(60ns)再進(jìn)行模式寄存器設(shè)置。注意,具體的模式依賴于A9-A0管腳的高低電平。具體參加下圖。

初始化完成

模式寄存器設(shè)置完成后,間隔tMRD Mode Register Program Time 14ns后,就可以給ACTIVE命令,即使行地址處于工作狀態(tài)。

如下圖所示,為功能仿真完成上電初始化過程。

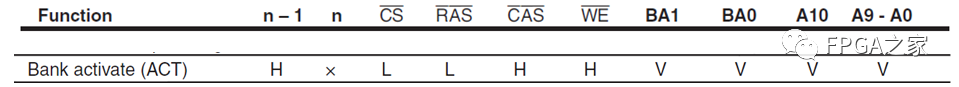

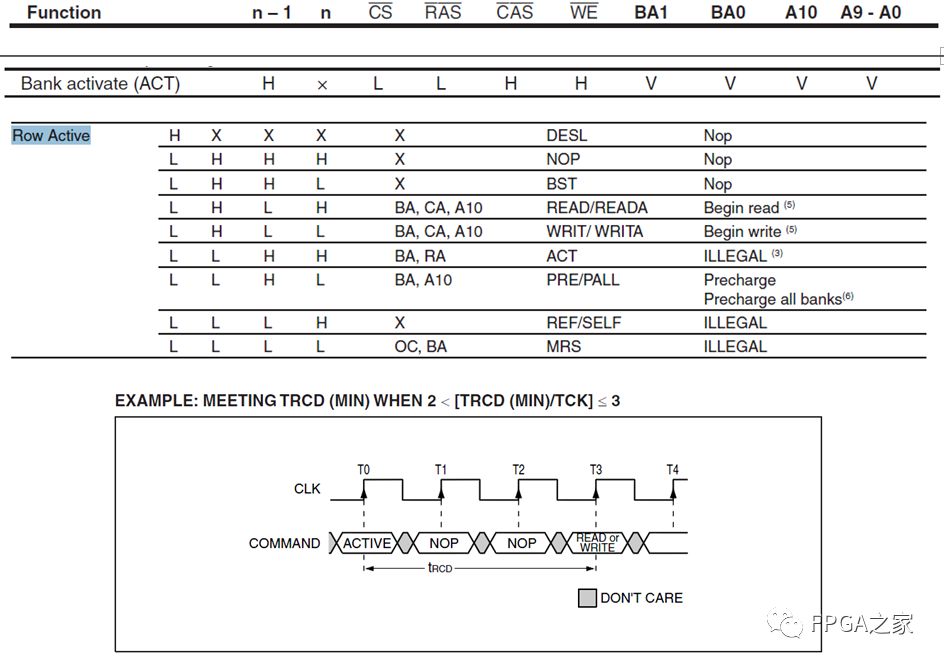

3.2 行激活

IDLE狀態(tài)進(jìn)入讀寫前,一定要行激活ROW ACTIVE。行激活命令完成之后,需要經(jīng)過tRCD Active Command To Read / Write Command Delay Time 15 ns才能進(jìn)行讀或?qū)憽M籦ank,不同row,激活需要間隔至少6個周期;不同bank,不同row,激活需要間隔至少2個周期,可以提高速度。

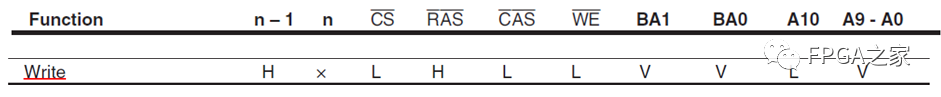

3.3 寫數(shù)據(jù)

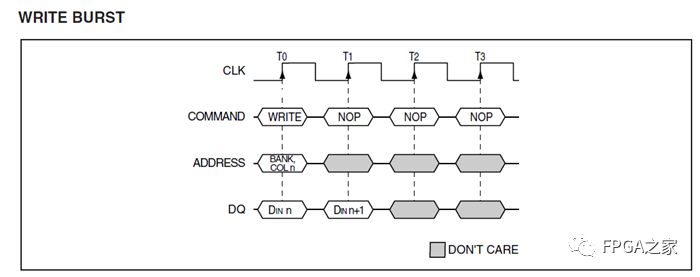

寫入的第一個數(shù)據(jù)與WRITE命令對齊,寫完burs length的長度之后,輸入自動變?yōu)楦咦瑁辉俳邮諗?shù)據(jù)。如果全頁寫入的話,如果不給burst terminate,會從頭開始覆蓋著寫入。

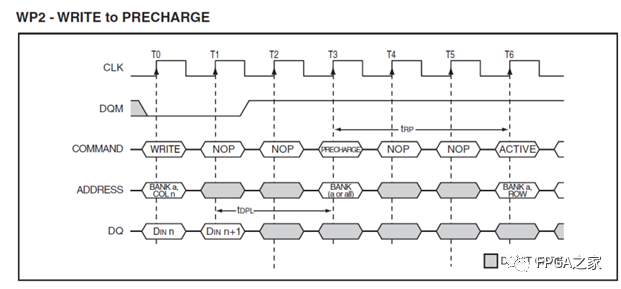

如果采用全頁寫入的方式,當(dāng)需要PRECHARGE的時候,需要預(yù)留tDPL的時間(14 ns,與最后一個數(shù)據(jù)的上升沿對齊),寫入過程即被中斷,然后在第一定時間(tRP)之后開始刷新。一般來說,write被中斷時,可以拉高DQM以阻斷數(shù)據(jù)的輸入。采用PRECHARGE中斷寫操作的缺點(diǎn)是需要考慮合適的時間點(diǎn)去配置cmd和address。優(yōu)點(diǎn)是它可以任何時候去中斷寫操作,不論是固定長度的寫操作還是全頁寫操作。

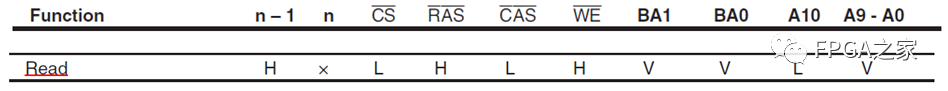

注意:在讀或?qū)懙拿钪校珹10控制是否自動預(yù)充電。

3.4 讀數(shù)據(jù)

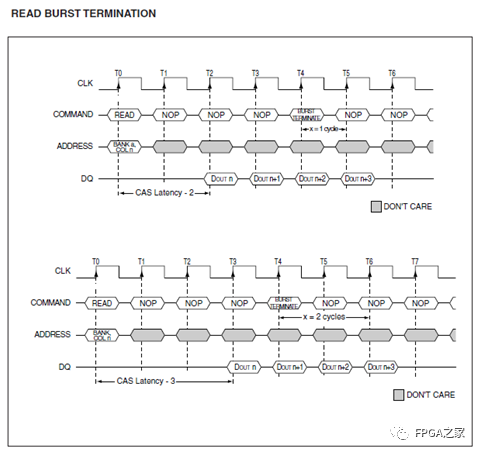

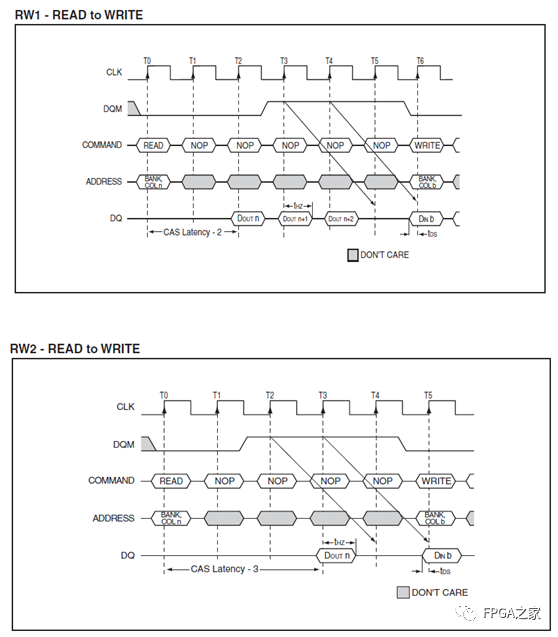

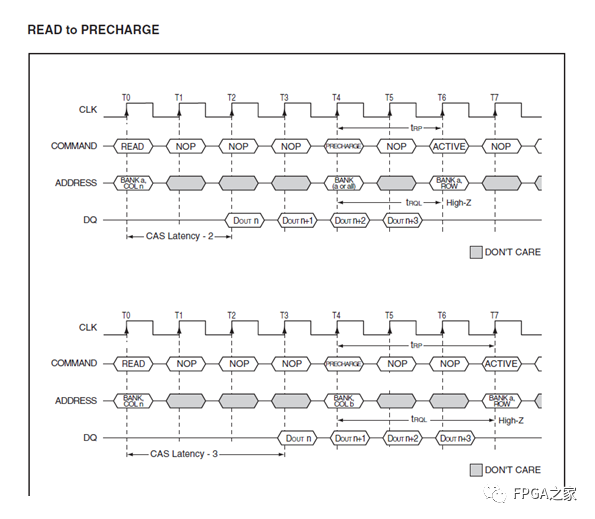

在連續(xù)讀的時候,如果新的命令加入(寫、讀、預(yù)充電),發(fā)出時刻x必須滿足最后一個期望讀出的數(shù)據(jù)到來前的CAS Latency-1個周期。

在讀轉(zhuǎn)寫的過程中,寫命令發(fā)出時刻應(yīng)在最后一個讀出數(shù)據(jù)所在時刻。但是,在實(shí)際系統(tǒng)中,為了避免I/O切換輸入輸出狀態(tài)時,出現(xiàn)沖突,所以寫指令會延后一個周期。In a given system design, there may be a possibility that the device driving the input data will go Low-Z before the SDRAM DQs go High-Z. In this case, at least a single-cycle delay should occur between the last read data and the WRITE command.

控制DMQ來避免I/O沖突,在WRITE命令來之前三個周期就要把DMQ拉高。注意DMQ并不會直接抑制輸出,只是抑制內(nèi)部的buffer,所以當(dāng)DMQ拉高時,實(shí)際上抑制之前buffer的數(shù)據(jù)還是照樣輸出。在WRITE命令來之前,必須把DMQ再拉低,否則輸入無效。(For example, if DQM was LOW during T4 in Figure RW2, then the WRITEs at T5 and T7 would be valid, while the WRITE at T6 would be invalid.???)

4. 疑問

周期性刷新的執(zhí)行過程采用的是:每次在同一bank和同一row中讀寫完成后先預(yù)充電,再刷新2次。可不可以只刷新,而不用預(yù)充電???

狀態(tài)機(jī)上,CBR明明自動進(jìn)入PRECHARGE,這怎么解釋。

-

FPGA

+關(guān)注

關(guān)注

1646文章

22089瀏覽量

620313 -

SDRAM

+關(guān)注

關(guān)注

7文章

443瀏覽量

56472 -

存儲器

+關(guān)注

關(guān)注

39文章

7662瀏覽量

168259 -

嵌入式系統(tǒng)

+關(guān)注

關(guān)注

41文章

3687瀏覽量

131697

原文標(biāo)題:FPGA實(shí)戰(zhàn)操作(1) -- SDRAM(操作說明)

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

SDRAM芯片引腳說明和存儲單元

簡單認(rèn)識雙倍速率同步動態(tài)隨機(jī)存取存儲器

FLASH存儲器與SRAM最主要的區(qū)別是什么

基于DSP的VXI總線動態(tài)存儲器設(shè)計(jì)

什么是SDRAM內(nèi)存

STM32同步動態(tài)隨機(jī)存取存儲器(SDRAM)的源代碼程序資料免費(fèi)下載

SRAM隨機(jī)存儲器的特點(diǎn)及結(jié)構(gòu)

各種隨機(jī)存儲器件之中,SDRAM脫穎而出的優(yōu)勢是什么

如何辨別SRAM是否屬于動態(tài)隨機(jī)存儲器

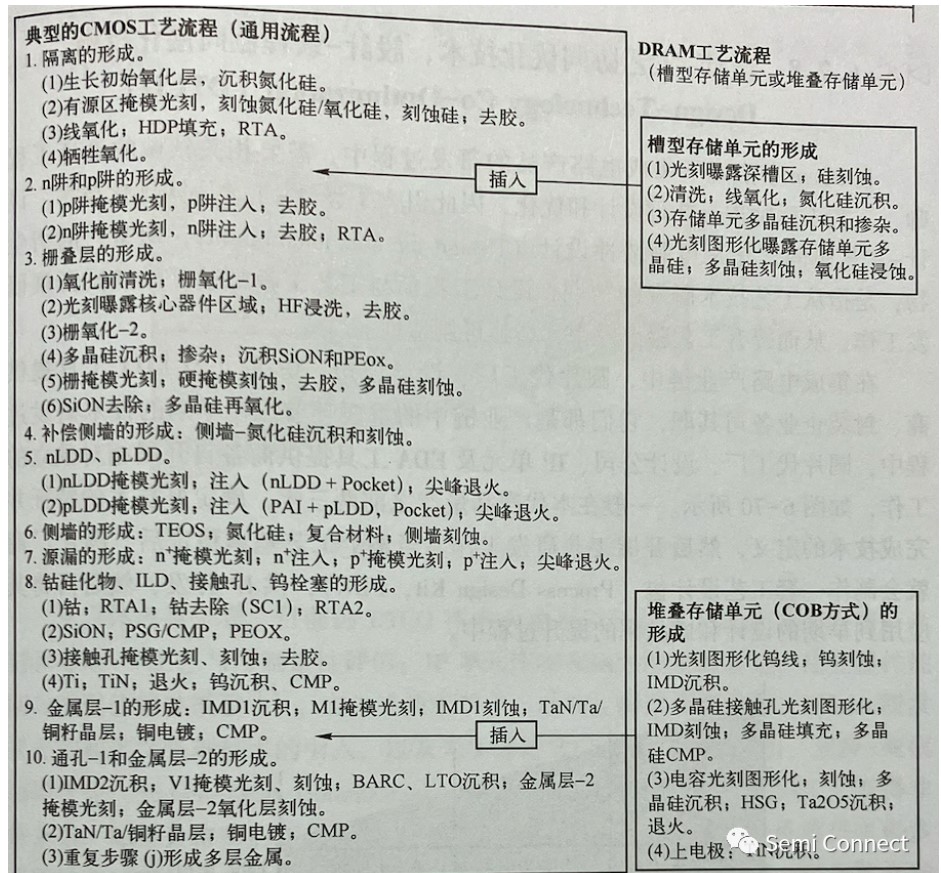

動態(tài)隨機(jī)存儲器集成工藝(DRAM)詳解

淺析動態(tài)隨機(jī)存儲器DRAM集成工藝

SDRAM工作原理 SDRAM布局布線說明

低功耗雙倍速率同步動態(tài)隨機(jī)存取存儲器介紹

評論