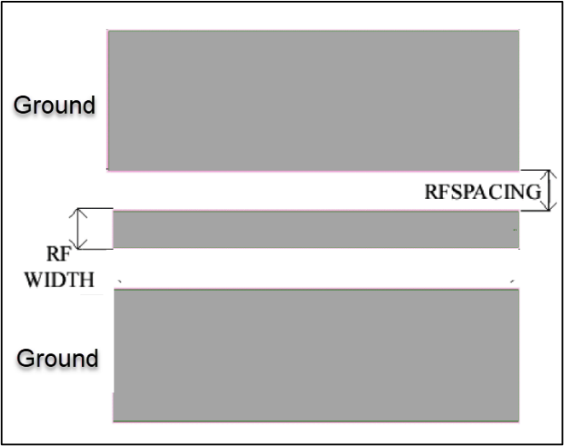

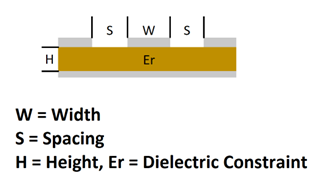

在射頻印刷電路板(RF PCBs)中實現最佳功率傳輸,關鍵在于精心布線以滿足特定阻抗要求的走線。阻抗匹配至關重要,它確保走線具有相同的阻抗,以防止信號反射和功率傳輸效率低下。控制阻抗的關鍵在于微調走線寬度、走線厚度以及在z軸上將走線與參考平面分隔開的介質高度。信號層下方的連續參考平面對于保持最佳阻抗也至關重要。在同一層上保持適當的走線到地間隙(對于共面波導)對于一致的阻抗控制同樣重要。

共面波導(俯視圖)

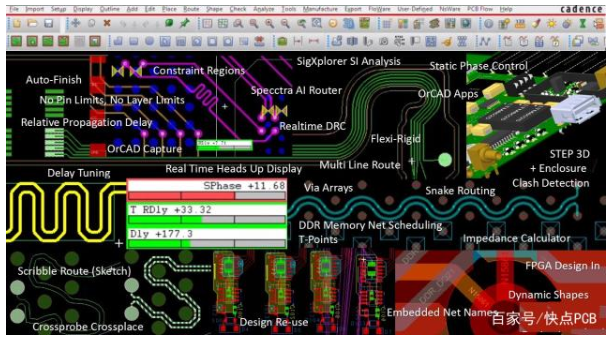

共面波導(橫截面圖)本文提供了實現最佳射頻(RF)布線和阻抗的解決方案。向大家介紹如何保護射頻電路免受同一印刷電路板(PCB)的其他部分或相鄰 PCB 產生的電磁干擾(EMI)。還解釋了如何在信號彎曲的地方將射頻走線轉換為鋪銅,以便更順暢地進行編輯。這些解決方案將在使用 Allegro X PCB Editor進行射頻 PCB 布局布線時為您提供幫助。

1

使用Via Arrays保護射頻電路以防止

電磁干擾

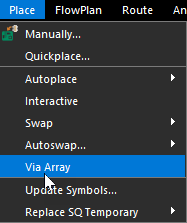

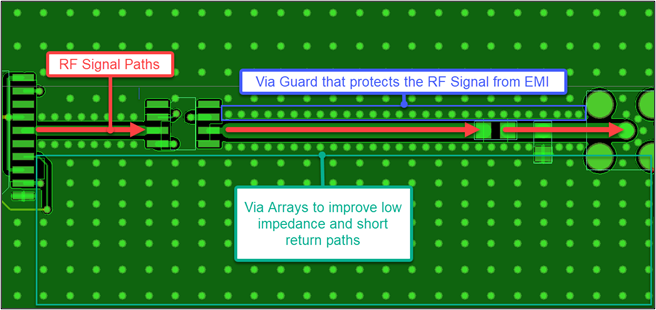

在射頻走線的兩側添加屏蔽可以保護電路免受電磁干擾。Via Arrays可以充當屏蔽,保護射頻信號免受相鄰電路產生的電磁干擾。Via Arrays是一系列以特定模式圍繞射頻信號放置的過孔,形成一個屏障并防止電磁干擾。要在 Allegro X PCB Editor中將Via Arrays添加到設計中,可執行以下操作:1、選擇Place–Via Array.

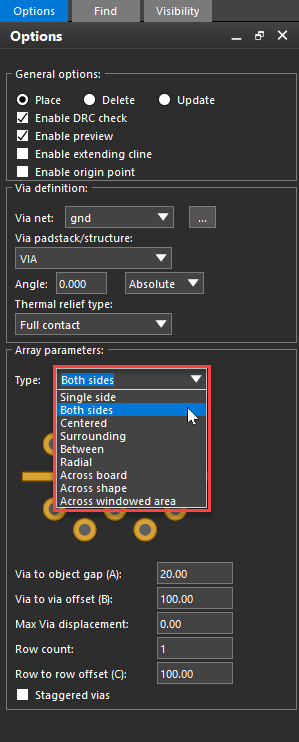

2、 點擊theOptions面板.3、按下圖所示,在Options面板的Array Parameters Type列表中選中Both sides:

4、在設計面板中選擇RF走線,一個Via Arrays沿著RF走線的兩側顯示出來。5、在Array Parameter中調整過孔間距設置,可以在走線周圍獲得最佳的Via Arrays。6、在設計面板中的任意位置點擊,即將Via Arrays放置在走線的兩側。

2

向射頻平面添加接地過孔

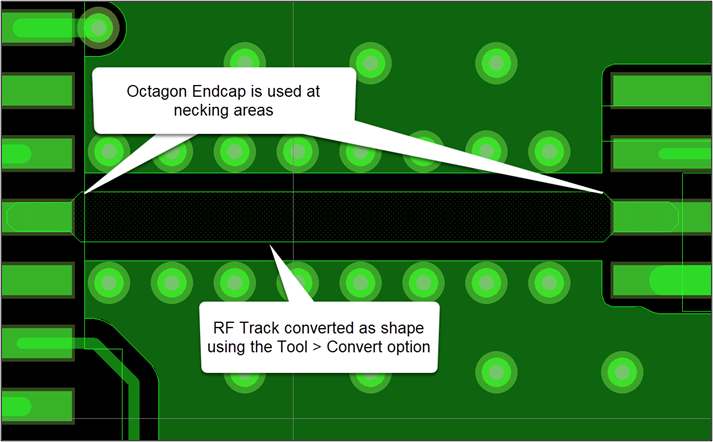

在為所有射頻信號添加過孔陣列后,在PCB的射頻電路部分附近,使用接地過孔接地的大的鋪銅填充,可保持 PCB 的較低阻抗并改善對地參考。可以使用via array命令來添加接地過孔。以下圖像展示了 PCB 布局的射頻部分,射頻信號兩側由過孔保護,接地平面用接地過孔縫合。這個可視化圖像可以幫助大家理解過孔應如何放置,以便它們在射頻信號周圍創建一個屏障。

3

將射頻走線轉換為鋪銅

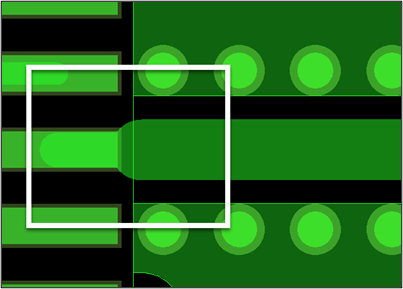

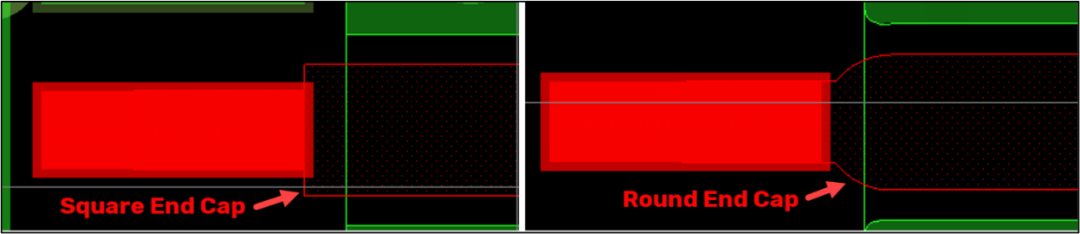

通常,射頻走線在縮頸點需要逐漸變細,避免其寬度的突然變化,以確保射頻信號的平滑過渡。然而,當設計師將射頻信號布線為弧形走線時,在走線進出元件時需要減小走線寬度的地方,無法進行逐漸變細操作。以下圖像顯示了一條在頸部區域出現阻抗變化的走線:

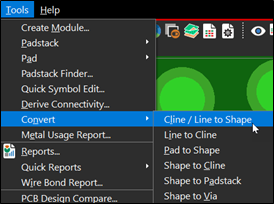

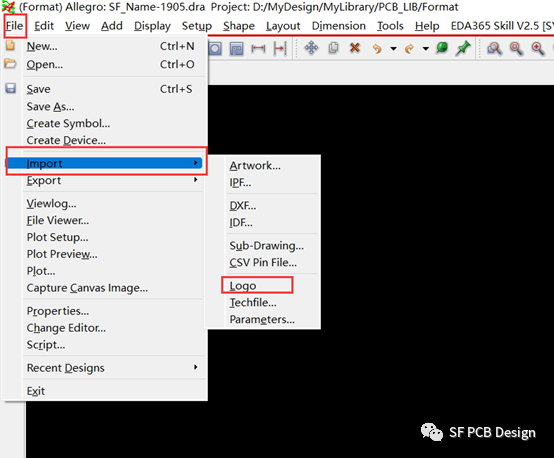

Shape為編輯提供了極大的靈活性。在布線的最后階段將射頻信號走線轉換為Shape可改善阻抗控制。在 Allegro X PCB Editor中將射頻走線轉換為Shape以增強設計靈活性,可執行以下操作:1、選擇Tools–Convert–Cline/Line to Shape

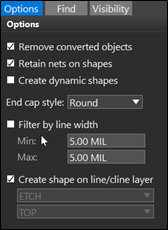

2、修改Options面板中設置。可以保留現有走線、保留網絡,或將shape更改為動態。3、要確定應轉換為shape的走線,請指定包含它們的區域或根據寬度應用過濾器。

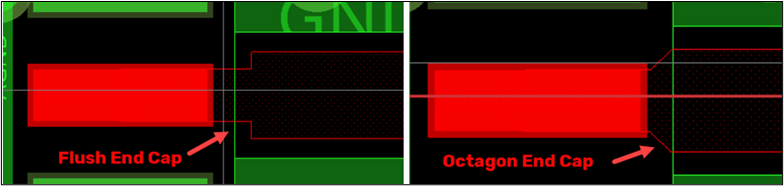

4、選擇“End cap style”選項,為走線的起始和結束邊緣選擇一個形狀(正方形、圓形、八邊形或齊平),如下圖所示:

轉換為Shape后的射頻信號如下圖所示:

4

對射頻信號應用Mask Shapes:

在確定射頻形狀后,下一步是對射頻信號應用Mask Shapes 。這涉及將射頻形狀從信號層復制到Mask層。可以這樣做,在射頻信號層上方創建一個開放的掩模。這一步至關重要,因為它有助于維持射頻電路的特性阻抗。忽略這一步可能會改變射頻電路的特性阻抗,影響電路的性能。對射頻信號應用Mask Shapes 以滿足微帶線或共面波導的要求是很重要的。

5

結論

本文為大家提供了應對射頻 PCB 設計復雜性的知識和技術。通過學習所提供的解決方案,可以確保您的射頻 PCB 設計實現最佳的功率傳輸,并為 PCB 的整體可靠性和效率做出貢獻。實現過孔陣列并將射頻走線轉換為shape可增強信號完整性并保護射頻電路免受電磁干擾。

文章來源:Cadence

-

pcb

+關注

關注

4319文章

23080瀏覽量

397494 -

電路板

+關注

關注

140文章

4951瀏覽量

97689 -

阻抗

+關注

關注

17文章

957瀏覽量

45912 -

布線

+關注

關注

9文章

771瀏覽量

84322 -

allegro

+關注

關注

42文章

655瀏覽量

145130

發布評論請先 登錄

相關推薦

Allegro PCB Editor Win8.1 64位失去響應問題

Cadence Allegro與OrCAD PCB軟件全新功能與特性

Allegro技術如何助力EDA360目標的實現

allegro pcb editor規則設置類別優先順序

3D打印PCB如何幫助阻抗控制的布線

使用Allegro PCB Editor制作Logo封裝

Allegro X 23.11 版本更新 I PCB 設計:DFA_BOUND 用于 DFA 規則設定

技術資訊 I 如何使用 Allegro X PCB Editor 優化RF布線和阻抗

技術資訊 I 如何使用 Allegro X PCB Editor 優化RF布線和阻抗

評論