隨著半導體行業的快速發展,先進封裝技術成為了提升芯片性能和功能密度的關鍵。近年來,作為2.5D和3D封裝技術之間的一種結合方案,3.5D封裝技術逐漸走向前臺。

什么是3.5D封裝技術

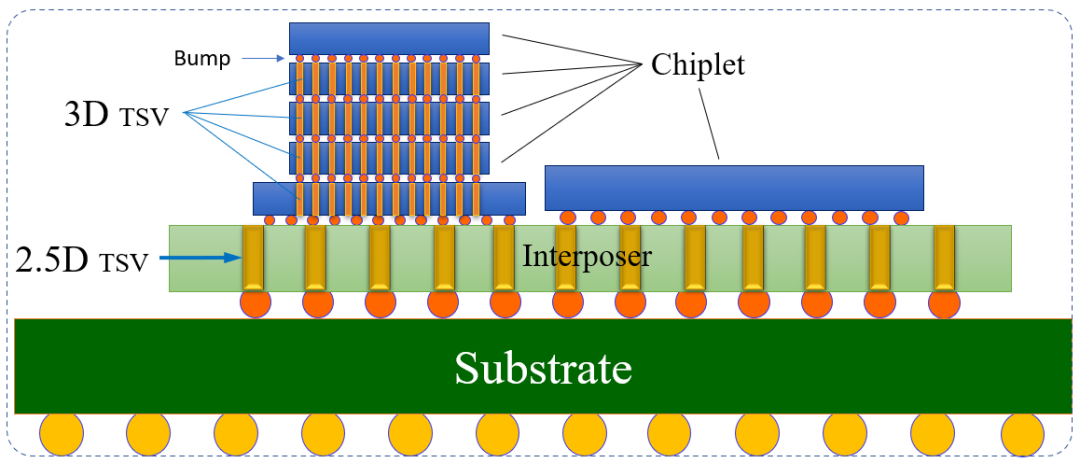

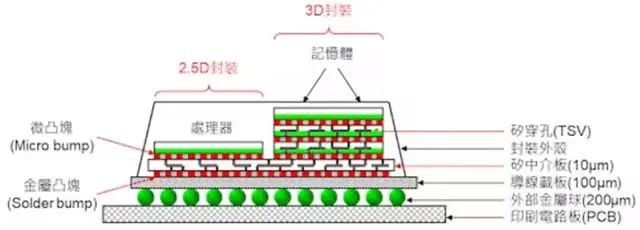

3.5D封裝技術最簡單的理解就是3D+2.5D,通過將邏輯芯片堆疊并將它們分別粘合到其他組件共享的基板上,創造了一種新的架構。能夠縮短信號傳輸的距離,大幅提升處理速度,這對于人工智能和大數據應用尤為重要。

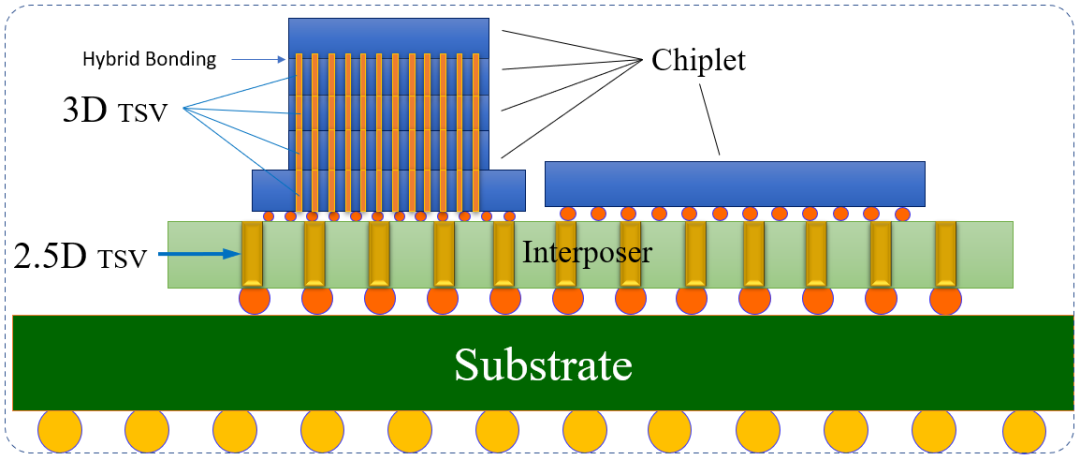

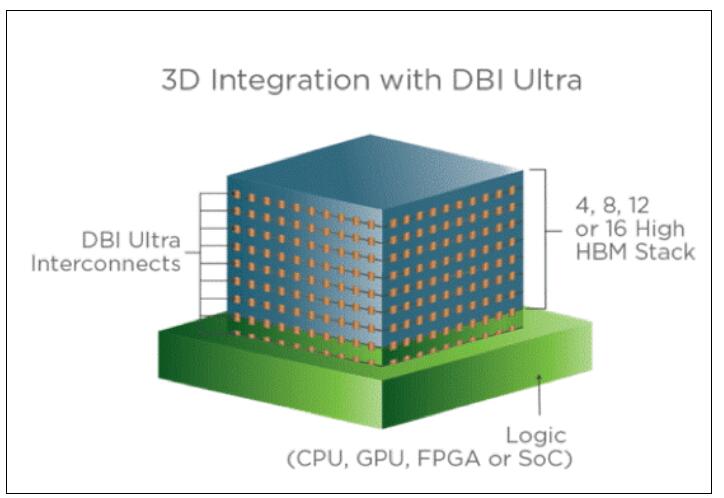

不過,既然有了全新的名稱,必然要帶有新的技術加持 —— 混合鍵和技術(Hybrid Bonding)。混合鍵合技術的應用為3.5D封裝帶來了新的可能性,是一種在相互堆疊的芯片之間獲得更密集互連的方法。

混合鍵合技術加持的3DTSV的直接互連

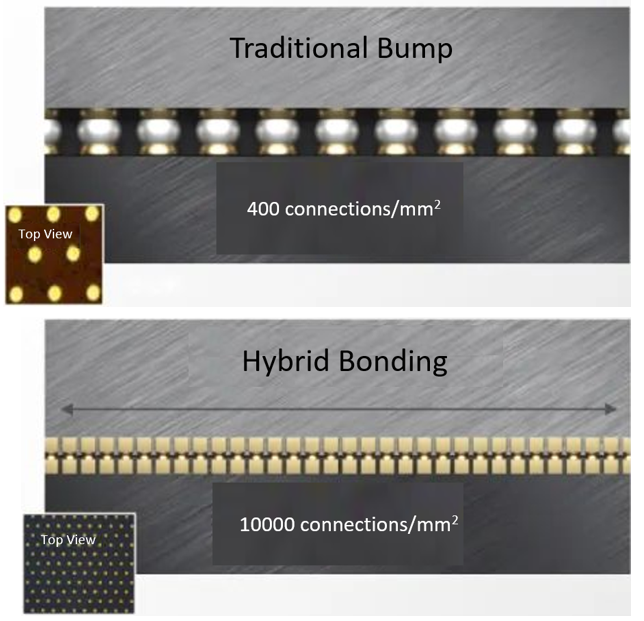

通過混合鍵合,可以在更小的空間內實現更多的連接,從而提高封裝的密度和性能。下圖是傳統凸點和混合鍵合技術的結構比較:傳統凸點間距是50微米,每平方毫米有大約400個連接;混合鍵和大約10微米的間距,可達到每平方毫米10000個連接。

傳統凸點和混合鍵合技術的結構比較

混合鍵合解決了另一個棘手的問題,即數千個微凸塊之間的共面性,而制造傳統鍵合產品很難以合理的產量滿足這一要求。混合鍵合技術應用于3DTSV的直接互連,省卻了凸點,其界面互連間距可小于10um甚至1um,其互連密度則可達到每平方毫米10000~1000000個點。這是傳統的凸點互連遠遠無法達到的,因此,在高密度的3D互連中,凸點最終會消失。

另外,SRAM作為處理器緩存的首選,通過3.5D封裝技術可以在不增加物理面積的情況下實現更多內存的集成。SRAM不一定必須與處理器的先進節點處于同一節點,這也有助于提高產量和可靠性。

在最近的三星代工活動中,該公司代工業務開發副總裁Taejoong Song展示了3.5D配置的路線圖,將使用2nm芯片堆疊在4nm芯片上,2027年將使用1.4nm芯片堆疊在2nm芯片上。

英特爾代工廠的方法在很多方面都很相似。英特爾高級副總裁兼代工服務總經理Kevin O'Buckley表示:“我們的3.5D技術是在帶有硅橋的基板上實現的。這不是成本極高、產量低、多掩模版形狀的硅,甚至不是RDL。我們以更具成本效益的方式使用薄硅片,通過硅橋實現芯片到芯片的連接,甚至是堆疊芯片到芯片的連接。因此,您可以獲得相同的硅密度優勢,以及該硅橋的相同SI(信號完整性)性能,而無需在整個硅橋下方放置巨大的單片中介層,這既成本高昂又限制了容量。它正在發揮作用。它正在實驗室中運行。”

3.5D封裝技術的挑戰

雖然當前的技術已經能夠實現較為穩定的3.5D封裝,但在大規模生產和應用中,仍需要進一步降低成本和提高良率,工藝的復雜性和制造成本是制約其大規模應用的主要因素。其次,3.5D封裝的可靠性和長期穩定性也需要進一步驗證,特別是在高溫和高壓環境下的應用場景中。

除此之外,散熱可能是最難解決的問題:工作負載可能會有很大差異,從而產生動態熱梯度并將熱量困在意想不到的地方,從而縮短芯片的使用壽命和可靠性。

理解2.5D和3D封裝技術

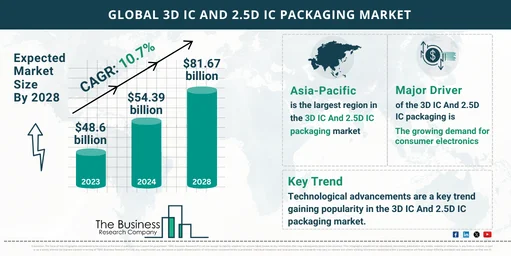

一直以來,提升芯片性能主要依靠先進制程的突破。但現在,人工智能對算力的需求,將芯片封裝技術的重要性提升至前所未有的高度。為了提升AI芯片的集成度和性能,高級封裝技術如2.5D/3D封裝和Chiplet等得到了廣泛應用。

根據研究機構的調研,到2028年,2.5D及3D封裝將成為僅次于晶圓級封裝的第二大先進封裝形式。這一技術不僅能夠提高芯片的性能和集成度,還能有效降低功耗,為AI和高性能計算等領域提供強有力的支持。

· 2.5D封裝技術

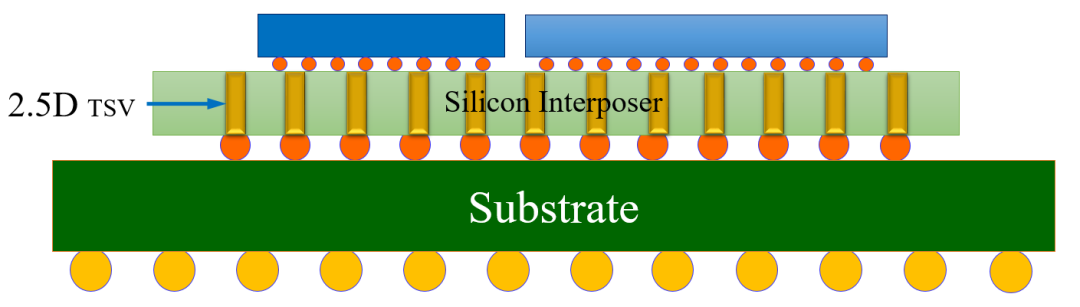

2008年,賽靈思將其大型FPGA劃分為四個良率更高的較小芯片,并將這些芯片連接到硅中介層,2.5D封裝由此誕生。2.5D封裝技術是一種介于傳統2D封裝和3D封裝之間的過渡技術,通過在硅中介層(Silicon Interposer)上集成多個裸芯片(Bare Die),實現了芯片之間的高速互連和短距離通信。硅中介層通常采用硅通孔(Through-Silicon Via,TSV)技術實現垂直互連,具有高密度、高性能的互連特性,可以大大提高系統的整體性能。

2.5D封裝的整體結構

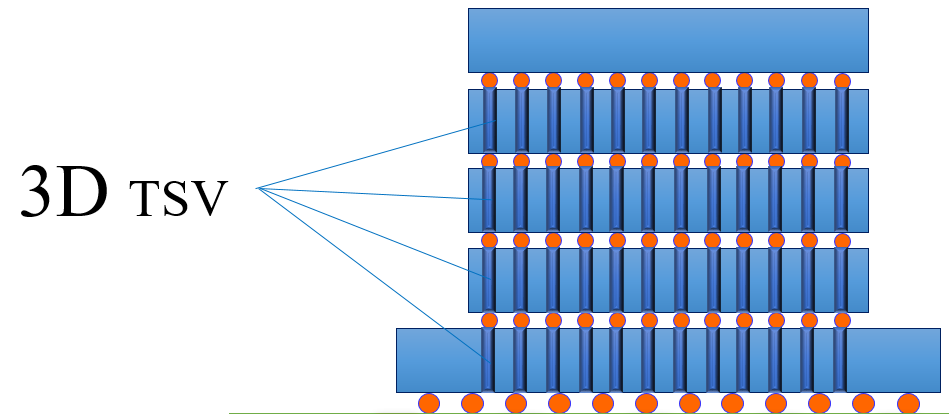

· 3D封裝技術

3D封裝是指在不改變封裝體尺寸的前提下,在同一個封裝體內于垂直方向疊放兩個以上芯片的封裝技術,它起源于快閃存儲器(NOR/NAND)及SDRAM的疊層封裝。但是要注意的是,3D封裝不一定要用到TSV技術,通過引線鍵合(Wire Bonding)的方式連接且在空間上進行芯片堆疊并封裝都能成為3D封裝。

3D封裝的整體結構

The Business Research Company近日發布了3D IC和2.5DIC封裝市場研究報告,預計未來幾年,3D IC和2.5D IC封裝市場規模將快速增長:將從2023年的486億美元增長到2024年的543.9億美元,復合年增長率(CAGR)為 11.9%,到2028年,市場規模將達到816.7億美元,CAGR為10.7%。預測期內的增長可歸因于可穿戴和便攜式設備的出現、能效需求的增長、高性能計算需求的上升、向片上系統設計的轉變、半導體器件復雜性的增加以及物聯網的普及。

另外,據市場分析機構Global Market Insights Inc.數據,2023年3D半導體封裝市場價值94億美元,預計2024年至2032年期間的CAGR將超過18%。

2.5D和3D封裝技術的區別

2.5D可以看兩塊積木在二維尺度是無法拼接在一起的,需要一個中介放在兩塊積木之下,且可以同時對兩塊積木進行連接;3D就直接積木與積木垂直(其實也不一定)的堆疊在一起,而積木就是一個個芯片。2.5D封裝是利用導電凸塊或TSV將組件堆棧在中介層上,3D IC封裝則將多層硅晶圓與采用TSV的組件連接在一起。

3D封裝中邏輯裸晶堆棧在一起或與儲存裸晶堆棧在一起,無需建構大型的系統單芯片。3D封裝技術在垂直方向上實現了更高的集成度,而2.5D封裝技術則通過硅中介層實現了水平方向上的高密度互連。

先進封裝中的關鍵技術

引線鍵合(Wire Bonding):采用直接穿過有源電路的多層互連結構,同時通過采用3D架構,可以將芯片折疊到它自己的上面,減小了互連線長度。這樣不僅會極大地提高電路性能,還會極大地降低電路的功耗。

硅通孔技術(Through Silicon Via,TSV):通過在硅片上打孔并填充導電材料實現了芯片之間的垂直電氣連接,可以完成連通上下層晶圓或芯片的功能,在更小的面積上大幅提升芯片性能并增加芯片功能。這種連接方式具有低電阻、低電容和低電感的特點,可以顯著提高信號傳輸的速度和穩定性。TSV用途大致分為三種:背面連接(應用于CIS等)、2.5D封裝(TSV在硅中介層)、3D封裝(TSV位于有源晶粒中,用于實現芯片堆疊)。

中介層(Interposers):中介層是封裝中多芯片裸晶或電路板傳遞電信號的管道,是插口或接頭之間的電接口,可以將信號傳播更遠,也可以連接到板子上的其他插口。中介層可以由硅和有機材料制成,充當多顆裸晶和電路板之間的橋梁。硅中介層是一種經過驗證的技術,具有較高的細間距I/O密度和TSV形成能力,在2.5D和3D IC芯片封裝中扮演著關鍵角色。

2D封裝加上Interposer后就變成了2.5D,那么3D封裝加上Interposer自然就變成了3.5D,既合情合理,又符合了通用的命名法則。

重分布層:重分布層包含銅連接線或走線,用于實現封裝各個部分之間的電氣連接。它是金屬或高分子介電材料層,裸晶可以堆棧在封裝中,從而縮小大芯片組的I/O間距。重分布層已成為2.5D和3D封裝解決方案中不可或缺的一部分,使其上的芯片可以利用中介層相互進行通訊。

高帶寬內存(High Bandwidth Memory,HBM):是一種用于3D堆疊同步動態隨機存取內存的高速計算機內存接口,最初由三星、AMD和SK Hynix開發,是將很多個DDR芯片堆疊在一起后和GPU封裝在一起,實現大容量。在堆疊內,芯片通過TSV和微凸塊垂直互連。

-

半導體

+關注

關注

334文章

27290瀏覽量

218081 -

封裝技術

+關注

關注

12文章

548瀏覽量

67981 -

3D封裝

+關注

關注

7文章

133瀏覽量

27118 -

先進封裝

+關注

關注

2文章

400瀏覽量

241

原文標題:2.5D和3D封裝技術還沒“打完架”,3.5D又來了?

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

研發的銅混合鍵合工藝正推動下一代2.5D和3D封裝技術

2.5D/3D芯片-封裝-系統協同仿真技術研究

分享一下小芯片集成的2.5D/3D IC封裝技術

3D封裝結構與2.5D封裝有何不同?3D IC封裝主流產品介紹

一文理解2.5D和3D封裝技術

一文理解2.5D和3D封裝技術

評論