量子計算機(jī)要充分發(fā)揮潛力,需要數(shù)百萬量子比特,而不是目前的數(shù)百量子比特。然而,通往量子計算機(jī)規(guī)模化的道路并不僅僅是由量子比特技術(shù)的發(fā)展鋪就的。在后臺工作的數(shù)模轉(zhuǎn)換器(DAC)和模數(shù)轉(zhuǎn)換器(ADC)也起著至關(guān)重要的作用。因此,隨著量子計算機(jī)復(fù)雜性的提高,這些模擬元件將變得越來越重要。

DAC 在量子控制中至關(guān)重要。它們用于將數(shù)字控制信號轉(zhuǎn)換成模擬電壓、光脈沖或微波脈沖,以控制量子比特和創(chuàng)建量子門。DAC 技術(shù)的進(jìn)步帶來了更快的速度和更高的精度,從而能夠更快、更精確地控制量子操作。

這些 DAC 允許使用復(fù)雜的脈沖序列和控制算法,從而提高了門的可靠性和量子算法的性能。量子門是在量子比特上執(zhí)行的基本操作,通過精心設(shè)計的控制信號來實(shí)現(xiàn)。每個量子比特通常需要 2 到 5 個 DAC。

這些 DAC 需要具備以下條件:

高分辨率和高速度

要精確操縱量子比特狀態(tài),需要具有高分辨率(8-12 位)的 DAC,以精確表示復(fù)雜的控制信號和快速沉淀時間(納秒或更快),確保將信號失真降至最低。隨著現(xiàn)代技術(shù)的發(fā)展,量子計算機(jī)的 DAC 采樣率正從每秒數(shù)十兆采樣 (MSPS) 提高到每秒 100 兆采樣 (MSPS) 甚至更高。

低噪音

數(shù)模轉(zhuǎn)換器引入的任何噪聲都可能導(dǎo)致控制信號出錯,從而影響量子運(yùn)算的保真度。

ADC 在量子控制中也至關(guān)重要。它們用于將測量量子比特的模擬信號轉(zhuǎn)換為可由標(biāo)準(zhǔn)控制系統(tǒng)處理的數(shù)字?jǐn)?shù)據(jù)。目前已經(jīng)開發(fā)出先進(jìn)的高分辨率轉(zhuǎn)換器,能夠以最小的噪聲和失真精確捕捉量子信號。

這些模數(shù)轉(zhuǎn)換器還能精確測量量子態(tài),為量子系統(tǒng)的糾錯和實(shí)時控制提供必要的反饋。執(zhí)行量子計算后,必須讀出量子比特狀態(tài)。這就需要監(jiān)測微弱信號,再由 ADC 轉(zhuǎn)換成數(shù)字形式。每個量子比特需要 1 到 3 個 ADC,具體取決于實(shí)現(xiàn)方式。

這些 ADC 需要具備以下條件:

高靈敏度和動態(tài)范圍

模數(shù)轉(zhuǎn)換器必須具有高靈敏度,才能捕捉到來自量子比特的微弱信號,并具有較寬的動態(tài)范圍,以便能夠處理全部電位值。通常,這些控制信號的分辨率應(yīng)在 5 到 12 位之間。

高速

快速采樣率的 ADC 是高效讀出所必需的,以便捕捉量子比特狀態(tài)的快速變化。與 DAC 一樣,量子計算機(jī)的 ADC 采樣率正在從每秒百萬次采樣(MSPS)提高到每秒數(shù)百次采樣(MSPS),甚至更高。

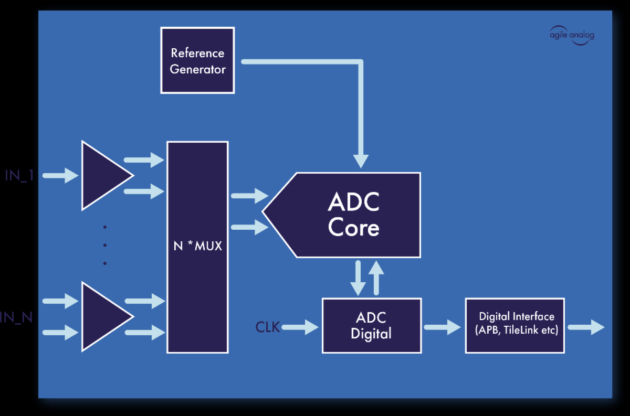

圖 1 高分辨率 ADC 可以精確捕捉量子信號,并將噪聲和失真降至最低。來源:Agile Analog 敏捷模擬

DAC 和 ADC 集成挑戰(zhàn)

將高性能 DAC 和 ADC 集成到量子計算系統(tǒng)中會面臨一些挑戰(zhàn):

微型化

隨著量子比特數(shù)量的增加,對緊湊型可擴(kuò)展 DAC 和 ADC 的需求也在增加。例如,如果每個量子比特需要 5 個 DAC 和 3 個 ADC,并且需要 1,000 個量子比特,那么就需要 8,000 個轉(zhuǎn)換器。因此,100 萬個量子比特需要 800 萬個轉(zhuǎn)換器。

集成

這些轉(zhuǎn)換器與量子比特控制和讀出電子設(shè)備的無縫集成對系統(tǒng)的高效運(yùn)行至關(guān)重要。

功耗

保持低功耗對量子計算機(jī)的整體能效至關(guān)重要。以 8000 或 800 萬個轉(zhuǎn)換器為例,如果這些轉(zhuǎn)換器的功耗都是 1 毫瓦,那么總功耗就是 8 瓦或 8000 瓦。這一切都會產(chǎn)生大量熱量,而現(xiàn)代低溫恒溫器的內(nèi)部耗散只能維持在 2 到 5 瓦之間。

目前面臨的主要挑戰(zhàn)是縮小面積、提高集成度、降低功耗,同時還要保持控制和測量量子比特所需的數(shù)據(jù)轉(zhuǎn)換器性能。

外部控制電子設(shè)備

控制電子元件與量子系統(tǒng)連接,實(shí)現(xiàn)精確控制和測量。目前,大多數(shù)量子計算機(jī)的控制電路,包括數(shù)模轉(zhuǎn)換器和模數(shù)轉(zhuǎn)換器,都安裝在量子比特所在的超低溫腔室(低溫恒溫器)外部。

這種方法雖然適用于小規(guī)模系統(tǒng),但在擴(kuò)展到數(shù)千甚至數(shù)百萬量子比特時卻遇到了瓶頸。問題包括

物理限制

可控制的量子比特數(shù)量受限于低溫恒溫器的物理限制。隨著量子比特數(shù)量的增加,為每個量子比特(包括用于 DAC 和 ADC 的電纜)鋪設(shè)大量控制電纜變得不切實(shí)際。

信號衰減

長控制電纜會導(dǎo)致信號衰減和噪聲,從而導(dǎo)致量子比特控制和讀出錯誤。隨著電纜長度的增加,這些誤差的可能性也會增加,從而影響量子運(yùn)算的保真度。

更高的復(fù)雜性

在低溫恒溫器外管理和布線眾多控制電纜會增加系統(tǒng)的復(fù)雜性,因此更難維護(hù)和擴(kuò)展。

在低溫恒溫器內(nèi)集成控制電子元件的優(yōu)勢

在低溫恒溫器內(nèi)直接集成控制電子元件,特別是 DAC 和 ADC,為解決可擴(kuò)展性難題提供了一種潛在的解決方案。它有助于為建造更大、更強(qiáng)大的量子計算機(jī)鋪平道路。

有以下幾個好處

提高可擴(kuò)展性

有了片上模擬控制電子元件,可控制的量子比特數(shù)量不再受限于低溫恒溫器饋入件的數(shù)量。這樣就能構(gòu)建更大、更復(fù)雜的量子電路。數(shù)字控制電路可以集成在低溫恒溫器內(nèi),或者由于數(shù)字信號固有的抗噪性,留在低溫恒溫器外。

減少信號衰減

通過將 DAC 和 ADC 放在離量子比特更近的位置,信號損耗和噪聲可降至最低,從而提高控制和讀出保真度。

簡化系統(tǒng)設(shè)計

將模擬控制電子元件集成在低溫恒溫器內(nèi)可降低系統(tǒng)的復(fù)雜性,從而使其更易于管理和維護(hù)。

在低溫恒溫器內(nèi)集成控制電子元件的挑戰(zhàn)

雖然在低溫恒溫器內(nèi)集成 DAC 和 ADC 有很多好處,但也存在一些挑戰(zhàn):

惡劣的低溫環(huán)境

為室溫操作而設(shè)計的 DAC 和 ADC 需要進(jìn)行調(diào)整,以便在低溫(通常為 4 開爾文左右)環(huán)境下可靠運(yùn)行。這需要專門的電路設(shè)計技術(shù)。雖然半導(dǎo)體工藝技術(shù)的工作溫度通常為 -40°C 至 125°C,但在這種低溫條件下設(shè)計時需要新的模型。此外,還必須對代工廠提供的基礎(chǔ)晶體管進(jìn)行改動,以便在這些低溫條件下實(shí)現(xiàn)最佳性能。

空間有限

要在量子比特附近的有限空間內(nèi)集成大量 DAC 和 ADC,就必須采用小型化和高密度封裝解決方案。

功耗

低溫恒溫器內(nèi)的散熱管理至關(guān)重要。為了避免影響系統(tǒng)的熱穩(wěn)定性,低功耗 DAC 和 ADC 至關(guān)重要。

量子計算機(jī)擴(kuò)展中的 DAC 和 ADC

隨著量子計算機(jī)的不斷發(fā)展,對高保真、低噪聲和高速模擬元件的需求只會變得更加重要。因此,Agile Analog 正在探索開發(fā)一系列低溫 DAC 和 ADC 的機(jī)會。設(shè)計團(tuán)隊在與超低功耗嵌入式存儲器專家 sureCore 合作的一個項(xiàng)目中獲得了一些相關(guān)挑戰(zhàn)的經(jīng)驗(yàn),該項(xiàng)目提供了一個低溫控制 ASIC,作為英國創(chuàng)新基金資助項(xiàng)目的一部分。

這些設(shè)計工作清楚地表明,DAC 和 ADC 將在量子計算機(jī)的擴(kuò)展過程中發(fā)揮關(guān)鍵作用,并將有助于加速量子計算機(jī)向更復(fù)雜的實(shí)際應(yīng)用發(fā)展。

-

adc

+關(guān)注

關(guān)注

98文章

6495瀏覽量

544461 -

dac

+關(guān)注

關(guān)注

43文章

2291瀏覽量

190975 -

模數(shù)轉(zhuǎn)換器

+關(guān)注

關(guān)注

26文章

3200瀏覽量

126810 -

量子計算機(jī)

+關(guān)注

關(guān)注

4文章

530瀏覽量

25415

原文標(biāo)題:為什么 DAC 和 ADC 對量子計算機(jī)的升級至關(guān)重要?

文章出處:【微信號:moorexuetang,微信公眾號:摩爾學(xué)堂】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

DAC和ADC對量子計算機(jī)升級的重要性解析?

DAC和ADC對量子計算機(jī)升級的重要性解析?

評論