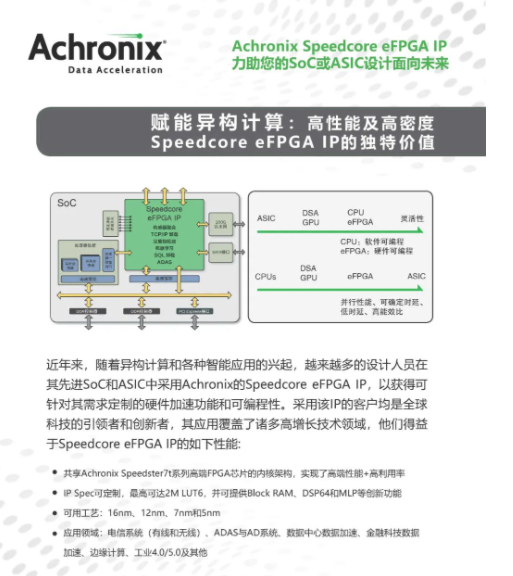

Speedcore嵌入式FPGA(embedded FPGA,eFPGA)知識產(chǎn)權(quán)(IP)產(chǎn)品是Achronix公司于2016年推出的顛覆性技術(shù),并于當(dāng)年開始向最終客戶交付,目前出貨量已經(jīng)超過2500萬。

Achronix的第四代Speedcore eFPGA IP(Speedcore Gen4),該產(chǎn)品添加了機器學(xué)習(xí)處理器(MLP)模塊,在保留原有功能的基礎(chǔ)上,將性能提高了60%、功耗降低了50%、芯片面積減少65%,可為需要大量計算和I/O帶寬的全新人工智能/機器學(xué)習(xí)及高性能應(yīng)用提供強有力的支持。Speedcore Gen4在多個工藝節(jié)點上可用,包括臺積電(TSMC)的7納米工藝技術(shù)等。

利用Speedcore eFPGA IP,客戶可以將FPGA功能集成到他們的SoC中,使他們既可以擁有在ASIC中才能實現(xiàn)的最佳硬件加速平衡,又可以擁有FPGA技術(shù)的靈活性和可編程性。

本文詳細介紹了Speedcore eFPGA的特性和功能,歡迎您閱讀,以進一步了解該產(chǎn)品。您也可以在Achronix微信公眾號的“產(chǎn)品介紹”欄目中隨時閱讀本文。

產(chǎn)品亮點

Speedcore嵌入式FPGA(eFPGA)知識產(chǎn)權(quán)(IP)——唯一一款已在各種大規(guī)模量產(chǎn)應(yīng)用中采用的eFPGA技術(shù)。

客戶可自定義eFPGA的資源,包括邏輯資源、RAM資源、機器學(xué)習(xí)處理器(MLP)/DSP模塊、二維片上網(wǎng)絡(luò)(2D NoC):

邏輯單元——6輸入查找表(LUT),并且集成了廣泛的MUX函數(shù)和快速加法器

邏輯RAM —— LRAM2k每個存儲模塊的容量為2kb;LRAM4k每個存儲模塊的容量為4kb

塊RAM —— BRAM72k每個存儲模塊的容量為72kb;BRAM20k每個存儲模塊的容量為20kb

DSP64模塊——每個模塊都帶有18×27乘法器、64位累加器和27位預(yù)加器

機器學(xué)習(xí)處理器(MLP)——在DSP64基礎(chǔ)上做了升級。支持整數(shù)(int4/int8/in16/int32)和浮點格式(FP24,FP16,bfloat16)。對不同的乘法器精度,每個MLP可支持的乘法器數(shù)量會不同,最多支持32個乘法器/累加器(MAC)

2D NoC——用戶還可以在定制二維片上網(wǎng)絡(luò)2D NoC,以實現(xiàn)大帶寬的高效數(shù)據(jù)交互。

客戶自定義的模塊

Achronix以一個GDSII的形式提供eFPGA IP。

SpeedcoreIP在以下工藝技術(shù)節(jié)點上可用:

TSMC 16FFC

TSMC 12FFC

TSMC N7/N6

TSMC N3A

SpeedcoreIP也可以移植到其他工藝節(jié)點上

Speedcore的性能:

最高運行頻率:750MHz

典型運行頻率:300MHz-500MHz

延遲最低的接口:

在Speedcore實例與宿主SoC之間僅有一步延遲

支持零延遲接口

Achronix的ACE設(shè)計工具可為Speedcore IP提供支持:

功能齊全的工具可為以Speedcore eFPGA為目標(biāo)的RTL進行綜合、布局、布線和優(yōu)化性能等操作

包括用于綜合的Synplify Pro工具

易于評估:

使用Achronix的ACE設(shè)計工具進行基準(zhǔn)測試的設(shè)計

使用VectorPath加速卡驗證功能

Speedcore eFPGA IP為ASIC和SoC帶來了可編程邏輯的強大功能和靈活性。客戶明確其邏輯LUT、RAM、MLP/DSP資源、NoC等需求,然后Achronix就會配置滿足其個性化需求的Speedcore IP。Speedcore查找表(LUT)、RAM、MLP和DSP64模塊等可以像積木一樣進行組裝,從而為任何給定的應(yīng)用創(chuàng)建優(yōu)化的可編程結(jié)構(gòu)。在Speedcore IP的交付包中,還包括一個ACE設(shè)計工具的個性化版本,用于對Speedcore IP進行編程。

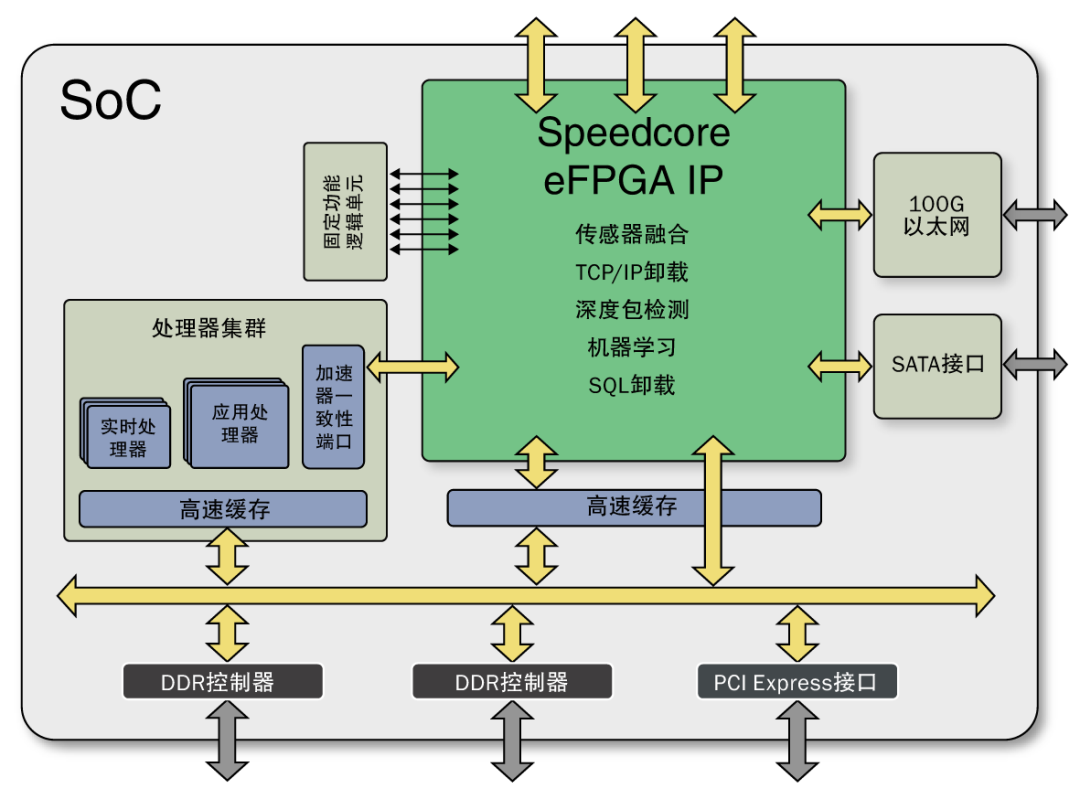

Speedcore集成框圖

Speedcore eFPGA技術(shù)已實現(xiàn)量產(chǎn),并且自2016年起開始交付給最終客戶,目前出貨量已經(jīng)超過2500萬。Achronix的客戶包括一些全球最大的科技公司。這些公司已經(jīng)認識到Speedcore IP是一種顛覆性技術(shù),可以使他們顯著提高其系統(tǒng)的整體性能。

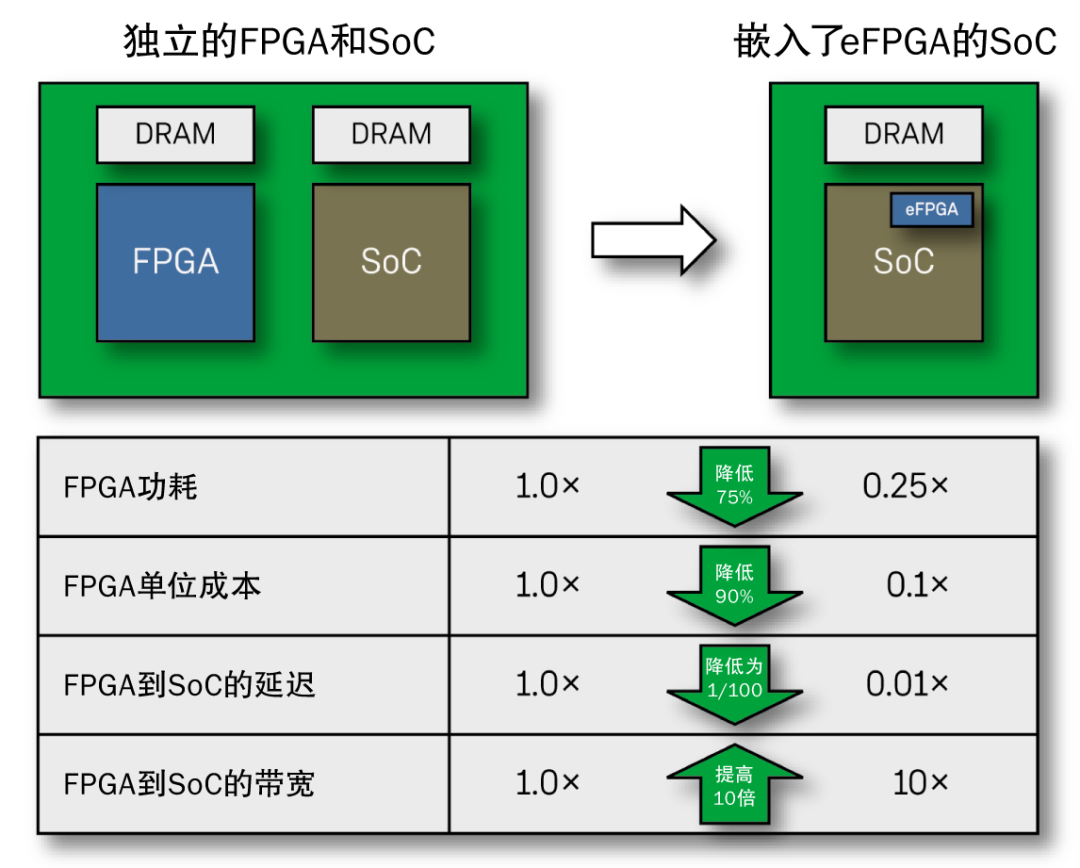

在SoC中嵌入Speedcore技術(shù)將帶來諸多好處,與一款獨立的FPGA芯片相比,Speedcore eFPGA IP提供了以下優(yōu)點:

降低75%的功耗

節(jié)省90%的成本

1/100的延遲

高10倍的帶寬

Speedcore eFPGA可以最小化芯片面積,提高性能,降低功耗,減少成本并且令SoC設(shè)計歷久彌新

經(jīng)過驗證的技術(shù)

構(gòu)建SoC的成本和風(fēng)險非常高,不能冒險使用未經(jīng)驗證的嵌入式IP。Achronix是唯一一家可以同時大批量生產(chǎn)并交付eFPGA和獨立FPGA的公司。設(shè)計人員可以100%確信SpeedcoreIP將會正常工作,因為它已得到全面的驗證,并且經(jīng)過了流片驗證。

工藝技術(shù)

Speedcore IP在臺積電的16FFC, 12FFC,N7/N6, N3A工藝節(jié)點上均可用。對于其他工藝技術(shù),Achronix可以輕松移植SpeedcoreIP以支持其需求。請聯(lián)系A(chǔ)chronix獲取更多關(guān)于移植Speedcore技術(shù)的詳細信息。

評估Speedcore eFPGA

在將Speedcore技術(shù)部署于SoC中之前,Achronix可以輕松地對其進行評估:

通過使用一個Speedcore eFPGA的示例實例,Achronix的ACE設(shè)計工具可被用來編譯設(shè)計,以對性能、資源使用率和編譯時間等進行評估。

Achronix使用其Speedcore芯片尺寸生成器(Speedcore Die Size Builder)工具來估算eFPGA實例的大小。

評估設(shè)計可以被加載到Achronix的VectorPath加速卡中,以驗證功能和性能。

此外,SpeedcoreIP附帶超過一千頁的詳細文檔,以幫助您將該技術(shù)集成到您的SoC中。Achronix還提供了如下一些現(xiàn)場教程:

基準(zhǔn)測試和評估

物理設(shè)計實現(xiàn)

時鐘和復(fù)位網(wǎng)絡(luò)設(shè)計

時序收斂

配置

驗證

Speedcore支持廣泛的應(yīng)用

將Speedcore技術(shù)嵌入復(fù)雜的器件中,除了這些直接客觀上的各項優(yōu)勢,設(shè)計人員還可以為其SoC設(shè)計增加獨有的、長期的價值。Speedcore IP內(nèi)核作為可重新配置的協(xié)處理器和硬件加速器來支持各種各樣的任務(wù),相比面向字的(word-oriented)CPU架構(gòu),這些任務(wù)在面向位的(bit-oriented)FPGA架構(gòu)上執(zhí)行時顯然更加高效——諸如SQL卸載引擎、inline I/O處理、加密、搜索引擎算法加速、壓縮和增強多媒體處理等功能。無論是使用Speedcore技術(shù)已實現(xiàn)量產(chǎn)的應(yīng)用,還是目前正在由SoC設(shè)計人員使用Speedcore IP實現(xiàn)的應(yīng)用,其范圍都在不斷擴大。

關(guān)于Achronix半導(dǎo)體公司

Achronix半導(dǎo)體公司是一家私有的、采用無晶圓廠模式的半導(dǎo)體公司,總部位于美國加利福尼亞州圣克拉拉市,同時提供高性能FPGA和嵌入式FPGA(eFPGA)解決方案。Achronix歷來都是高性能FPGA市場向前發(fā)展的推動者之一。Achronix提供的產(chǎn)品包括可編程的FPGA結(jié)構(gòu),具有硬連線系統(tǒng)級模塊的高性能、高密度獨立FPGA,數(shù)據(jù)中心和高性能計算(HPC)硬件加速器板,以及支持所有Achronix產(chǎn)品的一流EDA軟件。公司在美國、歐洲和中國都設(shè)有銷售辦公室和代表處,在印度班加羅爾設(shè)有一間研發(fā)和設(shè)計辦公室。

-

處理器

+關(guān)注

關(guān)注

68文章

19814瀏覽量

233645 -

嵌入式

+關(guān)注

關(guān)注

5141文章

19551瀏覽量

315248 -

Achronix

+關(guān)注

關(guān)注

1文章

76瀏覽量

22716 -

efpga

+關(guān)注

關(guān)注

1文章

33瀏覽量

15827

原文標(biāo)題:Speedcore eFPGA產(chǎn)品介紹

文章出處:【微信號:Achronix,微信公眾號:Achronix】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

Achronix的Speedcore? Custom Blocks定制單元塊為數(shù)據(jù)加速系統(tǒng)再添動力

?Achronix定制單元塊大幅提升Speedcore eFPGA性能

Achronix宣布用于SoC加速的Speedcore嵌入式FPGA IP產(chǎn)品開始供貨

全新Speedcore標(biāo)準(zhǔn)比FPGA更高效,大幅縮減芯片面積及功耗

Achronix宣布為其eFPGA IP解決方案推出定制單元塊

Achronix宣布:已完成SpeedcoreTM eFPGA量產(chǎn)驗證芯片的全芯片驗證

Achronix與Mentor攜手帶來高等級邏輯綜合(HLS)與FPGA技術(shù)之間的連接

解密:Achronix 7nm eFPGA的設(shè)計方法

Achronix半導(dǎo)體全面對接Speedcore eFPGA技術(shù)

Achronix推出其第四代嵌入式FPGA產(chǎn)品

Achronix推出全新EFPGA項目,幫工程師快速構(gòu)建低成本測試芯片!

Achronix宣布其Speedcore eFPGA IP核出貨量超千萬個

Achronix Speedcore eFPGA IP性能介紹

評論