歡迎關注虹科,為您提供最新資訊!

導讀

汽車電子和工業自動化領域對通信網絡的帶寬和可靠性要求日益提高。CAN通信已經從最初的1Mbit/s速率發展到如今CAN XL數據幀在FAST模式下可達20Mbit/s的高速傳輸。本文將詳細介紹CAN XL網絡中的物理層革新與優勢,包括CAN技術的演進、物理層的關鍵技術、FAST模式下的阻抗特性以及CAN XL網絡的驗證等方面。

01****CAN總線技術的演進與物理層革新

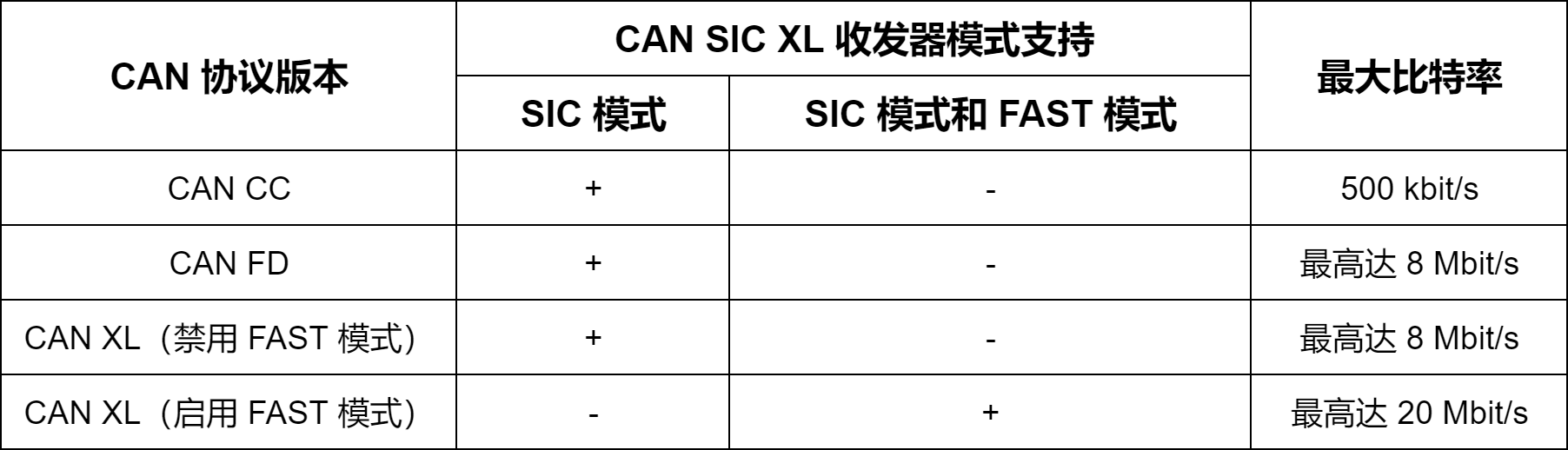

在CAN總線技術發展之初,1Mbit/s是最高比特率。如今,當使用CAN SIC XL收發器并啟用FAST模式時, 在CAN XL數據幀的數據階段,可實現高達20Mbit/s的速度 。通過一個使用CAN XL協議控制器和CAN SIC XL收發器的CAN節點,可以憑借不同配置實現CAN CC、CAN FD和CAN XL通信,而無需硬件修改,僅需不同的協議控制器配置。

CAN通信的一個重要優勢是其物理層支持多點網絡,該網絡所有節點可同時接收CAN幀,無需交換機,且節點間無傳播延遲。為了組織這種通信,特別是在開始時,需要一個仲裁階段。 在仲裁階段,所有節點在網絡上傳輸邏輯“1”或邏輯“0”。 為了在不損壞節點或不在網絡上傳輸未定義的信號電平的情況下實現這一點,只有“0”作為顯性信號在網絡上被主動傳輸,而“1”由終端電阻被動產生,被稱為隱性電平。

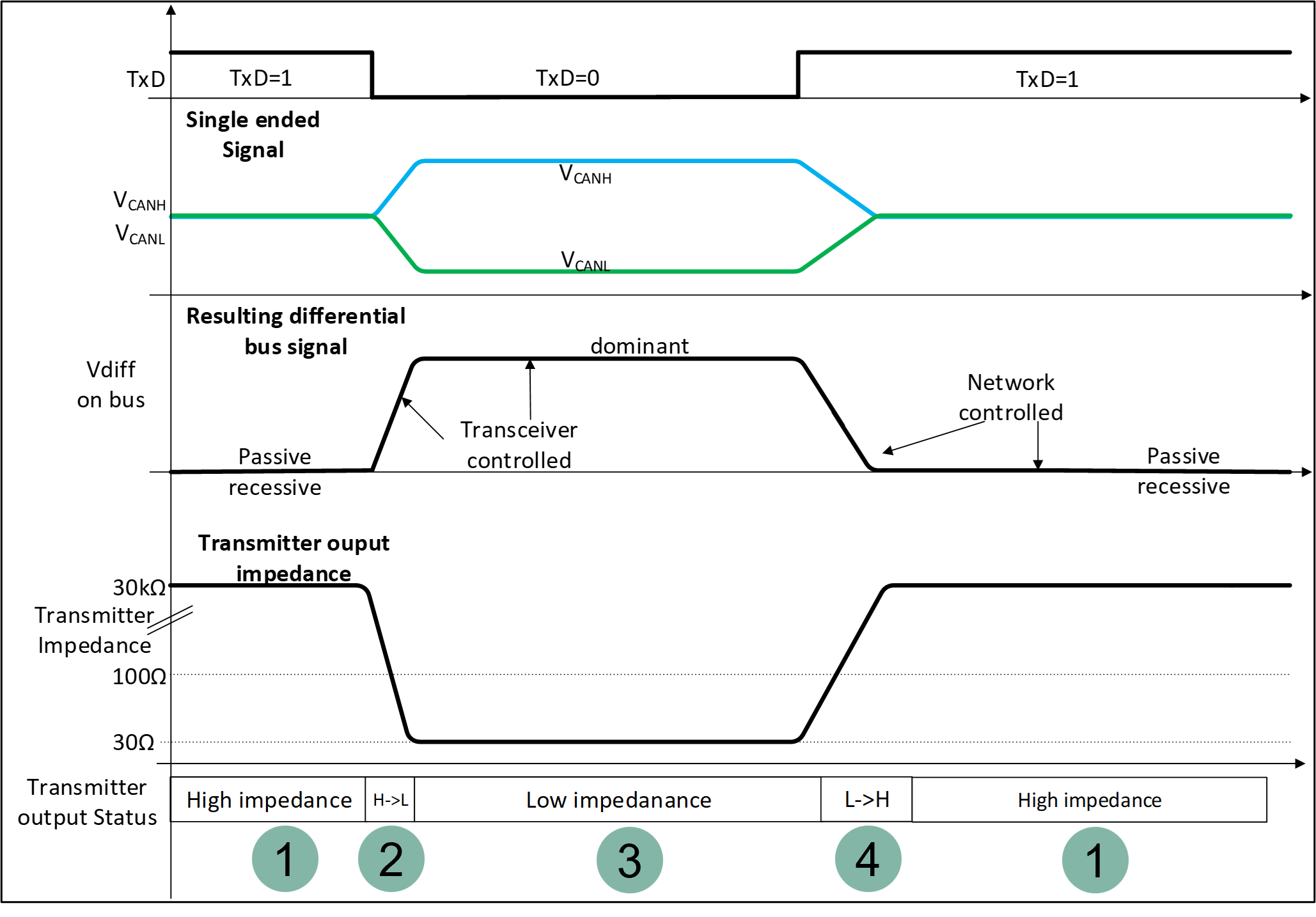

圖1 CAN FD收發器阻抗(來源:英飛凌)

圖1中展示了收發器的輸出行為。收發器在高阻抗(以允許網絡上的隱性電平)和低阻抗(以產生顯性電平)之間切換。隱性到顯性的轉換由收發器控制,而在顯性到隱性的轉換期間,最大可能的轉換速率僅由收發器限制。這種轉換主要由線束和終端電阻控制。在傳輸顯性和隱性信號期間,收發器輸出阻抗的不斷變化會在網絡上引起振鈴。這種振鈴限制了CAN網絡中的最大可能比特率。

02****物理層的關鍵技術與FAST模式阻抗特性

為了實現更高的比特率,CAN XL技術對收發器概念進行了重要修改。圖2中展示了SIC收發器輸出阻抗的行為,顯性到隱性階段也由收發器控制。輸出阻抗現在從顯性階段的低阻抗變為100歐姆的中阻抗,持續時間最多為500納秒。這個階段稱為有源隱性階段。在有源隱性階段之后,收發器輸出阻抗從中阻抗變為高阻抗,以允許網絡上的碰撞。這個階段稱為無源隱性階段。在SIC階段選擇100歐姆的阻抗是為了使收發器阻抗與典型的CAN雙絞線阻抗(100歐姆)相匹配。

圖2 CAN SIC收發器輸出阻抗特性(來源:英飛凌)

這種修改提高了現有CAN FD網絡的可靠性,使其比特率高達8Mbit/s。為了使CAN XL實現超過8Mbit/s的比特率,需要一個新的收發器概念。 在仲裁階段,采用CAN SIC 收發器概念,即 SIC 模式;在數據階段,選用推挽收發器概念,此模式稱為 FAST 模式,可實現高達 20Mbit/s 的比特率。 在CAN XL協議的ADS(仲裁到數據序列)階段,收發器從SIC模式切換到FAST模式。模式切換由CAN XL協議控制器通過TxD引腳控制。在FAST模式下的阻抗與有源隱性SIC模式下的阻抗相同,均為100歐姆。但是由于交替波形,傳輸比特的對稱性比SIC模式更好,允許比特率高達20Mbit/s。

圖3 從SIC到FAST模式轉換期間發射器的阻抗特性(來源:英飛凌)

圖3展示了 SIC XL發射器在SIC模式到FAST模式轉換期間和在FAST模式下的阻抗特性。 轉換從顯性電平變為level_0,然后變為level_1。從顯性變為level_0是為了獲得與FAST模式相同的電壓擺幅。否則,在轉換階段,由于更高的電壓擺幅引起的振鈴必須單獨分析。在圖4中,展示了 在數據階段結束時從FAST模式到SIC模式的模式轉換 。在整個FAST模式階段(與數據階段相同),阻抗恒定為100歐姆,與導線阻抗匹配。

圖4 從FAST到SIC模式轉換器件發射器的阻抗特性(來源:英飛凌)

從SIC模式到FAST模式的模式轉換 由CAN XL控制器通過TxD引腳控制 。在仲裁階段,TxD信號與所有其他類型的收發器相同。TxD高電平控制網絡上的隱性電平,TxD低電平控制網絡上的顯性電平。 在FAST模式下,控制器向收發器發送PWM編碼(脈寬調制)符號 。PWM符號的長度可以在50納秒到200納秒之間變化。如果收發器檢測到這個PWM符號,收發器將模式從SIC切換到FAST,如果不再檢測到符號,收發器切換回SIC模式。PWM符號的占空比代表將傳輸到網絡的電平。如果占空比小于50%,這代表邏輯0,并且將level_0(正差分信號)傳輸到網絡線路。如果占空比大于50%,這代表邏輯1,并且將level_1(負差分信號)傳輸到網絡。

不僅在數據階段使用PWM信號控制發送收發器,接收收發器也使用PWM信號切換到FAST模式。在FAST模式下,接收器閾值設置為0V,而在SIC模式下為700mV。這保證了CAN XL控制器和CAN SIC XL收發器始終處于相同的模式。例如,不會由于錯誤而導致不匹配。

03****CAN XL網絡的驗證與測試

為了確保CAN XL網絡的可靠性和性能,需要進行嚴格的驗證和測試。在此過程中,針對CAN XL數據幀的關鍵應用場景進行深入分析,對于評估網絡的穩定性和整體性能具有至關重要的作用。

1、關鍵場景的驗證

CAN XL數據幀中最關鍵的場景包括:1. 從SIC模式到FAST模式的轉換;2. 短位的突發;3. 在長電平_0或電平_1階段(根據stuff-bit規則最多連續11位)后接一個短位(與前一位相反的電平)。

在ADH(仲裁到數據高)位期間,收發器從顯性切換到level_0,然后切換到level_1,同時所有接收節點更改接收器閾值。這是通過CAN XL控制器發送到收發器TxD引腳的PWM編碼符號來實現的。

圖5 ADS域中SIC模式到FAST模式的轉換(來源:英飛凌)

在TxD引腳檢測到PWM編碼符號之前,接收節點發送一個短顯性脈沖,隨后是縮短的SIC階段。要求是在SDT(服務數據單元類型)字段開始之前,level 1必須穩定。此外,DL1(數據低)位的長度也很重要。從DH2(數據高)位到DL1位的轉換用于在進入數據階段后重新同步CAN XL協議控制器。此外,還應達到level_0。在SDT字段中選擇了“0101”位模式來分析在高比特率情況下短位的影響。

圖6 長相位后的Level_1或Level_0位(來源:英飛凌)

此外,在相同電平的大量位(連續level_1或level_0位的最高可能數量)之后的短位也是一個關鍵情況。應該使用在連續11位相同電平后接的一個位來進行調查。目標是找出在CAN XL數據幀中最長的相同電平階段后,短位的比特長度和電平如何表現。

2、測試標準計時

對于驗證,應使用在+100 mV和 -100 mV閾值處測量的比特時間長度。比特時間應接近標稱比特時間或其倍數。對于高比特率,也可以使用0 V閾值。可以忽略長度為20 ns的毛刺。

圖7 測試標準計時(來源:英飛凌)

此外,還應分析短位的電平,并且應至少達到標稱電平的80%。為了更輕松地驗證CAN XL網絡,CiA成員正在為CAN XL數據幀中的眼圖制定建議。

本文詳細介紹了CAN XL網絡中的物理層革新與優勢,包括CAN技術的演進、物理層的關鍵技術、FAST模式下的阻抗特性以及CAN XL網絡的驗證等方面。 在下篇中,我們將進一步探討CAN XL網絡在實際應用中的組合與兼容性問題,以及如何選擇合適的物理層選項來優化網絡性能。 敬請期待!

文章來源:本文基于Magnus Hell(英飛凌汽車網絡技術首席負責人兼CiA技術總監)在第18屆國際CAN大會(iCC)及2024年虹科CAN XL國際研討會的演講。論文已刊于《第18屆iCC會議論文集》2024版,由CiA出版。虹科智能互聯團隊翻譯并分享,旨在與行業同仁分享前沿技術成果。

審核編輯 黃宇

-

CAN

+關注

關注

57文章

2744瀏覽量

463613 -

協議控制器

+關注

關注

0文章

16瀏覽量

6455 -

CAN總線技術

+關注

關注

1文章

7瀏覽量

5027

發布評論請先 登錄

相關推薦

CAN物理層調試基礎知識及舉例

淺談CAN總線物理層

CAN總線不同的物理層

什么是以太網物理層?Ethernet物理層有哪些功能?

如何對CAN物理層進行調試?

ISO11898物理層特性

IIC物理層是由哪些部分組成的

WCDMA 物理層(英)

WCDMA系統的物理層(FDD)

物理層的作用

PCIe物理層接口定義了物理層中的,媒介層和物理編碼子層之間的統一接口

CAN XL物理層探秘(上):革新要點與顯著優勢

CAN XL物理層探秘(上):革新要點與顯著優勢

評論