電子封裝正朝著更小尺寸、更強(qiáng)性能、更優(yōu)電氣和熱性能、更高I/O數(shù)量和更高可靠性的方向飛速發(fā)展。然而,傳統(tǒng)的Sn基焊料互連封裝技術(shù),盡管具有低鍵合溫度和低成本等優(yōu)勢,其局限性也日益凸顯,如焊料外溢、電氣性能較差以及焊接溫度導(dǎo)致的芯片或基板翹曲等問題。在這樣的背景下,先進(jìn)封裝技術(shù)應(yīng)運(yùn)而生,成為推動半導(dǎo)體行業(yè)繼續(xù)前行的關(guān)鍵力量。

一、集成電路封裝發(fā)展概況

半導(dǎo)體業(yè)界已明確五大增長引擎,這些應(yīng)用推動了電子封裝技術(shù)的不斷進(jìn)步。移動和便攜式設(shè)備,如智能手機(jī)、智能手表和筆記本電腦,要求封裝尺寸更小、重量更輕,同時保持高性能和低功耗。高性能計算(HPC)則對處理速度和計算能力提出了更高要求。自動駕駛汽車和物聯(lián)網(wǎng)(IoT)則需要高度集成、低功耗和長壽命的封裝解決方案。大數(shù)據(jù)(云計算)和即時數(shù)據(jù)(邊緣計算)應(yīng)用則要求封裝具有高帶寬和低延遲。

目前,大規(guī)模回流焊工藝和熱壓焊技術(shù)是電子組件中兩種廣泛使用的互連封裝技術(shù)。然而,Sn基焊料的電氣性能較差,且焊接溫度較高,容易導(dǎo)致芯片或基板翹曲,限制了其進(jìn)一步發(fā)展。因此,業(yè)界迫切需要尋找新的封裝技術(shù),以滿足未來應(yīng)用的需求。

二、先進(jìn)封裝技術(shù)的誕生

隨著集成電路產(chǎn)業(yè)的不斷發(fā)展,摩爾定律在傳統(tǒng)半導(dǎo)體行業(yè)面臨挑戰(zhàn)。為了維持半導(dǎo)體行業(yè)的發(fā)展,業(yè)界提出了More Moore和More than Moore兩條路徑。More Moore路徑致力于晶體管的不斷縮放以提高性能,而More than Moore路徑則通過電路設(shè)計、系統(tǒng)算法優(yōu)化或封裝技術(shù)來提高芯片的性能。然而,隨著先進(jìn)制程逐漸向原子尺寸逼近,晶體管的制造難度呈指數(shù)級增加,且成本高昂,量產(chǎn)進(jìn)度落后于預(yù)期。

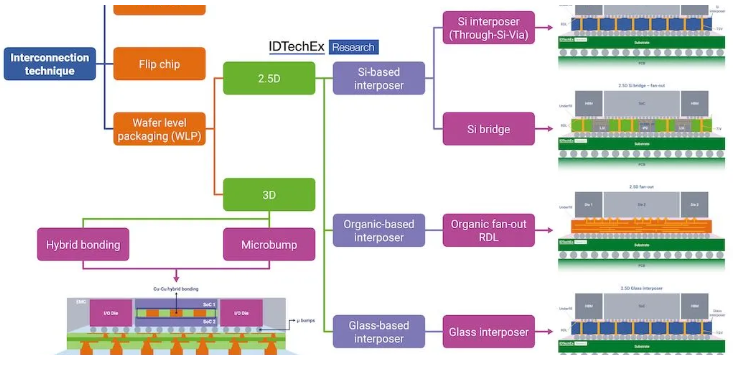

在這樣的背景下,先進(jìn)封裝技術(shù)登上歷史舞臺,成為拓展摩爾定律技術(shù)路線的重要方向。目前,已經(jīng)出現(xiàn)許多先進(jìn)的封裝技術(shù),如2-D扇出(芯片優(yōu)先)IC集成、2-D倒裝芯片集成、封裝上封裝(PoP)、封裝中系統(tǒng)(SiP)、μ凸點(diǎn)3-D IC集成和無凸點(diǎn)3-D IC集成等。

為了提高互連密度,IBM提出了倒裝鍵合(Flip Chip)技術(shù),利用焊錫凸點(diǎn)將芯片與芯片鍵合在一起。然而,當(dāng)互連密度提高到一定地步時,焊點(diǎn)將很容易完全轉(zhuǎn)化為金屬間化合物(IMC),進(jìn)而降低焊點(diǎn)的機(jī)械性能與導(dǎo)電性能。因此,業(yè)界開始探索銅銅直接鍵合技術(shù),其中銅銅混合鍵合技術(shù)已經(jīng)得到了應(yīng)用。該技術(shù)將銅焊點(diǎn)鑲嵌在介電材料中,并利用熱處理同時鍵合兩種材料,由于固態(tài)的銅原子會發(fā)生擴(kuò)散,因而可以實現(xiàn)鍵合。整個過程一直處于固態(tài),因此不會有橋接問題,且能顯著提升焊點(diǎn)密度和降低信號傳導(dǎo)所需的能量。

三、銅銅互聯(lián)封裝技術(shù)應(yīng)用

硅通孔技術(shù)(TSV)

硅通孔技術(shù)是通過在硅孔中填充鎢、銅、多晶硅等導(dǎo)電物質(zhì),形成垂直方向上的電氣互連。TSV技術(shù)避免了長布線帶來的尺寸限制和信號延遲等問題,有效減小了封裝體的尺寸。相對于二維封裝技術(shù),TSV具有更強(qiáng)的電氣性能、更高的堆疊密度和更寬的帶寬,同時功耗更低。因此,TSV技術(shù)非常適合便攜式電子產(chǎn)品和物聯(lián)網(wǎng)/可穿戴設(shè)備等應(yīng)用。

然而,TSV的填充工藝具有較大難度,因為硅通孔的孔徑較小且比較深,高深寬比使得其有較大的表面張力,并且孔外的電流密度一般高于孔內(nèi),物質(zhì)很難擴(kuò)散到孔內(nèi)部。因此,業(yè)內(nèi)的科研人員圍繞TSV的填充工藝展開了大量研究,以降低成本并提高沉積速率。

再布線層技術(shù)(RDL)

為了不斷擴(kuò)展摩爾定律,除了晶體管的新型納米技術(shù)的發(fā)展外,2.5D和3D的先進(jìn)封裝技術(shù)也在快速發(fā)展。在集成扇出(InFO)封裝中引入再分配層(RDL)可實現(xiàn)更好的集成能力和更低的成本。便攜設(shè)備中芯片的厚度限制抑制了其散熱能力,因此下一代移動應(yīng)用需要提高熱性能。預(yù)計由RDL技術(shù)制造的并排封裝將是未來的移動封裝解決方案,因為與PoP相比,并排結(jié)構(gòu)可以增加芯片厚度,并且RDL可以通過用RDL代替?zhèn)鹘y(tǒng)印刷電路板(PCB)來提供小的形狀因數(shù),從而提高熱性能。然而,需要解決與臺階高度、翹曲、底切和泄漏相關(guān)的關(guān)鍵挑戰(zhàn),以實現(xiàn)精細(xì)間距RDL集成。

電鍍銅是RDL工藝制造的重要步驟之一。由于RDL具有直徑小于50μm的盲孔和節(jié)距范圍為50μm至20μm甚至更小的布線,因此通孔填充能力和均勻性仍然是該應(yīng)用的主要挑戰(zhàn)。

銅柱凸點(diǎn)技術(shù)

隨著I/O密度的提高,傳統(tǒng)的焊料凸塊封裝工藝已經(jīng)無法滿足使用需求。C2(Chip Connection)技術(shù)逐漸成為主流,與C4技術(shù)中的焊球相比,銅柱直徑不受高度影響,因此可以進(jìn)一步縮小節(jié)距。銅柱凸點(diǎn)的主要制作工藝包括物理氣相沉積(PVD)、光刻、電鍍、蝕刻和回流焊。銅柱凸點(diǎn)技術(shù)不僅提高了互連密度,還提升了電氣性能和可靠性。

電鍍鍵合技術(shù)

電鍍鍵合技術(shù)是在兩個微結(jié)構(gòu)之間進(jìn)行互連或接觸的作用。使用這種電鍍鍵合工藝可以應(yīng)用于芯片封裝。電鍍鍵合技術(shù)通過將兩個承載要連接的金屬結(jié)構(gòu)的基板連接在一起,然后浸入電鍍?nèi)芤褐胁⑾蛲妼邮┘与妱荩菇饘俪练e在陰極并結(jié)合形成連接。多種金屬電鍍?nèi)芤嚎捎糜陔婂兘雍希–u、Au、Ni、Ni/Fe和多種其他金屬。電鍍鍵合技術(shù)具有工藝簡單、成本低廉和可靠性高等優(yōu)點(diǎn),在先進(jìn)封裝技術(shù)中具有廣泛的應(yīng)用前景。

銅銅直接鍵合技術(shù)以其獨(dú)特的優(yōu)勢,在先進(jìn)封裝技術(shù)中占據(jù)了重要地位。在鍵合過程中,銅一直處于固態(tài),不會產(chǎn)生外溢,可實現(xiàn)窄節(jié)距互連。銅具有低電阻率、強(qiáng)抗電遷移能力、快速導(dǎo)熱和優(yōu)秀的機(jī)械性能等優(yōu)點(diǎn),同時具有良好的工藝兼容性和較低的成本。因此,銅銅直接鍵合技術(shù)可實現(xiàn)高密度、高可靠性的互連。

-

集成電路

+關(guān)注

關(guān)注

5387文章

11530瀏覽量

361639 -

先進(jìn)封裝

+關(guān)注

關(guān)注

2文章

400瀏覽量

241

原文標(biāo)題:【芯片封裝】先進(jìn)封裝銅互聯(lián)技術(shù),如何重塑電子世界?

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

CoWoS先進(jìn)封裝技術(shù)介紹

人工智能半導(dǎo)體及先進(jìn)封裝技術(shù)發(fā)展趨勢

中國半導(dǎo)體產(chǎn)業(yè):面臨關(guān)鍵時刻的抉擇

AI與HPC技術(shù)推動先進(jìn)封裝行業(yè)發(fā)展

半導(dǎo)體封裝技術(shù)的類型和區(qū)別

晶圓廠與封測廠攜手,共筑先進(jìn)封裝新未來

半導(dǎo)體靶材:推動半導(dǎo)體技術(shù)飛躍的核心力量

半導(dǎo)體行業(yè)回暖,萬年芯深耕高端封裝

喜訊 | MDD辰達(dá)半導(dǎo)體榮獲藍(lán)點(diǎn)獎“最具投資價值獎”

玻璃基板時代,TGV技術(shù)引領(lǐng)基板封裝

半導(dǎo)體封裝技術(shù)的可靠性挑戰(zhàn)與解決方案

半導(dǎo)體發(fā)展的四個時代

半導(dǎo)體發(fā)展的四個時代

半導(dǎo)體先進(jìn)封裝技術(shù)

先進(jìn)封裝技術(shù)推動半導(dǎo)體行業(yè)繼續(xù)前行的關(guān)鍵力量

先進(jìn)封裝技術(shù)推動半導(dǎo)體行業(yè)繼續(xù)前行的關(guān)鍵力量

評論