01

整體概括

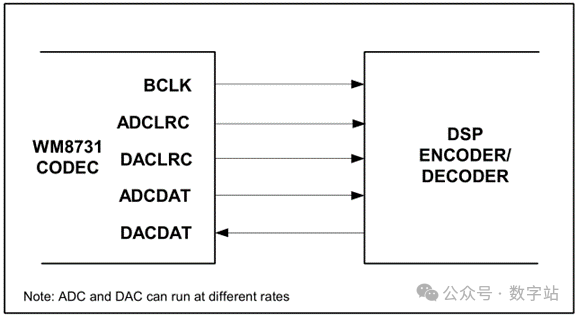

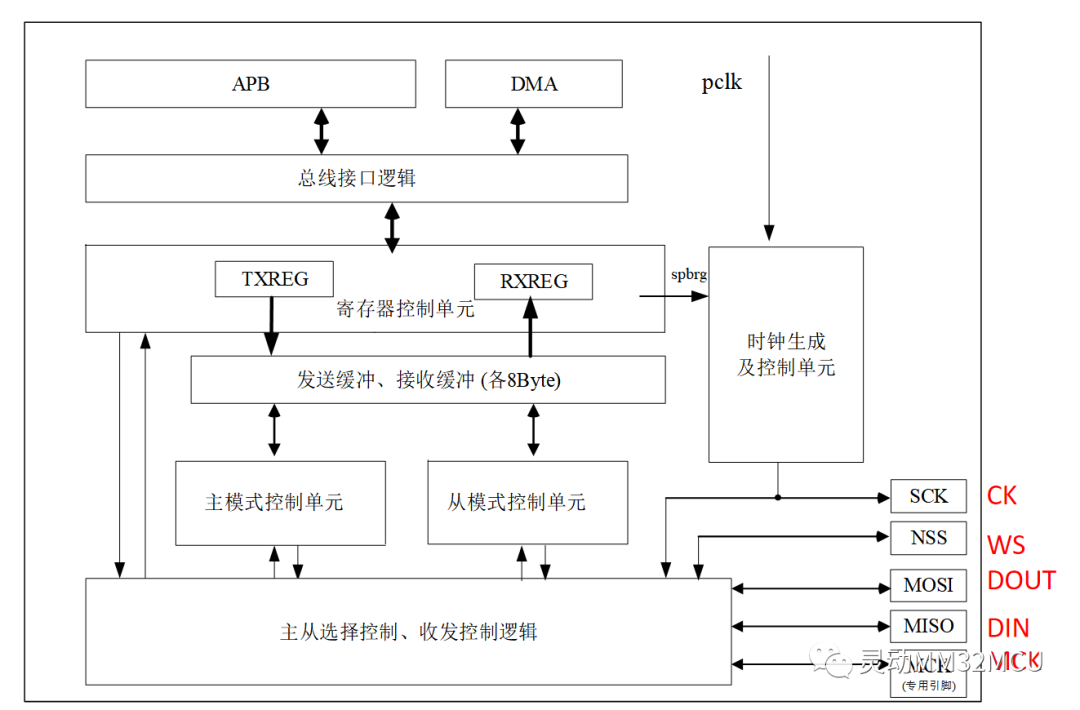

最近調試了一款音頻采集芯片wm8731,包含兩路音頻輸入(ADC)和一路音頻輸出(DAC),音頻芯片與主控芯片通過I2S接口傳輸ADC采集的數據和DAC驅動數據。

本文簡要講解一下I2S協議,該協議包含ADCRC(ADC采集數據的左右聲道指示信號)、DACRC(DAC采集數據的左右聲道指示信號)、BCLK(位數據對齊時鐘)、ADCDAT(ADC輸出數據)、DACDAT(DAC采集數據)共五個信號。

WM8731通過ADCRC、BCLK、ADCDAT三個信號傳輸ADC采集的數據,DACRC、BCLK、DACDAT三個信號傳輸驅動DAC的數據,ADC和DAC的數據通道共用BCLK信號。ADCDAT和DACDAT均在BCALK的下降沿變化,在BCLK上升沿保持不變。

WM8371的I2S接口包含主機和從機兩種模式,兩種模式的區別在于時鐘(BCLK)和聲道指示信號(ADCLRC、DACLRC)由主控芯片還是WM8371提供。

圖1是WM8371的主機模式,時鐘和聲道指示信號均由WM8371提供。

圖1 主機模式

下圖是WM8731的從機模式,時鐘和聲道指示信號均由WM8371提供,通過配置內部寄存器實現模式選擇,使用FPGA作為主控時,兩種模式均可使用,后續詳解。![]()

圖2 從機模式

02

I2S協議的四種模式

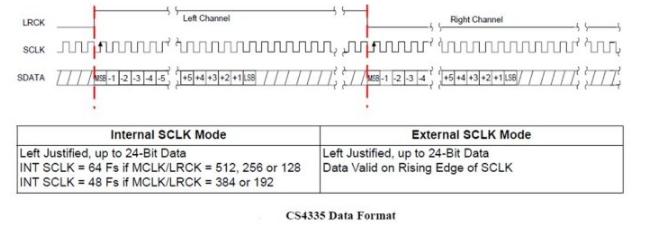

I2S總線根據ADCDAT和DACDAT的數據變化,分為左對齊,右對齊,I2S及DSP共四種模式,其實就是四種數據傳輸時序,推薦使用左對齊模式或者I2S模式。

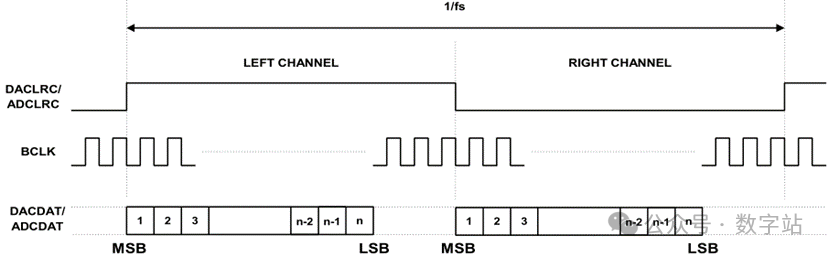

2.1左對齊模式

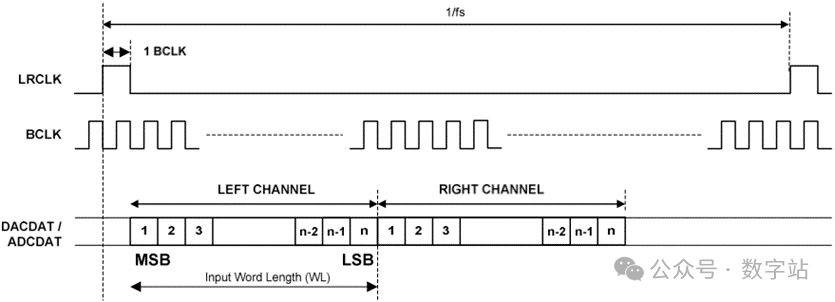

對應時序如下所示,ADCDAT在ADCLRC高電平時傳輸左聲道的數據,ADCDAT在ADCLRC低電平時傳輸右聲道數據,ADCDAT先傳輸高位數據。ADCLRC的頻率等于配置的ADC采樣頻率fs。

ADCDAT在BCLK的前n個時鐘的下降沿傳輸數據,n表示ADC采集數據的位寬。

圖3 左對齊模式

注意BCLK的頻率必須大于等于ADC采樣率乘以ADC數據位寬乘以2。當WM8371作為主機時,BCLK由WM8371提供,用戶不能設置其頻率。當WM8371作為從機時,BCLK由用戶提供,必須滿足頻率關系。

注意BCLK的下降沿與ADCLRC/DACLRC的跳變沿對齊,而DACDAT/ADCDAT的第一個數據(MSB)在BCLK下降沿開始傳輸,即DACDAT/ADCDAT與ADCLRC/DACLRC左邊對齊,因此被稱為左對齊模式。

在實測主機模式時發現BCLK的周期可能存在占空比不是百分之五十的情況,在設計時需要注意。

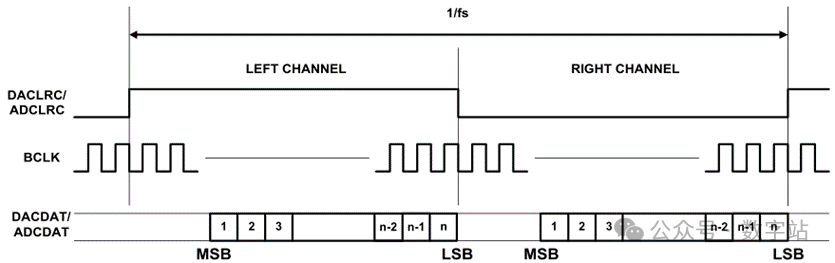

2.2右對齊模式

因為BCLK的頻率滿足大于等于ADCLRC/DACLRC頻率乘以ADC/DAC數據位寬乘以2即可,導致BCLK在ADCLRC/DACLRC高電平或低電平時的時鐘個數可能大于ADC/DAC數據位寬,就存在無效時鐘。

此時數據起始位與ADCLRC/DACLRC邊沿對齊,則是左對齊模式,如果數據的結束位置與ADCLRC/DACLRC邊沿對齊,則是右對齊模式,右對齊模式時序如下。

圖4 右對齊模式

DACDAT/ADCDAT依舊在BCLK下降沿先傳輸高位數據,LSB與ADCLRC/DACLRC邊沿對齊。

這種模式不好編寫適配多種采樣率的發送驅動,因為主機模式下不同采樣率時ADCLRC/DACLRC電平對應的BCLK個數不同,通用的驅動會比較麻煩,因此一般不推薦使用這類驅動時序。該模式不支持32位ADC和DAC數據位寬。

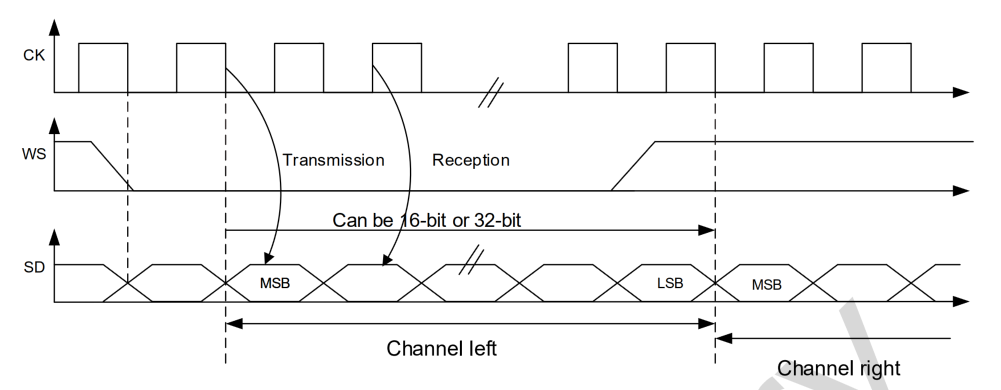

2.3I2S模式

I2S模式時序如下所示,與左對齊模式類似,但ADCDAT/DACDAT在ADCLRC/DACLRC邊沿后的第一個BCLK不傳輸數據,從BCLK的第二個下降沿傳輸最高位數據。

![]() 圖5 I2S模式

圖5 I2S模式

該模式使用起來也比較方便,推薦使用。

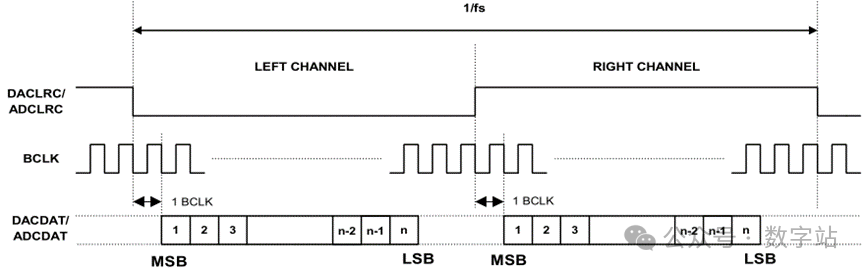

2.4DSP模式

DSP模式時序如下圖所示,每次傳輸數據LRCLK只持續一個BCLK周期,其余時間保持電平。

LRCLK的下降沿與BCLK的下降沿對齊,ADCDAT/DACDAT開始傳輸n位左聲道數據,然后傳輸n位右聲道數據,ADCDAT/DACDAT在剩余的BCLK周期無效。

![]() 圖6 DSP模式

圖6 DSP模式

四種模式下LRCLK和BCLK的頻率都是遵守相同規則的,且ADCDAT/DACDAT均在BCLK的下降沿傳輸數據,在BCLK上升沿期間數據保持不變。

03

WM8371的時序參數

WM8731的ADC和DAC的數據位寬始終為24位,但在I2S或左對齊模式下,數字音頻數據可編程為16位、20位、24或32位。即寄存器編程音頻數據位寬為16位時,ADCDAT會將ADC采集的高16位數據輸出,低8位數據舍棄。如果寄存器編程音頻數據位寬為32位時,ADCDAT會把ADC采集的24位數據作為高位,低八位補零,達到32位數據輸出。

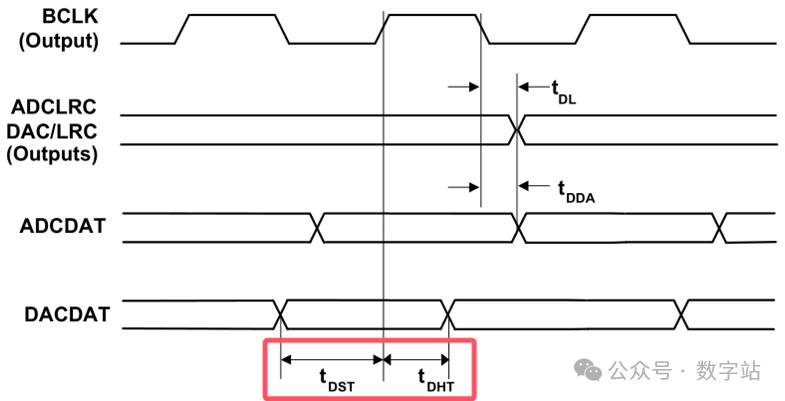

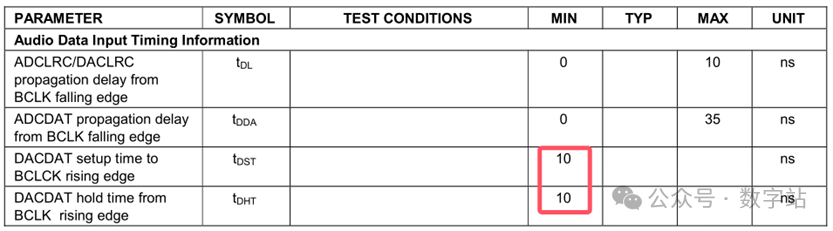

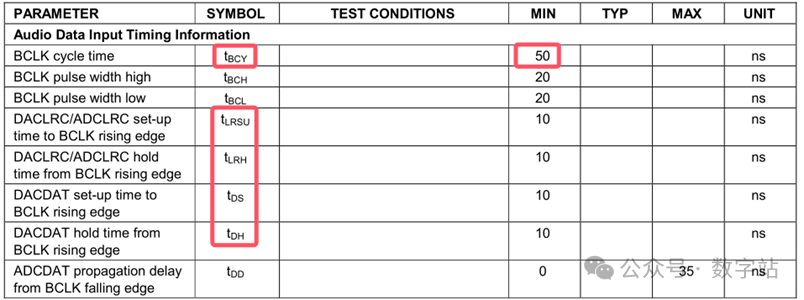

主機模式下的時序參數如下所示,需要重點關注下圖紅框中的兩個時序參數。

圖7 主機模式時序參數

兩個時序參數如下表所示,DACDAT必須在BCLK上升沿前后至少10ns內保持穩定。![]()

圖8 時序參數

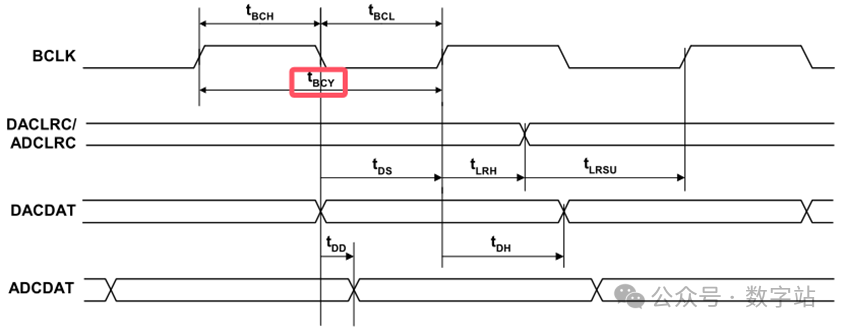

從機模式的時鐘信號和聲道指示信號都由主控芯片提供,相關的時序參數會多一些,如下圖所示。

圖9 從機模式時序參數

BCLK的最小周期為50ns,即接口數據傳輸的最大頻率為20MHz,另外DACLRC/ADCLRC和DACDAT在BCLK上升沿前后的10ns內必須保持不變,WM8731才能穩定采集對應信號的狀態。![]()

圖10 時序參數

本文主要講解I2S時序,文中圖片均來自WM8371芯片手冊

-

時序

+關注

關注

5文章

397瀏覽量

37867 -

I2S

+關注

關注

1文章

71瀏覽量

42744 -

wm8731

+關注

關注

0文章

2瀏覽量

3450

原文標題:詳解I2S時序

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

音頻總線I2S協議:I2S收發模塊FPGA的仿真設計

全面解析I2S、TDM、PCM音頻總線

aic3253的I2S完整的時序圖及接口協議如何設置?

音頻接口I2S實驗

基于FPGA和AD1836的I2S接口設計

幾種常見的I2S數據格式

基于MM32F5270控制器的I2S音頻播放

I2S、TDM、PCM音頻總線

雅特力AT32 MCU SPI/I2S入門指南

評論