本文編撰:KoenNoldus,流程與平臺架構師

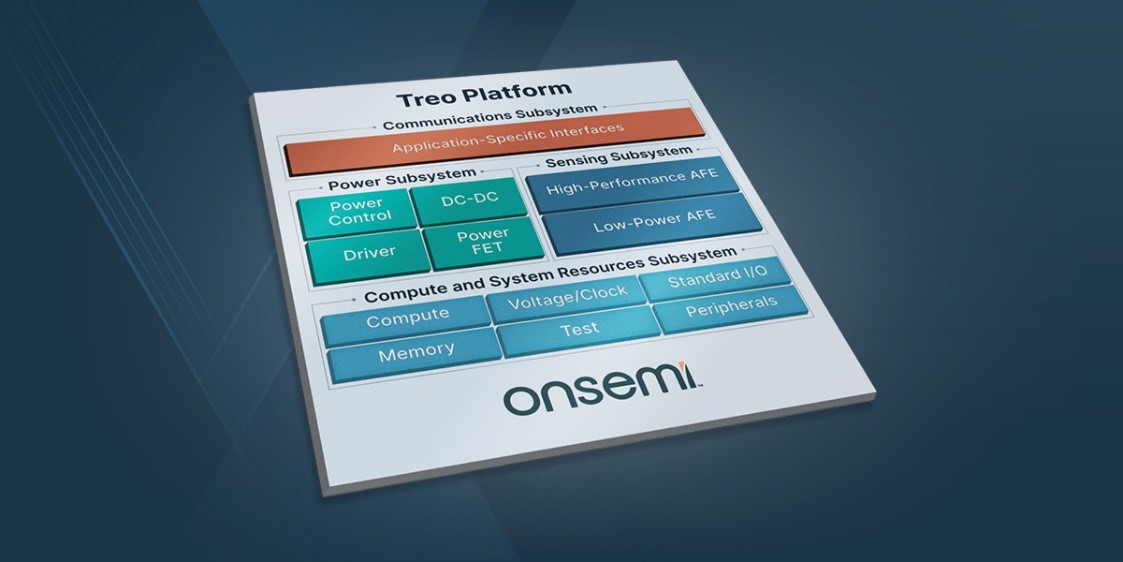

本文重點介紹了安森美(onsemi)Treo平臺的模擬性能。引入了PPA三角形概念來比較不同工藝技術之間的模擬關鍵指標。總體而言,本文將展示基于65nm BCD工藝技術的安森美 Treo平臺,在模擬、混合信號及高壓BCD解決方案領域具有強大的競爭力。

PPA 三角形

功耗、性能和面積(Power、Performance、Area,PPA)是表征晶圓工藝技術能力的三個關鍵指標:

性能指的是電路的帶寬或工作頻率。性能也可以指精度或分辨率,或者高壓器件的導通電阻。

面積是指集成電路占用的硅片面積。

采用特定工藝技術設計電路的競爭力體現在低功耗、高性能(或最小分辨率,以 mV/LSB 表示)和小硅片面積這幾個特征。在電路設計過程中,這三個變量構成了一個基本的權衡關系。例如,當性能提高時,可能會以增加功耗和晶粒尺寸為代價,或者當晶粒尺寸減小時,可能會導致性能降低。根據不同的電路,存在不同的權衡,從而導致不同的電路優化結果。

不同技術節點之間,其工藝技術的功耗、性能和面積特性及其最優組合也各不相同。在較小的工藝節點上設計的電路通常能夠實現更優的總體PPA得分,即在更小的面積和更低的功耗下實現更高的性能。

傳統上,PPA的評估指標由以下方程表示:

隨著性能的提高,面積和功耗的降低,PPA 的總得分也越高。

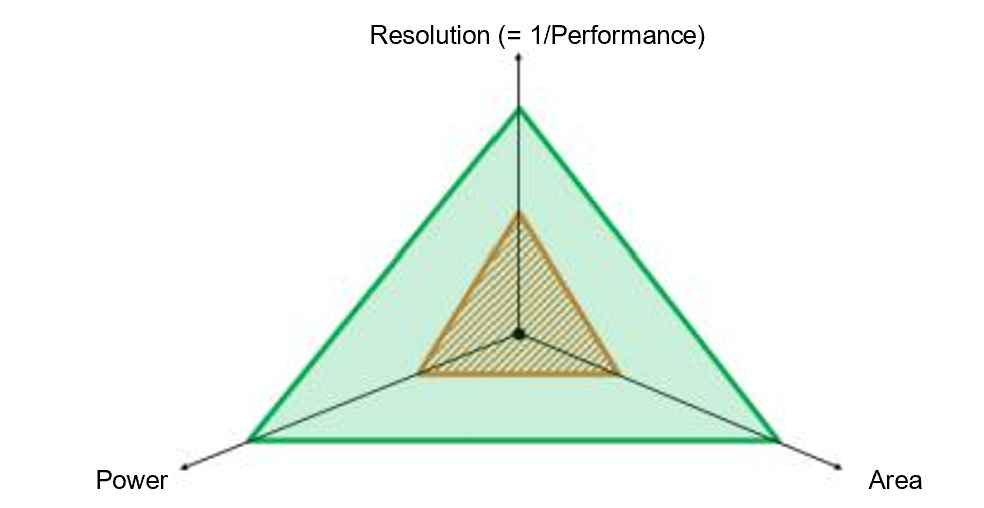

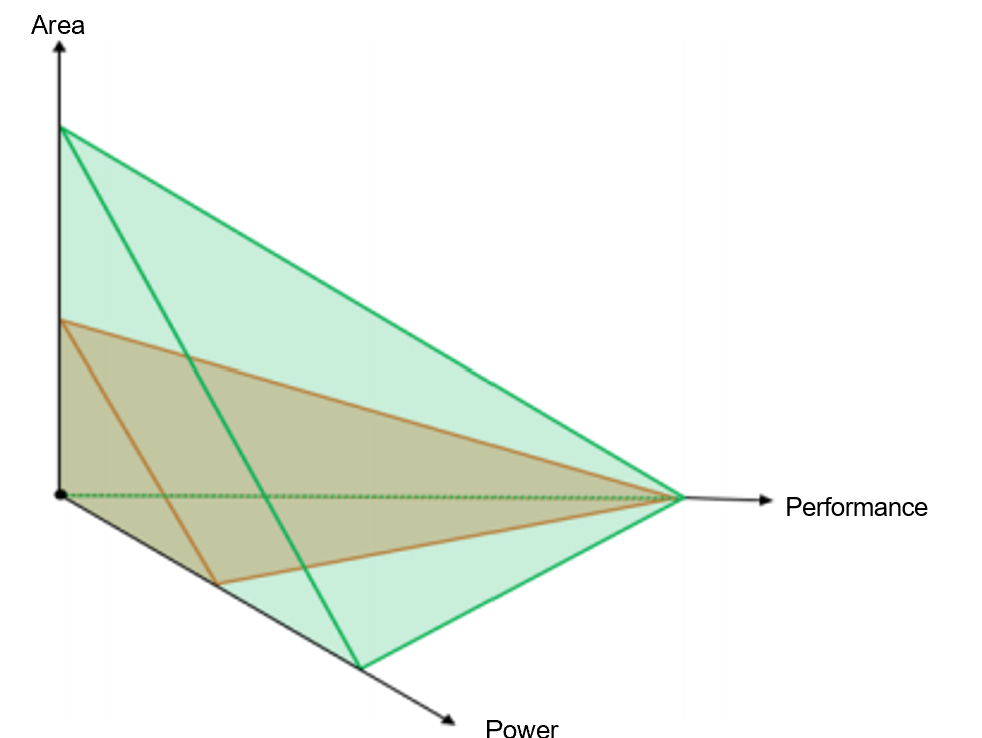

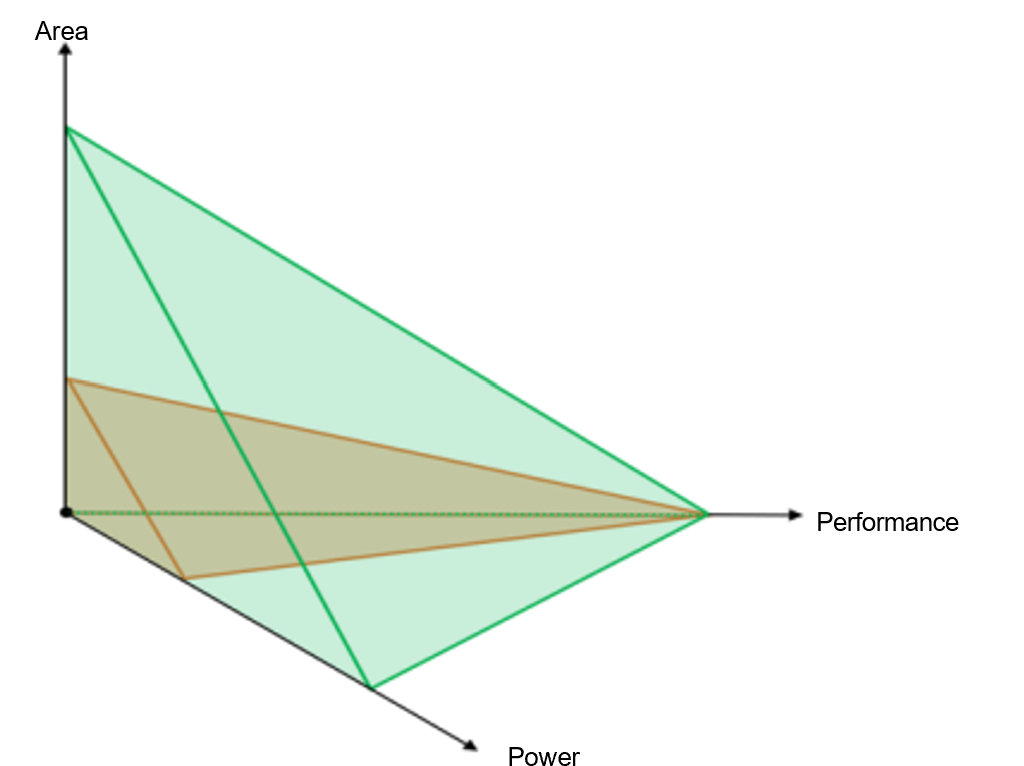

另一種以直觀方式表示各代技術之間相互的方法是三角形(2D)或金字塔(3D)。在圖 1 中,整體性能用 3 個坐標軸來表示。

圖1. PPA三角形作為工藝技術評估指標示意圖

一個軸代表分辨率,其中理想電路指盡可能高的分辨率(零分辨率對應于無限精確的系統)。第二個軸代表硅片面積,其中理想電路以無限小的面積提供相應功能。第三個軸代表功耗,其中理想電路以無限小的功耗實現相應功能。然而,在現實中,每個電路都需要一定的硅片面積和功耗,并且實現大于零的有限分辨率。

如圖 1 中的三維圖所示,由原點和 PPA 三角形定義的金字塔體積表示工藝技術的競爭力。在比較不同電路和技術節點之間的 PPA 時,PPA 三角形的頂點越靠近中心,電路的 PPA 分數就越高。終極工藝技術具有無限小的功耗、硅片面積和無限精確的分辨率。

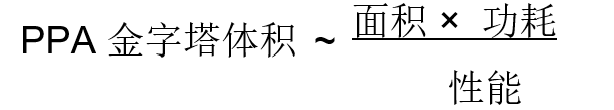

在這種表示方法中,整體性能由金字塔的體積決定:

金字塔圖是估算實現特定性能所需資源數量的直觀方法。

PPA作為BCD65的評估指標

本文采用 PPA 作為評估指標,對安森美 Treo 平臺,采用65 nm BCD 工藝技術(BCD65 - 2.5 V)和以前的工藝節點(180 nm - 3.3 V / 5 V)進行了比較。通過比較技術參數和特性,闡明了所選工藝技術對功耗、性能和面積的影響,并討論了 BCD65 相較于之前工藝節點的改進之處。已經使用BCD65設計或從180nm工藝遷移到65nm工藝的模擬IP,為PPA得分的提高提供了真實可靠的證據。本文還討論并比較了實際電路示例。

安森美Treo平臺還提供工作電壓范圍在5V - 90V的高壓器件。低Rsp(比導通電阻,單位為mΩ*mm2)的DMOS器件可以與65nm 低壓模擬和數字電路在同一晶粒上集成。這種結合了低、中、高壓能力的特點,在65nm BCD技術中是非常獨特的。

本文以 PPA 作為評價指標,表明從 180 nm - 3.3 V / 5 V 遷移到 65 nm - 2.5 V,模擬電路平均至少達到了5倍的整體改進。基于此,安森美在 BCD 應用領域處于領先地位,實現了功耗、性能和面積的完美結合。

以下各節將分別闡述這三項關鍵指標。

功耗

工藝改進包括柵極氧化層厚度的縮小。更薄的柵極氧化層需要更低的工作電壓。對于 BCD65,典型的模擬低壓電源為 2.5 V,而在較早的 BCD 技術節點(如 110 nm / 130 nm 或 160 nm / 180 nm)中通常使用 3.3 V 或 5 V。這種低壓電源意味著電路功耗可降低 25% 至 50%(電流消耗相同),這已經是提高 PPA 分數的一個重要因素。由于晶體管閾值電壓 (VTH) 通常也會降低,因此以前的電路拓撲結構不一定需要改變,一般仍可重復使用。

在65nm 節點上,模擬電路的電流消耗通常也較低,但性能卻相差無幾。在保持相同帶寬和增益的情況下,可以使用更低的偏置電流:相對寄生電容顯著減少,在更低的電流下可以獲得相同的跨導。這一點通過將IP從180nm –3.3V遷移到65nm –2.5V,并在相同性能水平上得到驗證。

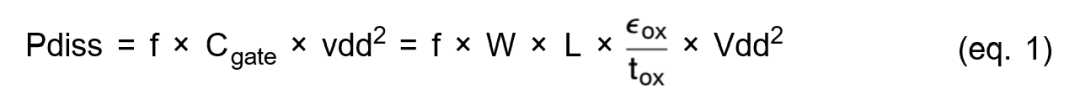

數字電路的標稱電壓為 2.5 V(厚柵極工藝)或 1.2 V(薄柵極工藝)。在 180 nm 節點上,標稱電壓分別為 3.3 V 和 1.8 V。下式表明,當 W、L、tox和 Vdd縮減時,數字功耗可以大大降低。(注意,調節tox具有相反的效果,但可通過調節尺寸和供電電壓得到補償)。特別是在 1.2 V 工藝流程中,Wmin和 Lmin顯著縮小。因此,工作頻率也有提高的空間。

硅片面積

從 180 nm 節點遷移到 65 nm 節點,每個功能(模擬、數字、高壓電源)的硅片面積都有顯著縮減。

對于模擬低壓電路,這一點通過將一組通用電路遷移到BCD65(厚柵極氧化層工藝)并保持相似性能來證明。為了使比較有效,使用了相同數量的金屬層和相同的標準器件集。結果是采用BCD65的模擬低壓電路的面積減少了大約50%。

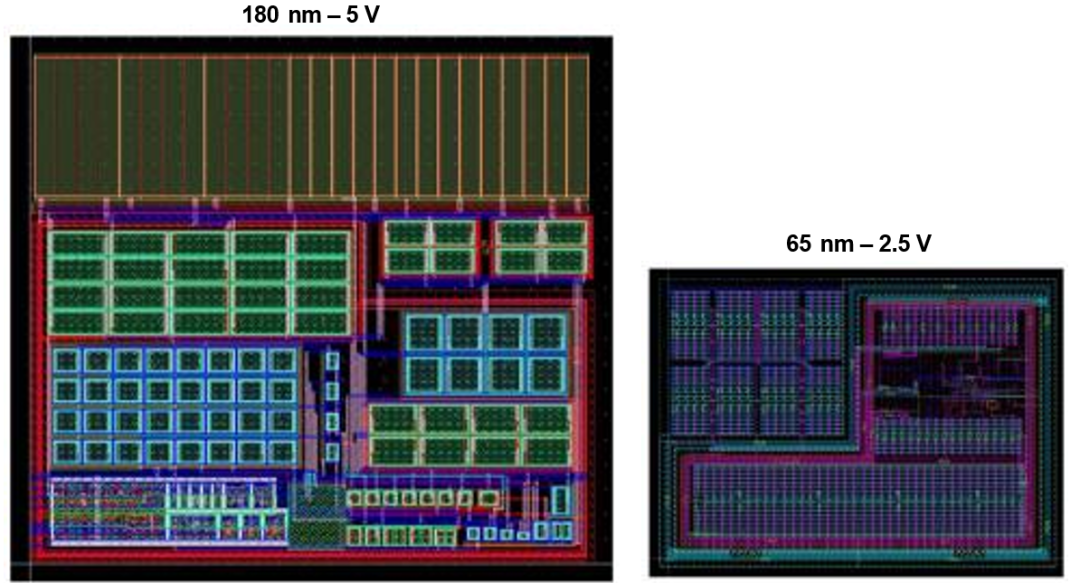

圖2展示了180nm-3.3V與BCD65-2.5V比較器電路之間存在45%的尺寸差距。

圖 2. 不同工藝節點間比較器電路的布局尺寸變化

這種在相似精度下的模擬(及混合信號)低壓電路尺寸縮小不僅能降低晶粒成本,還允許在一個更小的封裝尺寸中集成更多功能。之所以能實現這些模擬和混合信號電路尺寸縮小,主要得益于以下因素:

在半導體工藝中,較小的工藝節點通常能改善晶體管閾值電壓(Vth)的匹配。因此,與工藝相關的失配系數會降低。根據Pelgrom定律,在失配程度相同的情況下,匹配晶體管的柵極面積會減小。對 180 nm - 5 V 工藝和 65 nm BCD - 2.5 V 工藝的閾值電壓失配系數進行比較后發現,匹配晶體管結構的柵極面積至少縮小了兩倍。而在180 nm -3.3V與65 nm-2.5 V之間,改善程度較為有限。

BCD65標準多晶硅電阻相比于安森美采用180 nm BCD技術的標準多晶硅電阻和高電阻多晶硅電阻,具有更低的失配系數。加之單元間的間距更小,匹配電阻陣列的面積減少了超過40%。

與安森美的180 nm BCD技術相比,Poly-Nwell電容在相同絕對值下具有更小的面積。這是由于BCD65技術(厚柵極工藝)中,柵極氧化層電容密度與氧化層厚度成反比,其電容密度高出30%。

除了多晶硅面積縮小之外,BCD65設計規則允許器件之間的間距更小,從而進一步提高了器件密度。晶體管的源極、漏極和柵極連接所占用的面積更小,觸點面積幾乎縮小了6倍。

雙極型晶體管體積更小,并且表現出優異的匹配性。

BCD65 可顯著減少器件互連和信號布線所占面積。后端設計規則允許更小的間距(更小的金屬線寬和間距)以及更小(近 7 倍)的過孔。這并不一定會導致互連阻抗的增加:BCD65的金屬層采用的是銅鑲嵌工藝,其電阻比鋁低35%。布線距離通常更短。

BCD65 提供了一種錐形金屬化結構,使得在較低的金屬層中可以實現窄且高密度的互連線路,而在較高的金屬層中則逐漸變寬變厚,以支持大電流能力、電源布線和功率傳輸。此外,布線密度僅受限于在較高電壓下某些線間間距規則。

與 180 nm - 5 V 技術相比,另一個顯著的區別是器件隔離(BCD65 低壓電路采用結隔離)所占用的面積。

數字庫提供了更小的數字標準單元,從而實現了數字電路尺寸的顯著縮小。這使得數字柵極密度提高了 3 倍(與厚柵極氧化層工藝相比)和 6 倍(與薄柵極氧化層工藝相比)。在集成電路中可以輕松添加更多的數字功能。

靜電放電(ESD)保護只會輕微的減少尺寸,因為其尺寸主要由所需承受的能量決定。

在 BCD65 中,高壓器件的 Rsp 值顯著提高。與安森美之前的 BCD 技術相比,45 V DMOS 器件的 Rsp 值提高了 40%。

所有這些因素的結合,就會在產品層面產生顯著尺寸縮小。這一點通過將產品從180 nm BCD節點遷移到安森美的Treo平臺上的65 nm BCD節點得到了證明。

性能

前幾節詳細介紹了 BCD65 在電路性能與安森美之前的 180 nm BCD 節點類似的情況下,降低功耗和減少硅片面積的情況。反之亦然,在相同的功耗和面積下,基于安森美Treo 平臺開發的電路在精度和帶寬方面表現更佳。

更匹配的晶體管、電阻和雙極型晶體管可轉化為更高的精度。對于相同的電流消耗,電路可以在更高的增益帶寬乘積下工作。錐形金屬化結構在最低層的銅金屬層上采用窄跡線,并結合更短的布線距離,減少了互連寄生效應,這對高帶寬電路同樣有益。

由于寄生耦合和串擾噪聲較低,金屬疊層下部的低 K(低介電常數)材料可實現高速運行。無論如何,低 K 材料都是持續改進工藝技術和高速運行所必需的。等式 1 中已經顯示了提高數字電路時鐘速度的潛力,這有助于性能的提升。

通過在1.2V薄柵極工藝流程中使用BCD65雙柵極選項進行模擬設計,可以獲得另一個重要的帶寬提升。在薄柵極工藝流程中,晶體管的匹配度再次得到改善。1.2 V 下的模擬設計對于直接連接數字信號的模塊(如 A/D 和 D/A 轉換器或比較器)尤為重要。在更高頻率下運行可使模數轉換器 (ADC) 以更高的采樣率進行時鐘運算,從而實現多輸入通道的多路復用或達到更高的過采樣率 (OSR),從而獲得更高的分辨率。

在相同的硅片面積內集成了更多功能和更先進的電路。數字電路尺寸顯著縮小,可輕松增加包括MCU在內的數字功能。數字功能可用于增強模擬電路性能,并對模擬電路不完善之處進行修正。

BCD65中的PPA得分整體提升

前文解釋了為什么 Treo平臺 65 nm BCD技術在功耗、性能和面積方面優于 180 nm - 3.3 V / 5 V 技術。列舉了許多關于不同影響因素的定性說明。本節將根據實際電路示例說明 PPA 的具體改進。

示例 1

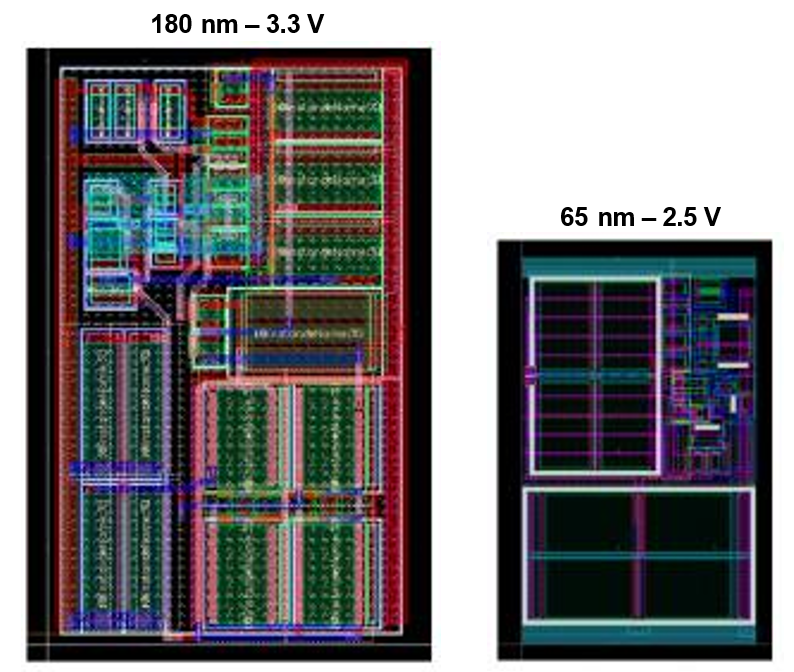

此運算放大器的設計已從安森美的 180 nm - 3.3 V BCD 技術遷移到 BCD65技術。該拓撲結構是一種廣泛使用的兩級放大器,稱為米勒運算放大器。遷移后的電路在偏移、帶寬、相對輸入共模范圍等方面具有相同性能。實際制造后的電路特性分析表明,與采用3.3 V 電壓供電的原電路相比,遷移后的電路電流消耗減少了40%(采用2.5 V 電壓供電)。原始設計和遷移后設計的布局如圖 3 所示(兩個電路布局的比例相同)。

圖 3. 運算放大器的布局比較

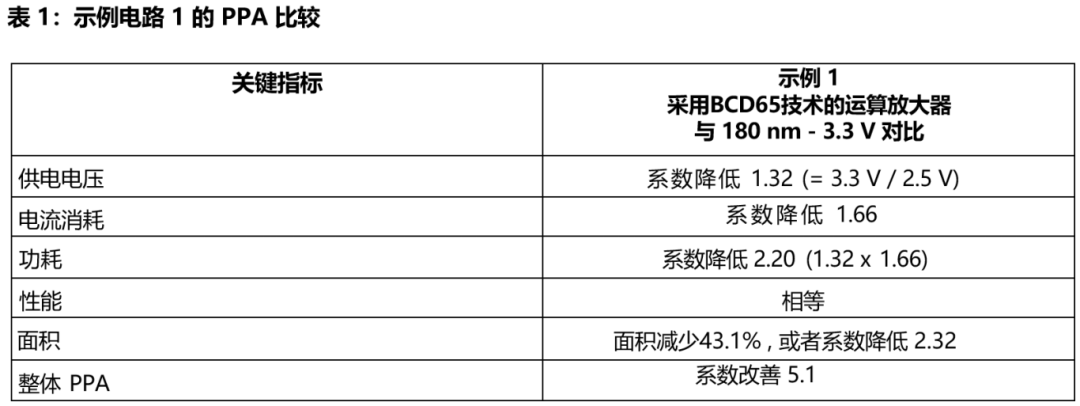

下表匯總了關鍵指標和整體PPA的比較:

對于這個運算放大器設計,采用 65 nm工藝技術可將整體 PPA 得分提高 5.1倍 。圖 4 所示電路的 PPA 三角形是顯示改進的另一種方法。綠色部分代表 180 nm - 3.3 V 設計,橙色部分代表 BCD65 設計,其性能相同,但功耗和硅片面積得到改善。

圖 4. 運算放大器的 PPA 三角形

180 nm- 3.3 V(綠色)和 65 nm- 2.5 V(橙色)

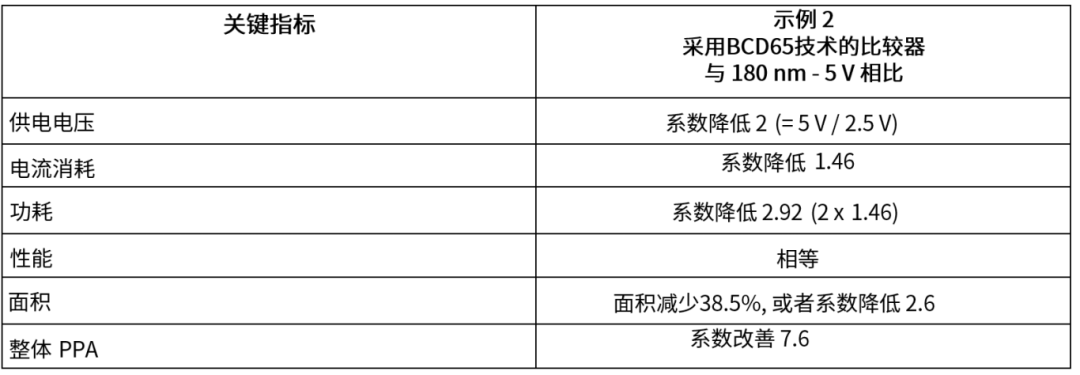

示例 2

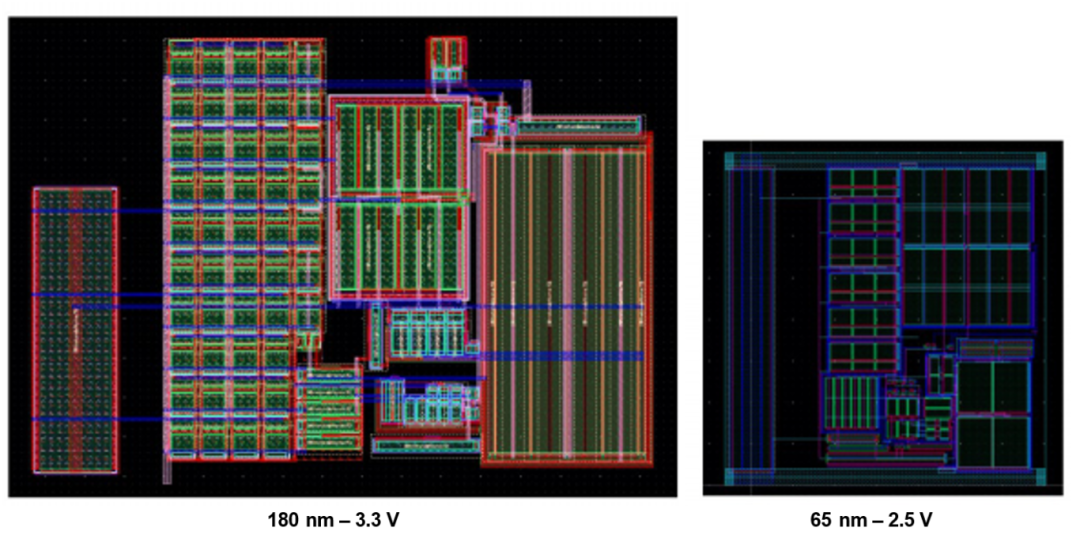

比較器設計已從安森美的 180 nm - 5 V BCD 技術遷移到 BCD65技術,在偏移、傳輸延遲和相對輸入共模范圍方面具有相同的性能。實際制造后的電路特性分析表明,與采用5V 電壓供電的原電路相比,遷移后的電路電流消耗減少了31%(采用2.5 V 電壓供電)。兩種版本的布局面積如圖 5 所示(兩種電路布局的比例相同)。

圖 5. 180 nm和 65 nm比較器電路布局圖

表 2:示例電路 2 的 PPA 比較

對于該比較器電路,改用 BCD65 可將整體 PPA 得分提高 7.6 倍。圖 6 所示電路的 PPA 三角形是顯示改進的另一種方法。同樣,綠色部分代表 180 nm - 5 V 設計,橙色部分代表 BCD65 設計,性能相同,但功耗和硅片面積得到改善。

圖 6. 比較器電路設計的 PPA 三角形

180 nm- 5 V(綠色)和 65 nm- 2.5 V(橙色)

根據電路類型的不同,可達到的整體 PPA 改進得分也不同。一些設計比其他設計更難縮小尺寸,或者一些設計僅在硅片面積或電流消耗方面顯示出有限的優化。但平均而言,從 180 nm - 3.3 V 遷移到 BCD65技術,整體 PPA 得分可提高 5 倍以上。從 180 nm - 5 V 升級到 BCD65 時,改進幅度更大,因為降低更多的供電電壓帶來了更多的好處。

結語

本文描述了三個關鍵指標——功耗、性能和面積,它們之間存在的權衡關系,以及如何使用PPA作為衡量標準來比較不同工藝技術下的模擬性能。以PPA作為評價指標,顯示了從180 nm-3.3V /5 V BCD技術遷移到安森美 Treo平臺,至少實現了平均5倍的整體改進。加上高壓器件,密集的模擬低壓和數字電路,使得安森美Treo平臺在BCD應用中具有強大的競爭力。

安森美Treo平臺在PPA方面的改進不僅限于理論層面,還得到了已經完成遷移及制造的模擬IP實踐驗證。工藝的改進允許更高的集成密度,在更小的尺寸內能夠集成更多功能,這對于現代高性能模擬和BCD應用至關重要。

總體而言,通過向市場推出性能卓越、功耗更低、硅片面積更小的產品,安森美 Treo 平臺使安森美在模擬、混合信號和高壓解決方案領域處于領先地位,成為先進模擬電路設計極具競爭力的選擇。

-

集成電路

+關注

關注

5415文章

11848瀏覽量

366007 -

安森美

+關注

關注

32文章

1752瀏覽量

92639 -

混合信號

+關注

關注

0文章

492瀏覽量

65203 -

晶圓

+關注

關注

52文章

5072瀏覽量

128958

原文標題:從功耗、硅片面積、性能三大維度評估Treo平臺

文章出處:【微信號:onsemi-china,微信公眾號:安森美】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

安森美推出業界領先的模擬和混合信號平臺

安森美為客戶提供真正益處的交易

安森美半導體和Q Tech的攝像機參考設計

安森美半導體宣布收購Fairchild半導體

安森美新一代車載方案技術

安森美功放管解讀 安森美功放管怎么樣 安森美功放管優缺點

安森美公司介紹與安森美官網鏈接分享

安森美推出基于BCD工藝技術的Treo平臺

安森美推出Treo平臺,賦能高效電源與感知解決方案

安森美亮相2024德國慕尼黑電子展

安森美推出創新Treo平臺,BCD技術+模塊化IP讓工程師更易上手

深度解析安森美Treo平臺

深度解析安森美Treo平臺

評論