Silabs公司的Si54x系列是采用第四代DSPLL技術(shù)的超低抖動(dòng)高性能晶體振蕩器,頻率范圍從0.2-1500MHz,分辨率小于1ppb,具有極好的PSRR,電源抗噪度-80dBc,穩(wěn)定度3倍于SAW振蕩器,工作電壓3.3V,2.5V和1.8V,輸出格式包括LVPECL, LVDS, CML, HCSL, CMOS和雙CMOS輸出,主要用在100G/200G/400G OTN,相干光學(xué),10G/40G/100G光學(xué)以太網(wǎng),3G-SDI/12G-SDI/24G-SDI廣播視頻,數(shù)據(jù)中心,測(cè)量和測(cè)試,時(shí)鐘和數(shù)據(jù)恢復(fù),FPGA/ASIC時(shí)鐘。本文介紹了Si54x系列主要特性,功能框圖,通用振蕩器評(píng)估板Si5xxUC-EVB主要特性,框圖和電路圖。

The Si545 Ultra Series? oscillator utilizes Silicon Laboratories’advanced 4th generation DSPLL? technology to provide an ultra-low jitter, low phase noise clock at anyoutput frequency. The device is factory-programmed to any frequency from 0.2 to1500 MHz with 《1 ppb resolution and maintains exceptionally low jitter for both integerand fractional frequencies across its operating range. The Si545 offers excellentreliability and frequency stability as well as guaranteed aging performance. On-chippower supply filtering provides industry-leading power supply noise rejection,simplifyingthe task of generating low jitter clocks in noisy systems that use switched-modepower supplies. Offered in industry-standard 3.2x5 mm and 5x7 mm footprints, theSi545 has a dramatically simplified supply chain that enables Silicon Labs to ship customfrequency samples 1-2 weeks after receipt of order. Unlike a traditional XO,where a different crystal is required for each output frequency, the Si545 uses onesimple crystal and a DSPLL IC-based approach to provide the desired output frequency.

This process also guarantees 100% electrical testing of every device. The Si545 isfactory-configurable for a wide variety of user specifications, including frequency, output format, and OE pin location/polarity. Specific configurations are factory-programmedat time of shipment, eliminating the long lead times associated with custom oscillators.

Si54x系列主要特性:

? Available with any frequency from 0.2MHz to 1500 MHz

? Ultra low jitter: 80 fs Typ RMS(12 kHz–20 MHz)

? Excellent PSRR and supply noiseimmunity:–80 dBcTyp

? 3x tighter stability than SAW oscillators

? 3.3 V, 2.5 V and 1.8 V VDD supplyoperation from the same part number

? LVPECL, LVDS, CML, HCSL, CMOS,and Dual CMOS output options

? 3.2×5, 5x7 mm package footprints

? Samples available with 1-2 week leadTimes

Si54x系列應(yīng)用:

? 100G/200G/400G OTN, coherent optics

? 10G/40G/100G optical ethernet

? 3G-SDI/12G-SDI/24G-SDI broadcastvideo

? Datacenter

? Test and measurement

? Clock and data recovery

? FPGA/ASIC clocking

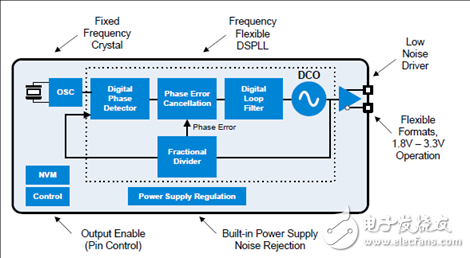

圖1.Si54x系列框圖

通用振蕩器評(píng)估板Si5xxUC-EVB

This document describes operation of the Silicon Laboratories Si5xxUC-EVB evaluation board designed to evaluate any of Silicon Labs’ pin-controlled or I2C configurable Si5xx XOs or VCXOs. Three device sites are available to support one of either 5mm x 7mm, 3.2mm x 5mm, or 2.5mm x 3.2mm devices in either 4, 6, or 8 pin configurations. Selector switches make it easy to configure device control pins (pins 1, 2, 7, or 8) for properoperation without the use of jumpers. Similarly, XO device VDD voltage (3.3V, 2.5V,1.8V) can be selected via switches based on either external +5V (for stand-alone operation)or micro USB sourced +5V USB operation. The EVB also features flexible outputtermination circuits and PCB layout optimized for superior signal integrity.

通用振蕩器評(píng)估板Si5xxUC-EVB主要特性:

? Evaluation of any Silicon Labs XO orVCXO (Si51x, Si53x, Si54x, Si55x, Si57x,Si59x)

? AC coupled differential/single-ended outputclocks.

? Voltage control (Vc) port for VCXOevalution.

? Switch selectable settings. No jumpers.

? External power or USB powered.

? Use stand-alone or with our ProgrammableOscillator Calculator SW tool

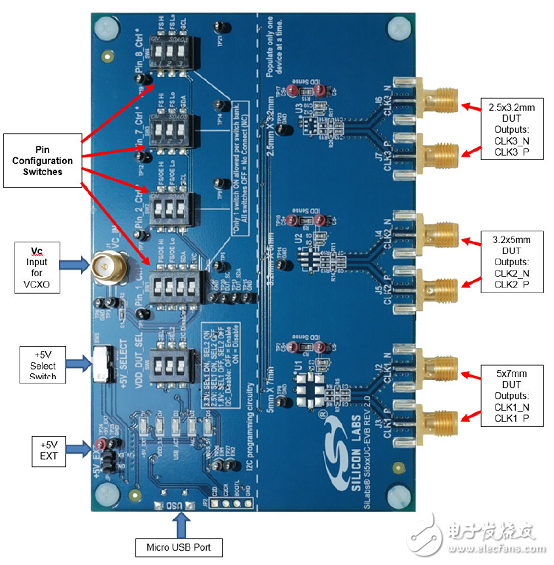

圖2.通用振蕩器評(píng)估板Si5xxUC-EVB外形圖

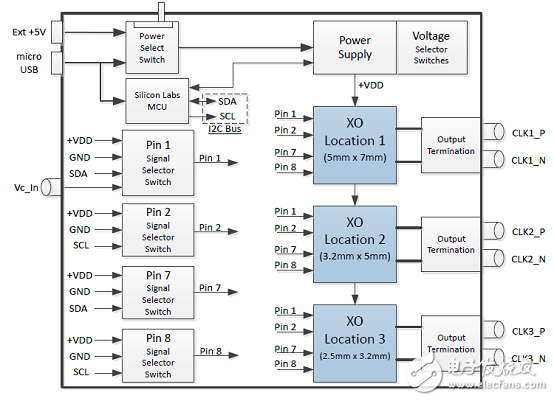

圖3.通用振蕩器評(píng)估板Si5xxUC-EVB框圖

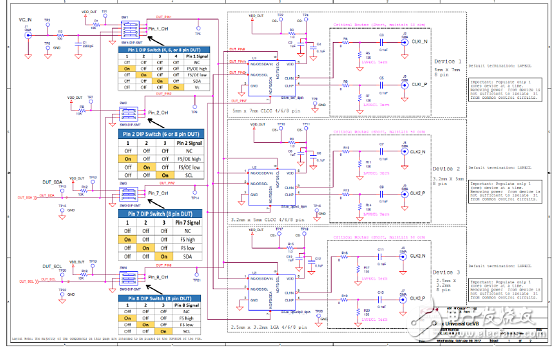

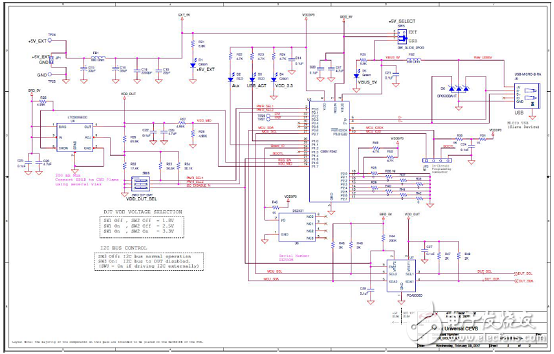

圖4.通用振蕩器評(píng)估板Si5xxUC-EVB電路圖(1)

圖5.通用振蕩器評(píng)估板Si5xxUC-EVB電路圖(2)

-

Silabs

+關(guān)注

關(guān)注

0文章

5瀏覽量

14395 -

晶體振蕩器

+關(guān)注

關(guān)注

9文章

617瀏覽量

29106

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Silicon Labs發(fā)布時(shí)鐘行業(yè)超小尺寸、超低抖動(dòng)的 I2C可編程晶體振蕩器

Blackfin ADSP-BF70x系列DSP處理器,業(yè)界性能領(lǐng)先的超低功耗DSP解決方案

silabs無(wú)線收發(fā)器SI446x的應(yīng)用技巧是什么?

Silicon Labs發(fā)布業(yè)界最低抖動(dòng)任意頻率輸出晶體振蕩器

Silicon Labs發(fā)布滿足高速收發(fā)器需求的新一代高性能振蕩器Si54x

Silicon Labs不斷擴(kuò)大在高性能時(shí)鐘解決方案領(lǐng)域的領(lǐng)先地位

SiTime硅晶振工業(yè)機(jī)器人解決方案

晶振具有超低抖動(dòng)、頻率靈活性

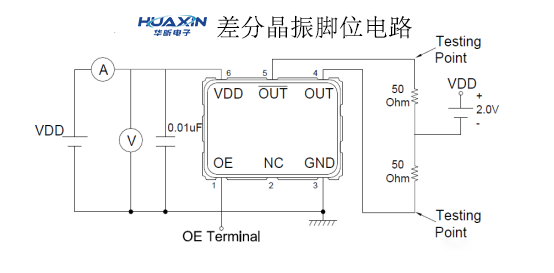

華昕差分晶振:高性能、低功耗、低相位噪聲

晶振的抖動(dòng)會(huì)帶來(lái)哪些影響

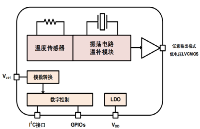

兼容SiTime,國(guó)產(chǎn)高性能晶振/溫補(bǔ)晶振交換機(jī)應(yīng)用方案

Silabs Si54x系列超低抖動(dòng)高性能晶振解決方案詳解

Silabs Si54x系列超低抖動(dòng)高性能晶振解決方案詳解

評(píng)論