氮化硅(Si?N?)薄膜是一種高性能介質(zhì)材料,在集成電路制造領(lǐng)域具有廣泛的應(yīng)用前景。作為非晶態(tài)絕緣體,氮化硅薄膜不僅介電特性優(yōu)于傳統(tǒng)的二氧化硅,還具備對(duì)可移動(dòng)離子的強(qiáng)阻擋能力、結(jié)構(gòu)致密、針孔密度小、化學(xué)穩(wěn)定性好以及介電常數(shù)高等一系列優(yōu)點(diǎn)。本文將主要介紹了氮化硅薄膜的制備方法、特性及其在半導(dǎo)體器件制造中的具體應(yīng)用,重點(diǎn)對(duì)比低壓化學(xué)氣相沉積(LPCVD)和等離子體增強(qiáng)化學(xué)氣相沉積(PECVD)兩種制備工藝,并詳細(xì)解析低應(yīng)力PECVD氮化硅薄膜的制備技術(shù)。

一、氮化硅薄膜的制備方法及用途

1. 氮化硅薄膜的制備方法

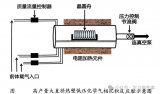

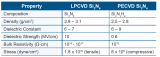

氮化硅薄膜的制備方法主要包括LPCVD和PECVD兩種。

LPCVD氮化硅工藝

LPCVD工藝需要高溫環(huán)境,通常在700~800°C范圍內(nèi)進(jìn)行。這種工藝制備的氮化硅薄膜結(jié)構(gòu)致密,具有較高的耐腐蝕性和硬度,掩膜性能優(yōu)異,適用于堿性溶液刻蝕硅材料的掩膜層。

PECVD氮化硅工藝

與LPCVD相比,PECVD工藝可以在較低的溫度下(低于400°C)沉積氮化硅薄膜。這使得PECVD工藝在與底層器件結(jié)構(gòu)兼容的工作溫度下沉積氮化硅薄膜成為可能。PECVD制備的氮化硅薄膜雖然相對(duì)不如LPCVD薄膜致密,但具有更高的靈活性和更低的制備成本。

2. 氮化硅薄膜的用途

氮化硅薄膜在半導(dǎo)體器件制造中有兩個(gè)主要用途:掩蔽膜和鈍化層。

掩蔽膜

掩蔽膜通常使用LPCVD沉積,因?yàn)長PCVD制備的氮化硅薄膜具有優(yōu)異的阻水性能。氮化硅掩蔽特別適用于熱氧化過程,因?yàn)檠鯕夂茈y通過氮化硅擴(kuò)散。

鈍化層

作為鈍化層,氮化硅薄膜具有許多理想的品質(zhì)。PECVD方法允許其在與底層器件結(jié)構(gòu)兼容的工作溫度下沉積。該薄膜幾乎不受水分和鈉離子等關(guān)鍵環(huán)境污染物的影響。通過調(diào)整PECVD工藝條件,還可以調(diào)整薄膜中的固有應(yīng)力,以消除薄膜分層或開裂的風(fēng)險(xiǎn)。

二、低應(yīng)力PECVD氮化硅薄膜制備

在半導(dǎo)體工藝中,較低的薄膜應(yīng)力是保證器件形變較小的關(guān)鍵因素。PECVD制備氮化硅薄膜時(shí),薄膜應(yīng)力主要來源于兩個(gè)方面:熱應(yīng)力和微結(jié)構(gòu)應(yīng)力。

1. 熱應(yīng)力

熱應(yīng)力是由于薄膜和襯底之間不同的熱膨脹系數(shù)所導(dǎo)致的。在高溫條件下淀積的薄膜當(dāng)降低到室溫時(shí),相對(duì)于襯底會(huì)產(chǎn)生一定的收縮或膨脹,表現(xiàn)出張應(yīng)力或壓應(yīng)力。

2. 微結(jié)構(gòu)應(yīng)力

微結(jié)構(gòu)應(yīng)力主要來源于薄膜和襯底接觸層的錯(cuò)位,或薄膜內(nèi)部的一些晶格失配等缺陷和薄膜固有的分子排列結(jié)構(gòu)。在PECVD系統(tǒng)中,由于淀積溫度較低(通常不超過400℃),并且使用射頻放電產(chǎn)生等離子體來維持反應(yīng),因此射頻條件(頻率和功率)成為影響氮化硅薄膜應(yīng)力的關(guān)鍵因素之一。

3. 射頻條件對(duì)薄膜應(yīng)力的影響

頻率

在低頻(380kHz)條件下,反應(yīng)氣體的離化率較高,等離子體密度較大,容易減少氫元素的摻入,使薄膜變得致密,產(chǎn)生較大的壓應(yīng)力。而在高頻(13.56MHz)條件下,反應(yīng)氣體的離化程度較低,等離子體密度較小,引入較多的氫元素,形成較為疏松的結(jié)構(gòu),導(dǎo)致薄膜呈現(xiàn)張應(yīng)力。

功率

射頻功率對(duì)薄膜應(yīng)力的影響同樣顯著。當(dāng)射頻功率較小時(shí),反應(yīng)氣體尚不能充分電離,激活效率低,薄膜針孔多且均勻性較差。隨著射頻功率的增大,氣體激活效率提高,反應(yīng)物濃度增大,等離子體氣體對(duì)襯底有一定的轟擊作用,使生長的氮化硅薄膜結(jié)構(gòu)致密,提高了膜的抗腐蝕性能。但射頻功率不能過大,否則沉積速率過快,會(huì)出現(xiàn)類似“濺射”現(xiàn)象,影響薄膜性質(zhì)。低頻條件下氮化硅薄膜應(yīng)力為壓應(yīng)力,高頻條件下為張應(yīng)力,其大小均隨功率的增大而減小。

4. 混頻工藝

為了減小氮化硅薄膜的應(yīng)力,并實(shí)現(xiàn)對(duì)應(yīng)力大小甚至方向的控制,可以采用混頻工藝。混頻工藝結(jié)合了低頻和高頻氮化硅薄膜的特性,通過適當(dāng)選取低頻和高頻反應(yīng)時(shí)間周期,可以實(shí)現(xiàn)對(duì)薄膜應(yīng)力的調(diào)控。然而,混頻工藝中低頻和高頻反應(yīng)時(shí)間周期的選取需要折中考慮。切換時(shí)間周期過短會(huì)導(dǎo)致等離子體不穩(wěn)定,影響薄膜的均勻性;切換時(shí)間周期過長則會(huì)影響氮化硅薄膜厚度方向上的均勻性。因此,在進(jìn)行工藝調(diào)整時(shí),需要綜合考慮以上兩方面因素。

通過對(duì)比LPCVD和PECVD兩種制備工藝,我們可以發(fā)現(xiàn),LPCVD制備的氮化硅薄膜具有更加致密的薄膜特性、更耐腐蝕和硬度更好等優(yōu)點(diǎn),適用于堿性溶液刻蝕硅材料的掩膜層;而PECVD制備的氮化硅薄膜則具有更低的沉積溫度和更高的靈活性,適用于與底層器件結(jié)構(gòu)兼容的鈍化層。此外,通過調(diào)整PECVD工藝條件,還可以實(shí)現(xiàn)對(duì)薄膜應(yīng)力的調(diào)控,以滿足不同半導(dǎo)體器件的需求。

-

薄膜

+關(guān)注

關(guān)注

0文章

305瀏覽量

29951 -

PECVD

+關(guān)注

關(guān)注

2文章

22瀏覽量

10162 -

氮化硅

+關(guān)注

關(guān)注

0文章

77瀏覽量

374

原文標(biāo)題:【半導(dǎo)體材料】最全!氮化硅薄膜的特性及制備方法

文章出處:【微信號(hào):深圳市賽姆烯金科技有限公司,微信公眾號(hào):深圳市賽姆烯金科技有限公司】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

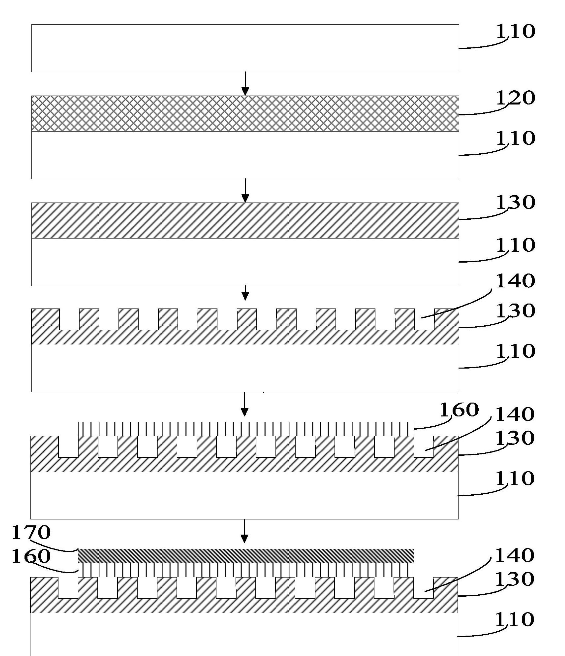

單晶圓系統(tǒng):多晶硅與氮化硅的沉積

納微半導(dǎo)體氮化鎵和碳化硅技術(shù)進(jìn)入戴爾供應(yīng)鏈

LPCVD氮化硅薄膜生長的機(jī)理

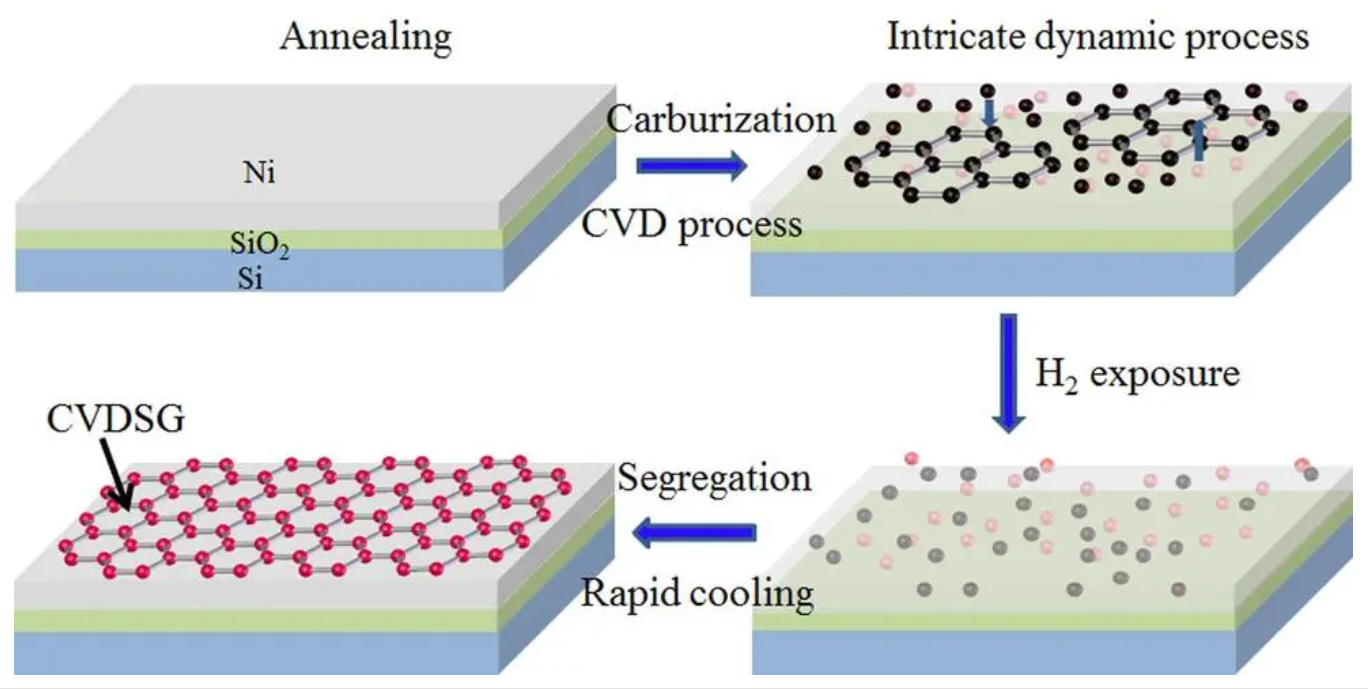

碳化硅薄膜沉積技術(shù)介紹

碳化硅材料的特性和優(yōu)勢(shì)

?石墨烯的基本特性?,制備方法?和應(yīng)用領(lǐng)域

透射電鏡(TEM)樣品制備方法

淺談薄膜沉積

碳化硅 (SiC) 與氮化鎵 (GaN)應(yīng)用 | 氮化硼高導(dǎo)熱絕緣片

碳化硅與氮化鎵哪種材料更好

ATA-7010高壓放大器在納米薄膜制備中的作用有哪些

大連理工大學(xué)發(fā)布氮化鎵氣體傳感器專利

氮化硅薄膜的特性及制備方法

氮化硅薄膜的特性及制備方法

評(píng)論