一、前言

芯片間的數據傳輸根據同一時間傳輸的bit數分為串行傳輸和并行傳輸。

串行傳輸:每次傳輸1bit數據,該方式具有傳輸距離長,傳輸可靠,但延遲高,數據帶寬低。

并行傳輸:每次可傳輸多bit數據,具有傳輸效率高,但傳輸距離短,因同時多路傳輸相互之間存在干擾導致信號容易失真。

二、芯片間數據傳輸技術發展

芯片間數據傳輸時,要保證數據準確被接收端接收,需要考慮時鐘信號在準確的時刻采集數據信號,因為需要考慮時鐘信號與數據信號的同步。

2.1 時鐘/數據同步方式

根據時鐘信號與數據信號的同步方式分為系統同步,源同步,自同步

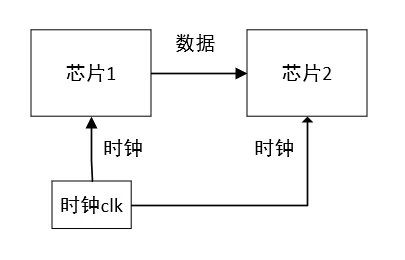

系統同步:發送端和接收端的時鐘來自同一個外部時鐘,簡單原理圖如下

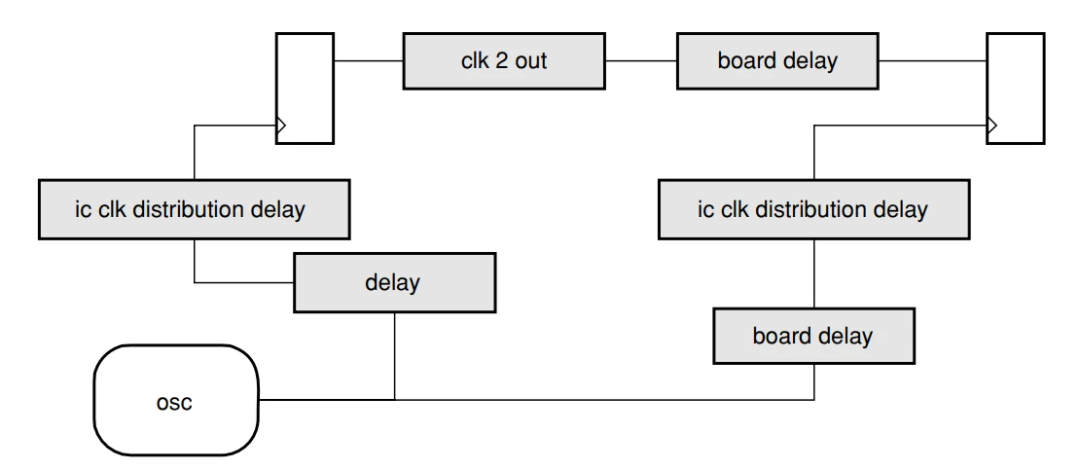

對應的詳細時間模型如下圖,下圖中灰色背景的都是實際需要考慮的,可見需要考慮不少相關單元的延時。

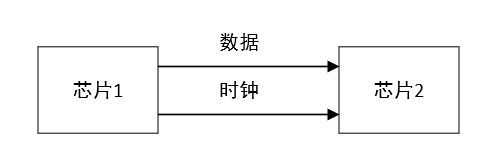

源同步:接收端的時鐘和數據都來自發送端

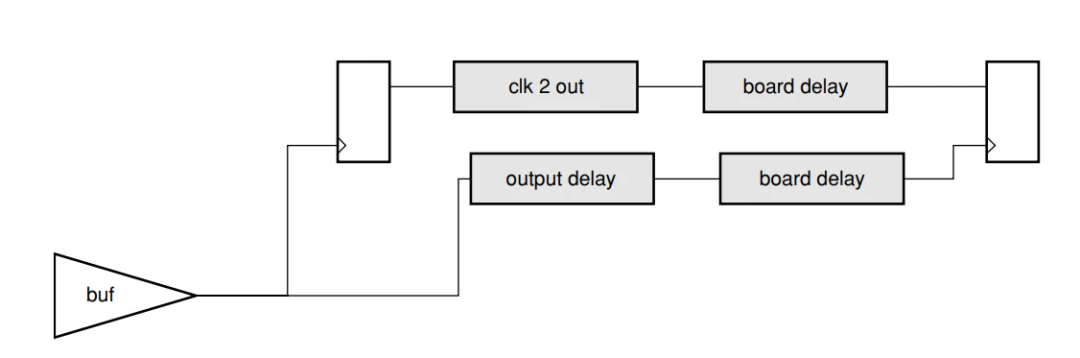

源同步對應的時間模型如下圖,相比于系統同步,只需考慮輸出延時和板間延時

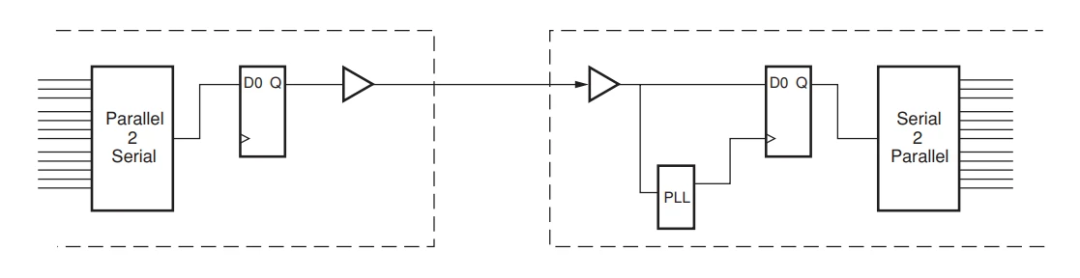

自同步:源同步設計會帶來時鐘域的增加,如上圖中的clk2,因此,出現了自同步這種方式,時鐘信號和數據信號在同一路傳輸。

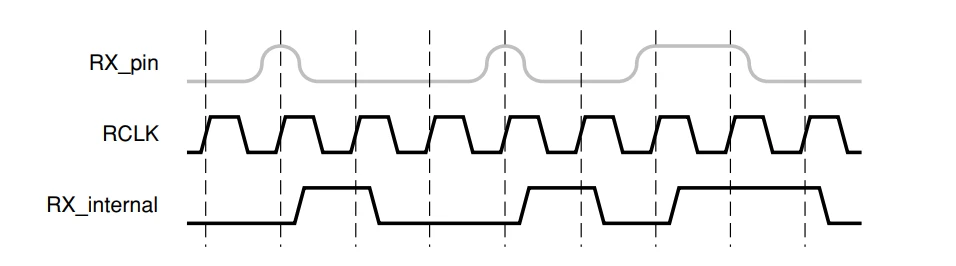

對應的時間模型如下圖,自同步中包含了3個主要模塊:串并轉換,并串轉換以及時鐘數據恢復單元

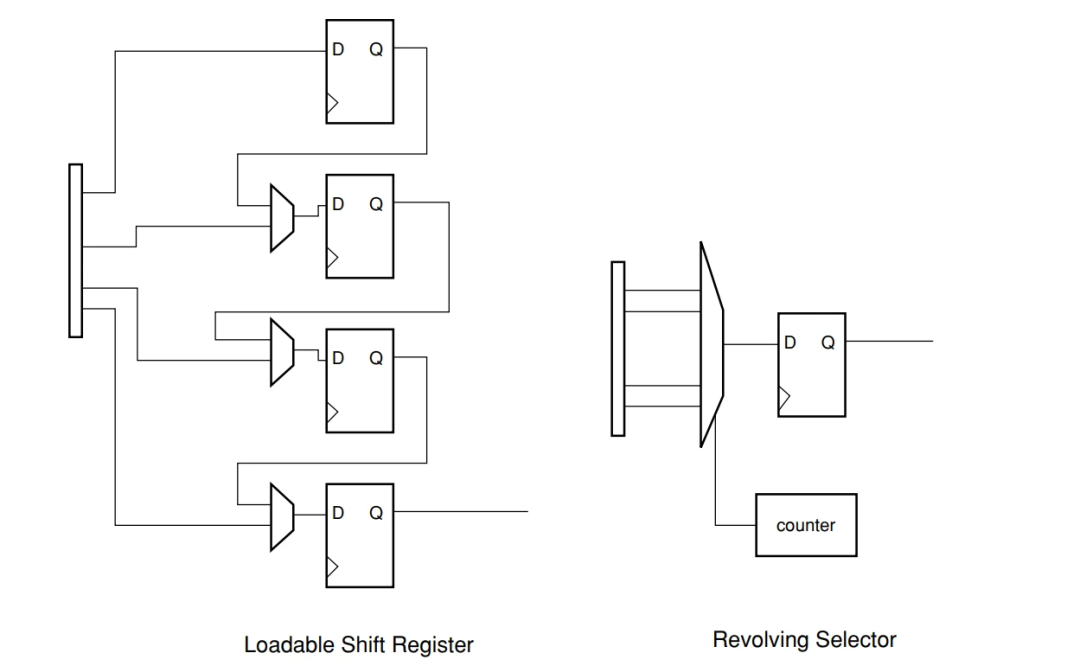

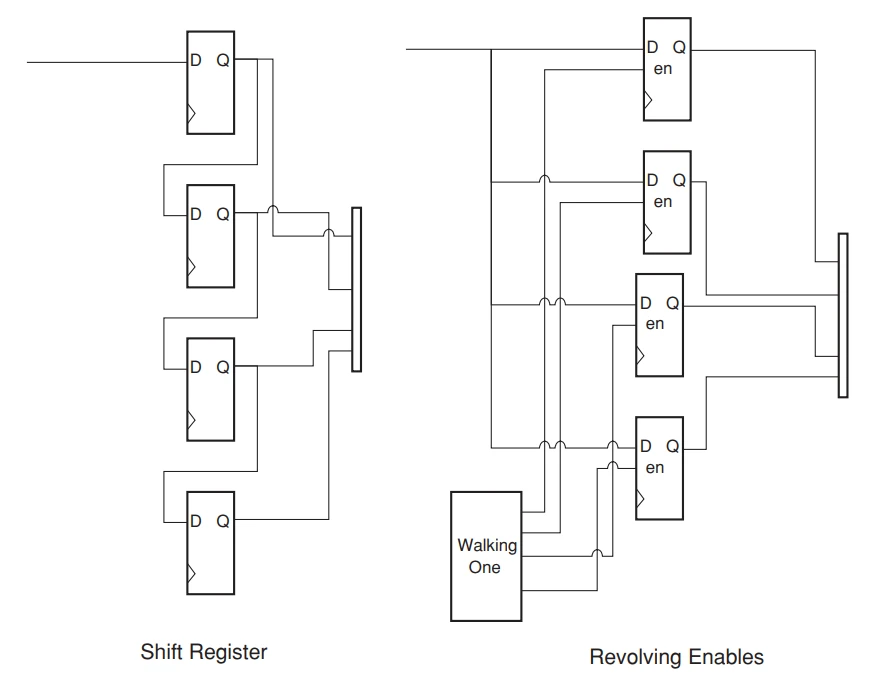

并串轉換有兩種實現方式:移位寄存器,旋轉選擇器(revolving selectors)

串并轉換的方式與并串轉換相反

時鐘數據恢復

時鐘數據恢復是通過PLL去同步一個和生成輸入串行數據流的時鐘頻率相匹配的時鐘

2.2 Serdes

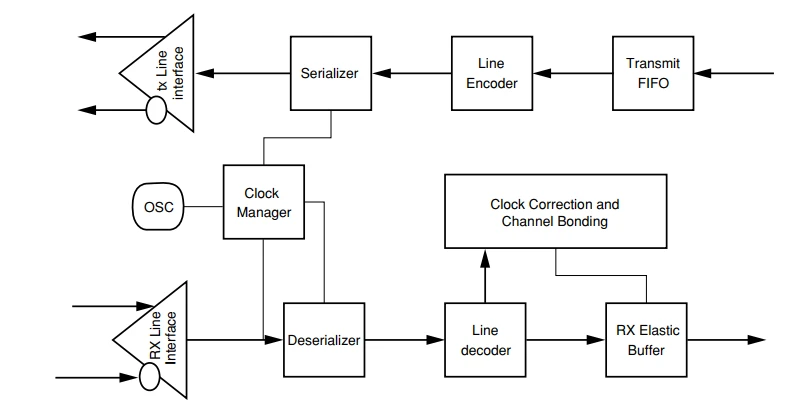

Serdes是屬于自同步的一種,通常結構如下

Serializer(并串轉換):將并行數據流轉換成串行數據

Deserializer(串并轉換): 將串行數據流轉換成并行數據

Rx (Receive) Align:將輸入數據以合適的長度進行分組,從自動檢測到用戶控制的位流分隔有多個不同的機制

Clock Manager:管理設計中需要的不同時鐘,包括分頻時鐘,倍頻時鐘,以及時鐘恢復

Transmit FIFO (First In First Out): 將需發送的數據先存儲

Receive FIFO:允許在移除接收到的數據前先進行存儲,對于需要進行時鐘糾正的系統很重要

Receive Line Interface:指模擬接收電路,包括差分接收器,以及正向均衡或反向均衡

Transmit Line Interface:模擬發送電路,可以改變驅動強度

Line Encoder:將數據編碼成一種更有友好的線性格式,包括將無變化的長序列移除,對于serdes不是必需的模塊

Line Decoder:將經過Line Encoder的數據恢復成原始數據

Clock Correction and Channel Bonding:允許糾正發射時鐘和接收時鐘的差異,也可以糾正不同信道中時鐘的偏斜

三、 7系列GTX/GTH

GT的全稱為Gigabit Transceiver ,是基于serdes技術發展起來的。Xilinx 7系列器件的收發器有GTX和GTH兩類,GTX支持的線速率范圍為500Mb/s到12.5Gb/s

GTH支持的線速率范圍為500Mb/s到13.1Gb/s. GTX/GTH可以通過配置靈活使用。

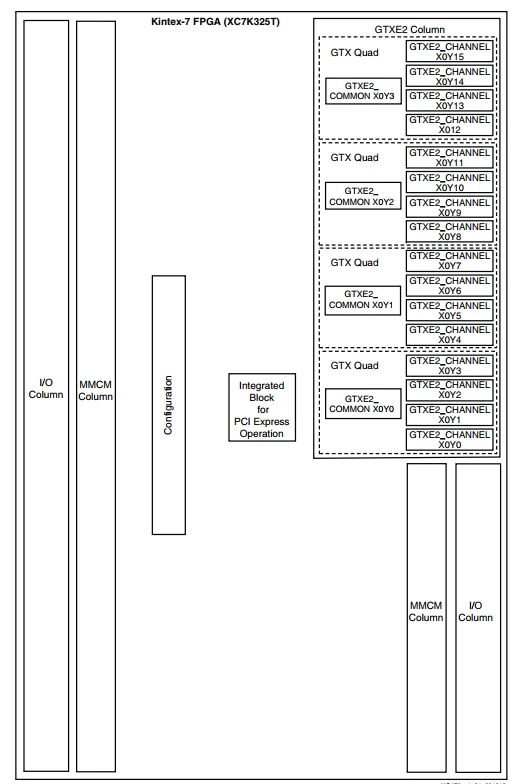

3.1 GTXE2

下圖右上角顯示了Kintex-7中GTXE2的位置,由4個GTX Quad組成,每個GTX Quad由一個GTXE2_COMMON和4個GTXE2_CHANNEL組成,其中GTXE2_COMMON和GTXE2_CHANNEL是用于例化該單元的原語。

3.2 Quad

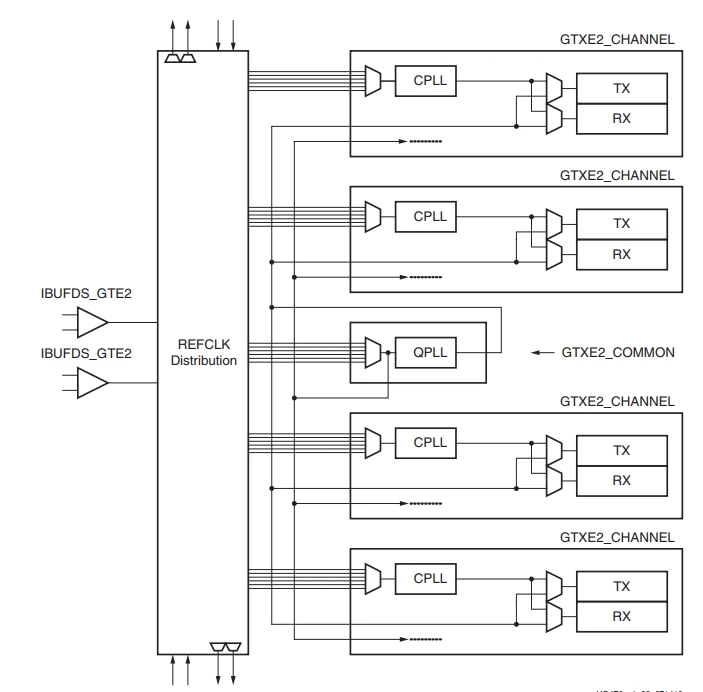

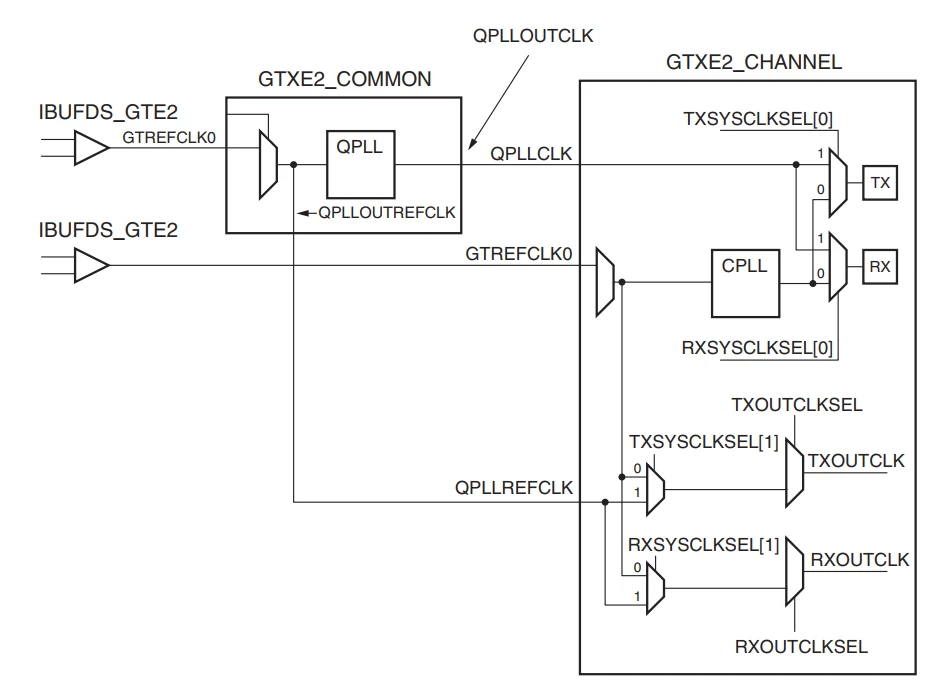

單個Quad的內部結構如下圖,包含了1個GTXE2_COMMON和4個Four GTXE2 CHANNEL,時鐘都是來自差分時鐘輸入,有兩個差分輸入對IBUFDS_GTE2,通過一個參考時鐘分配單元傳輸到GTXE2_CHANNEL中的CPLL和GTXE2_COMMON中的QPLL

3.3GTXE2_CHANNEL

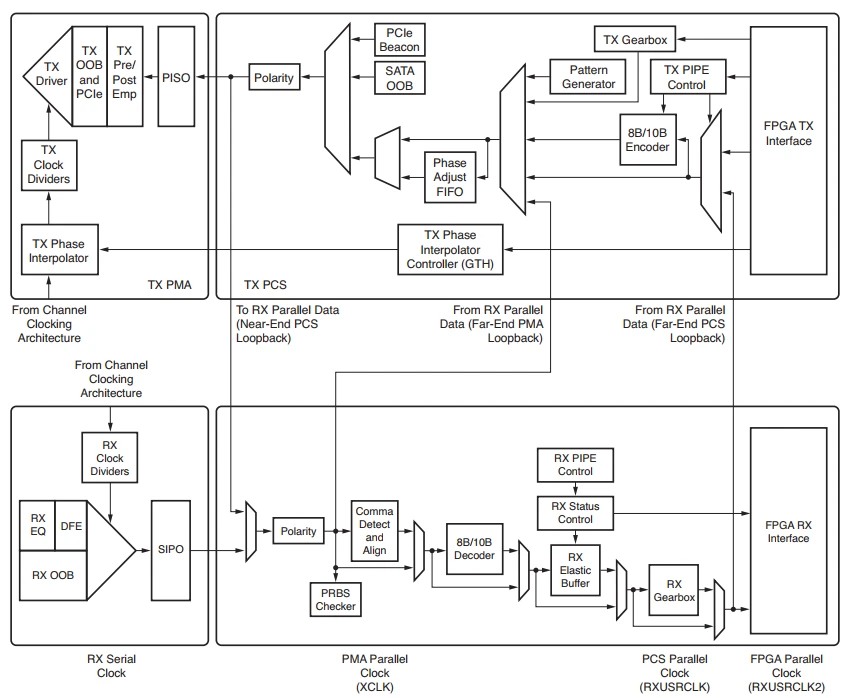

GTXEW_CHANNEL的內部結構如下圖,模塊較多,結構也復雜。

3.4 參考時鐘結構

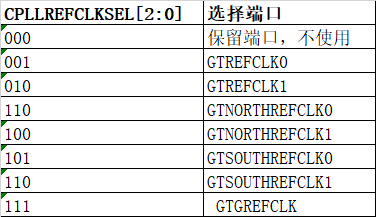

QPLL和CPLL(Channel PLL)是GT的時鐘管理單元,用于生成以及管理時鐘信號,從而實現數據的高速傳輸。CPLL是使用環形振蕩器的PLL,QPLL是使用LC共振器的PLL。時鐘來源于輸入的參考時鐘,其中GTSOUTHREFCLK/GTNORTHREFCLK表示參考時鐘來自南北方向其他Quad的參考時鐘,所謂的南北方向也即臨近的上下Quad的參考時鐘。

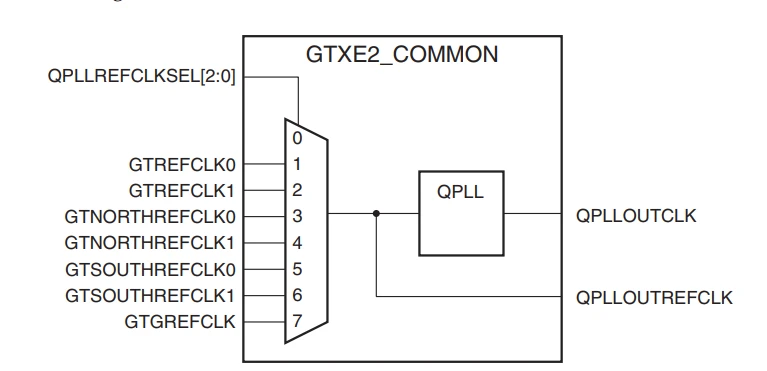

QPLL的時鐘連接如下圖,如果需要使用QPLL,必須例化GTXE2_COMMON/

GTHE2_COMMON。其中QPLLREFCLKSEL為參考時鐘選擇端口,為3bit的數據。具體的端口選擇規則如下表

GTREFCLK0/GTREFCLK1為IBUFDS_GTE2使用的外部時鐘,GTGREFCLK為FPGA內部生成的參考時鐘輸入端口,一般用于內部測試。

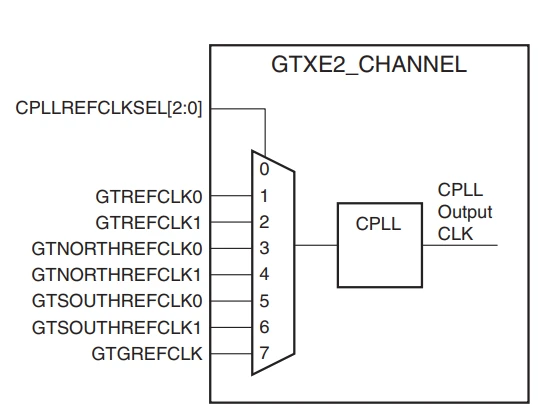

CPLL的時鐘連接如下圖,如果只使用CPLL時,也必須例化GTXE2_COMMON/GTHE2_COMMON

對于單個Quad來說,參考時鐘可來自6個輸入引腳

1)Quad自身的GTREFCLK0和GTREFCLK1

2)來自上方相鄰Quad參考時鐘GTSOUTHREFCLK0和GTSOUTHREFCLK1

3)來自下方相鄰Quad參考時鐘GTNORTHREFCLK0和GTNORTHREFCLK1

4)1個外部參考時鐘最多驅動3個Quad

3.4.1 外部參考時鐘

每一個Quad有兩對差分輸入端口可以連接外部時鐘源,使用IBUFDS_GTE2可以實例化使用來自外部的時鐘作為參考時鐘對

3.5 CPLL

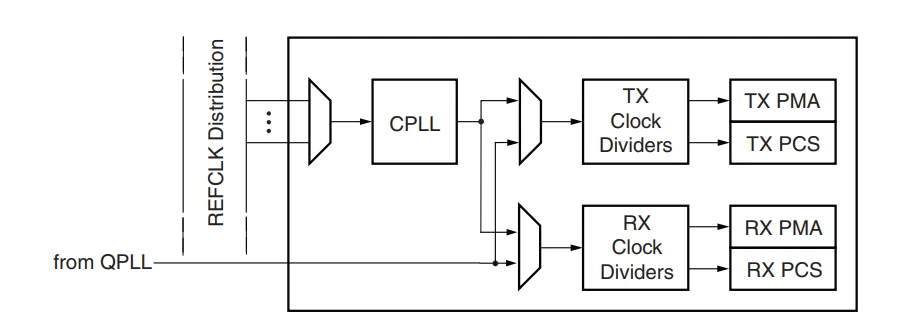

上一小節描述了外部時鐘與QPLL/CPLL的連接關系,下面是CPLL內部時鐘連接,TX和RX時鐘分頻器都可以選擇時鐘來自CPLL還是QPLL, 然后再傳輸到對應的PMA/PCS的串并時鐘上

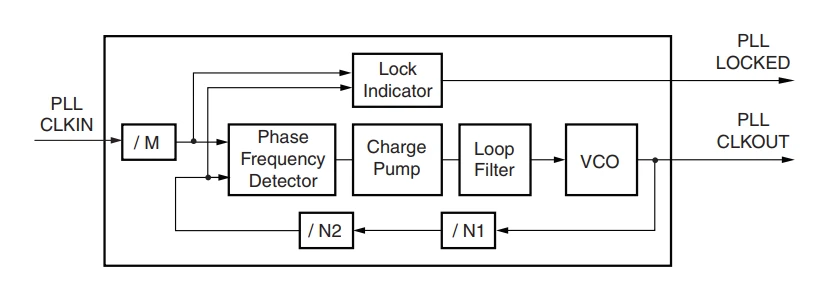

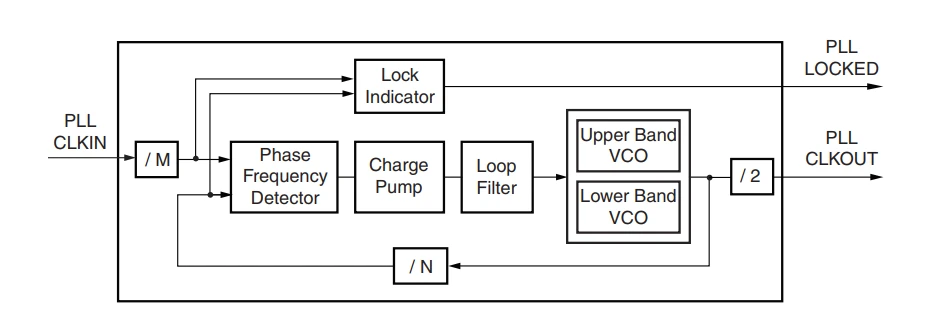

CPLL的內部結構如下圖

上述圖中的各系數含義如下圖

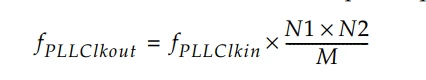

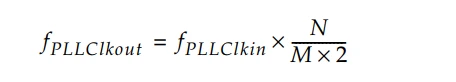

CPLL的時鐘輸出頻率計算公式為

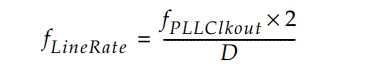

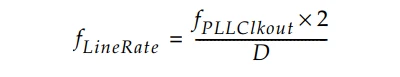

對應的線速率的計算公式為,D為TX/RX的時鐘分頻器的分頻系數,由于時鐘的上升沿和下降沿都可以使用,因此乘2

3.6QPLL

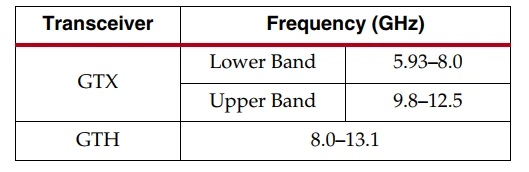

每個Quad包含了一個基于LC振蕩器的PLL,即QPLL,QPLL可以被同一個Quad內的收發信道使用,不能被其他Quad內的收發器使用。QPLL支持的速率在GTX和GTH中不同,在GTX中還分為低帶寬和高帶寬。

當運行的線速率超過CPLL的范圍時就需要使用QPLL,QPLL的內部結構如下圖

各系數的含義如下表

QPLL的輸出頻率計算公式如下

線速率的計算公式如下

四、收發器GTX/GTH

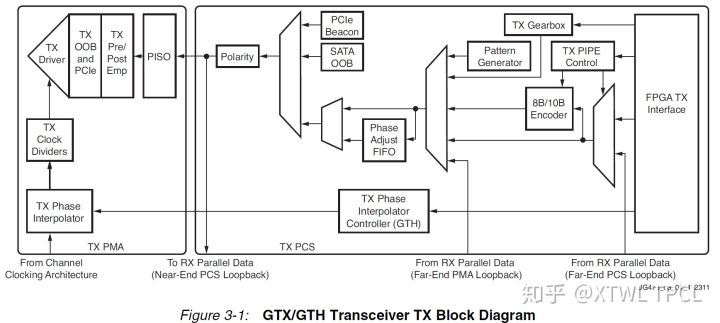

4.1 發送器TX

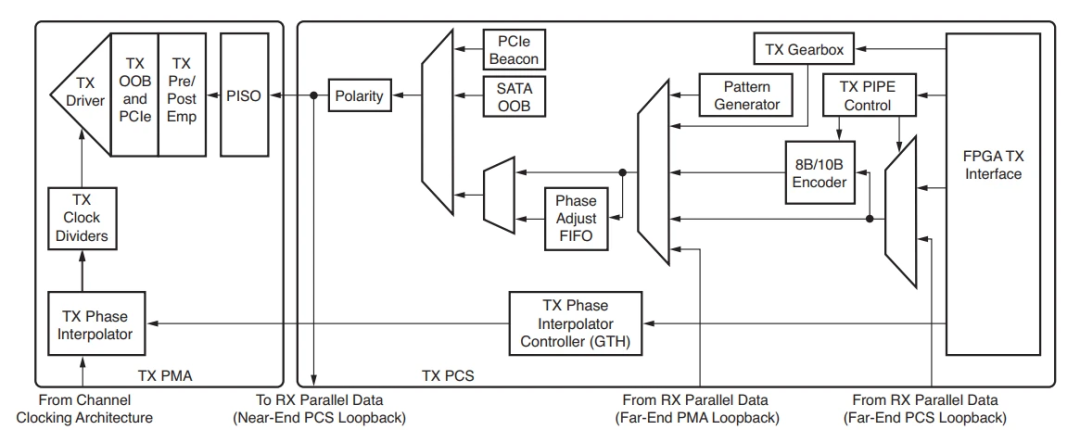

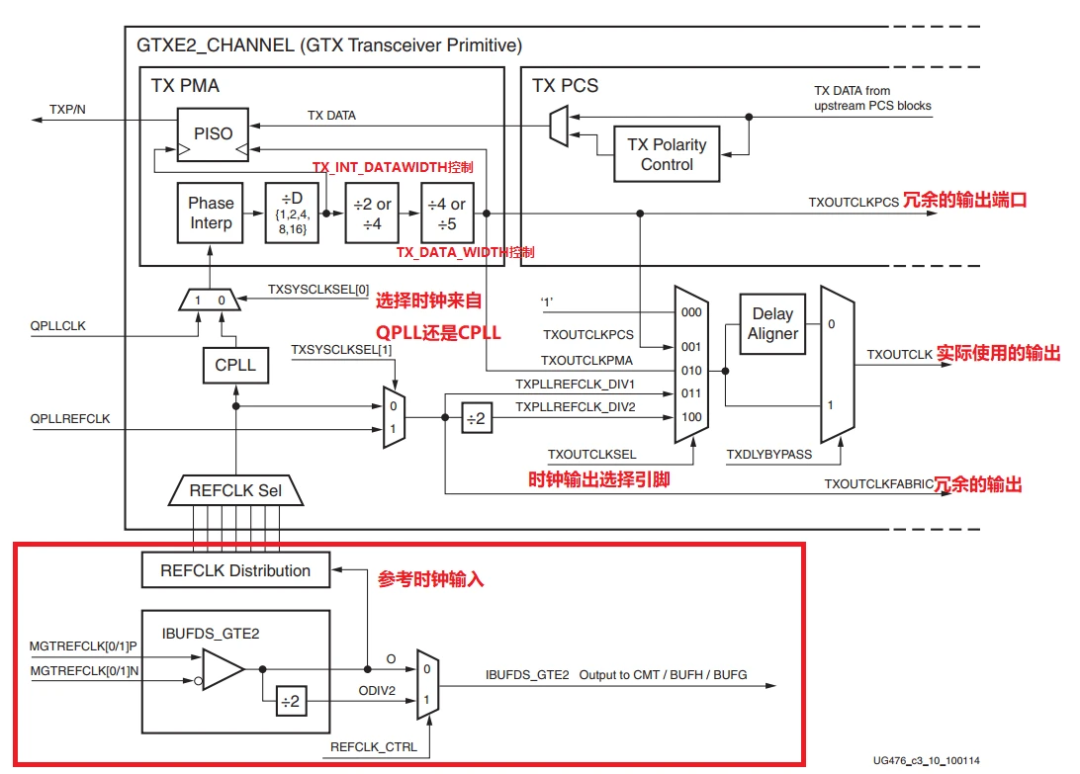

發送器的內部結構如下圖,每個收發器包含一個獨立的發送器,主要由左側的物理媒介適配層(?PMA)?和右側的物理編碼子層(?PCS)?組成。PMA子層負責高速串并轉換、?預/后加重、?接收均衡、?時鐘發生器及時鐘恢復等電路功能,?而PCS子層則包含8B/10B編解碼、?緩沖區、?通道綁定和時鐘修正等電路。?

并行數據從PFGA的內部流向發送器接口,通過PCS和PMA,轉換成串行數據被TX傳輸出去。

通過TX的結構圖可知,主要有以下模塊組成

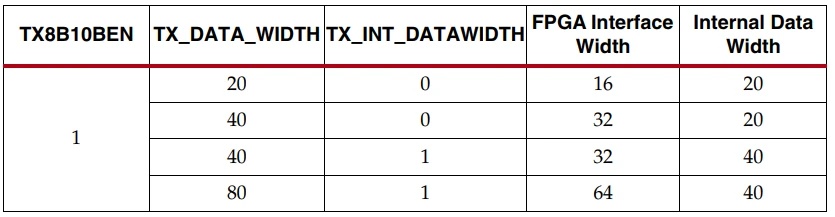

1.FPGA TX Interface:TX接口就像是進入TX數據路徑的網關,在時鐘TXUSRCLK2

的上升沿將要發送的數據寫入到TXDATA端口,TXDATA端口的寬度可配置成2,4,8個字節。具體配置為TX_DATA_WIDTH控制FPGA接口寬度(FPGA Interface Width),TX_INT_DATAWIDTH屬性控制內部數據寬度(Internal Data Width),對應關系如下圖。

2.TX 8B/10B Encoder:對于輸出數據,很多協議使用8B/10B這一行業標準編碼方案,只要在每個字節增加2bit就可達到DC平衡(直流平衡)和界限差異從而恢復時鐘信號。GTX/GTH有一個專用的8B/10B TX路徑來編碼發送數據,而不需要其他的FPGA資源。

3.TX Gearbox:一些高速數據傳輸協議會用64B/66B的編碼方式來代替8B/10B編碼,可在維持原有編碼方案的優勢下減少增加bit的開銷。TX Gearbox支持2字節、4字節、8字節接口,但是加擾數據需要使用FPGA的邏輯資源來實現。

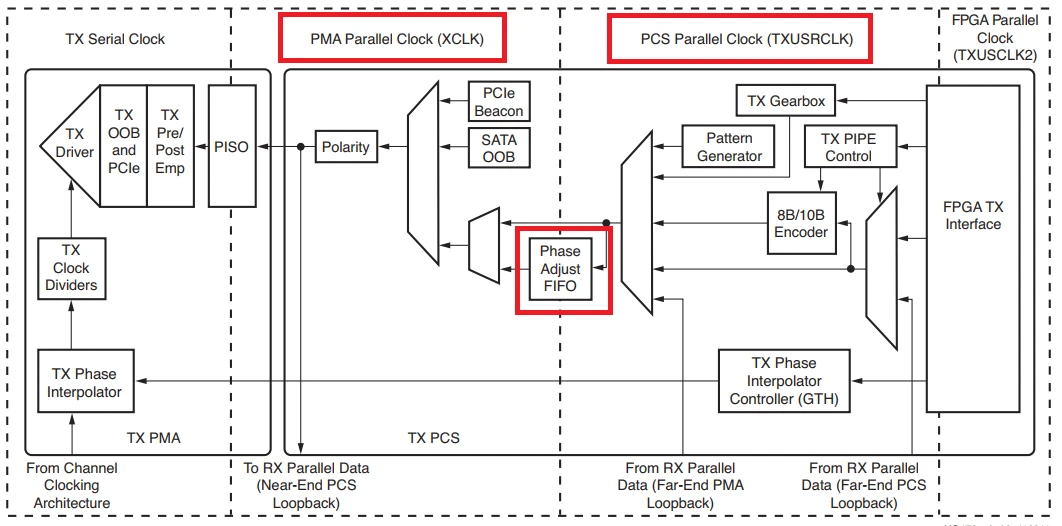

4.TX Buffer:GTX/GTH收發器的發送數據路徑在PCS部分上有兩個內部的并行時鐘域,即PMA并行時鐘域XCLK和PCS的TXUSRCLK時鐘域。

如果要發送數據,XCLK的速率必須和TXUSRCLK速率匹配,兩個時鐘域不能存在相位差。因此,GTX/GTH中有一個TX相位對齊電路來解決XCLK和TXUSRCK間的相位差,即下圖的Phase Adjust FIFO,當TX Buffer為bypass模式時,就使用Phase Adjust FIFO。所有的發送數據要么被TX buffer使用,要么被Phase Adjust FIFO使用。

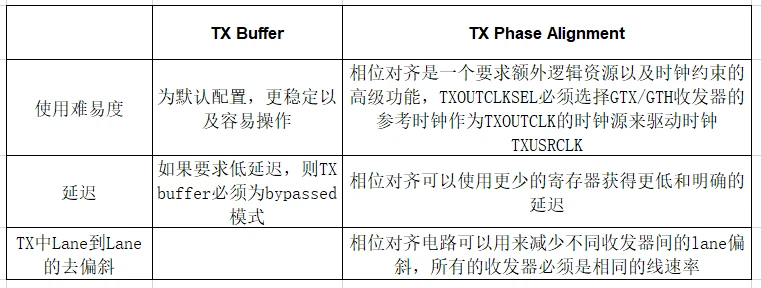

TX buffer和TX buffer bypass(相位對齊電路)如下圖

5.TX Buffer Bypass:TX buffer的bypass模式是7系列收發器的高級功能。前面提到TX相位對齊電路可以調整PISO并行時鐘域與TXXCLK時鐘域的相位差。它也可以連續地調整TXUSRCLK來控制TX延時分配,從而補償因溫度和電壓變化帶來的波動。TX相位調整與延時對齊都可以由GTX自動控制,也可也用戶手動控制。

6.TX Pattern Generator:偽隨機序列(PRBS)通常用于測試高速鏈路的完整性。序列看似隨機的,卻是有一定的特性可以用來測試鏈路的質量。GTX/GTH的pattern generator可以生成多個行業標準的PRBS,如PRBS-7,PRBS-15,PRBS-23,PRBS-31

7.TX Polarity Control:如果差分引腳TXP和TXN在PCB上意外地被交換了,TX發送的數據將會取反。一種辦法是在并行數據串行化以及發送前將其極性取反,來抵消在差分對上的極性取反。也可以通過TX極性控制模塊來實現輸出數據的極性取反。

8.TX Fabric Clock Output Control:TX fabric時鐘輸出控制模塊有兩部分組成:串行時鐘分頻控制與選擇器,并行時鐘分頻控制與選擇器。

下圖中分頻模塊/2或/4的由TX_INT_DATAWIDTH屬性決定,/4與/5由TX_DATA_WIDTH

決定

9.TX Phase Interpolator PPM Controller:TX相位插入器PPP控制器可以動態地控制TX相位插入(TX PI)。該模塊位于TX的PCS模塊,接收來自TX接口的數據并且輸出到TX的PMA上。當需要對TX PMA上的數據進行微調時才會使用,TX PI可以控制PLL的輸出時鐘,反過來也可以被TX相位插入PPM控制器模塊控制。

10.TX Configurable Driver:TX可配置驅動器是一個高速電流模式差分輸出緩沖器。為了最好的保持信號的完整性,該模塊可以通過控制差分電壓,發送預加重進行Pre-cursor和Post-cursor,校準終端電阻來實現。

11.TX Receiver Detect Support for PCI Express Designs:PCIE指標包括允許發送器在一個指定連接上檢測接收器是否存在,確認接收器是否存在是基于TXP/TXN的上升沿實現的。

12.TX Out-of-Band Signaling:每一個GTX/GTH收發器都支持生成帶外序列,可用在SATA,SAS以及PCIE協議中。

4.2 接收器RX

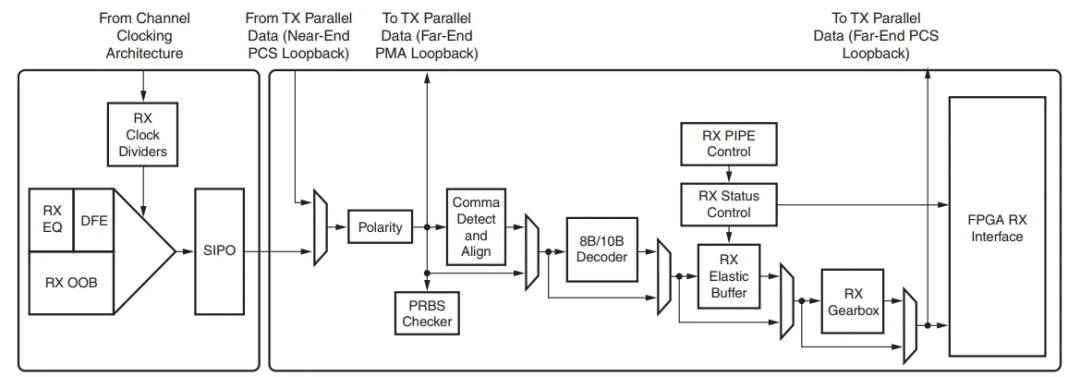

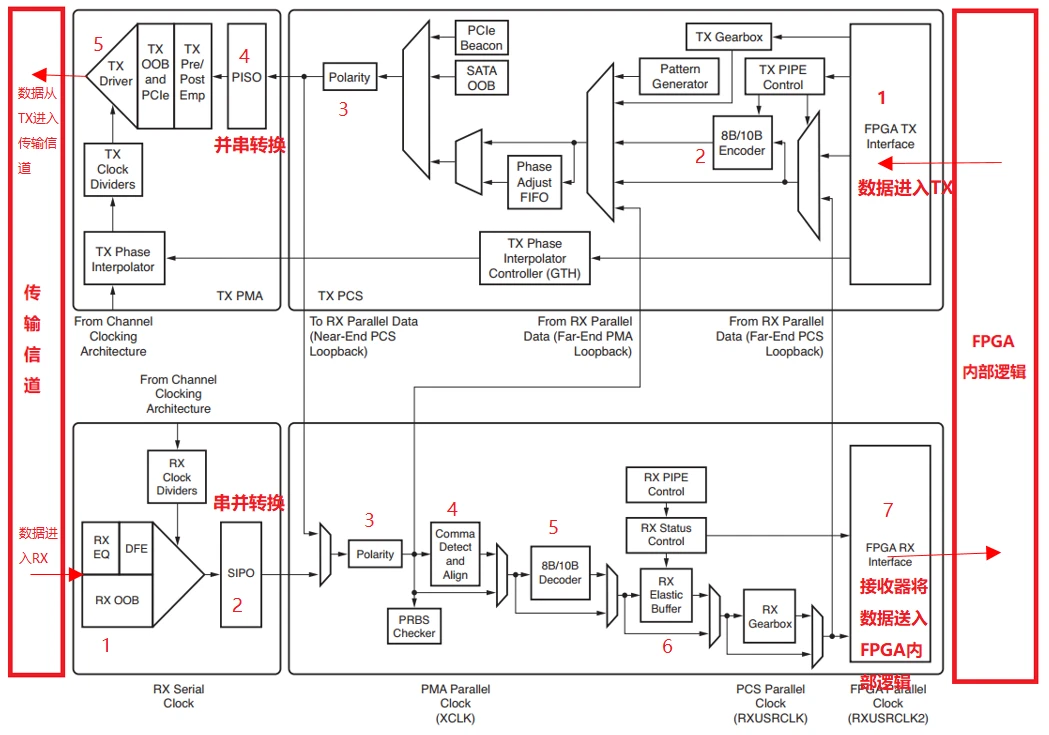

接收器RX的內部結構圖如下,每個GTX/GTH的收發器都包含一個獨立的接收器RX,和發送器類似,由PCS和PMA兩大部分組成,高速串行數據從每個接收器的PMA到PCS,然后進入到FPGA內部邏輯。

接收器的主要由以下部分組成

1.RX Analog Front End:RX AFE是一個高速電流模式輸入差分緩沖器,可以配置RX終端的電壓以及校準終端電阻。

2.RX Out-of-Band Signaling:每一個GTX/GTH接收器都支持解碼SATA,SAS

和PCIE協議的帶外序列。

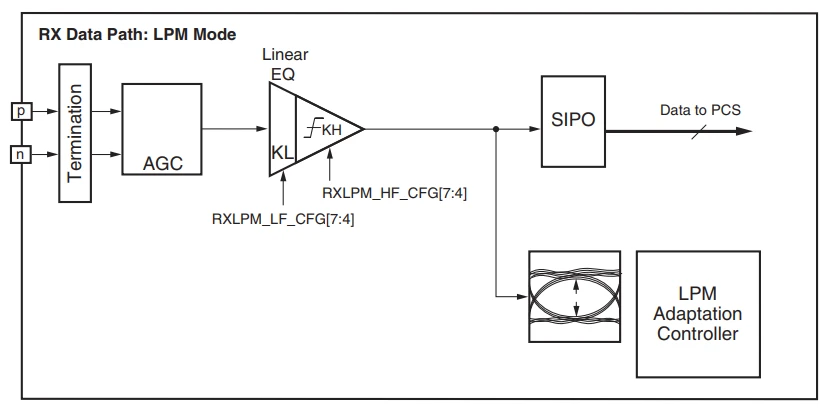

3.RX Equalizer (DFE and LPM):通常發送媒介或信道是一個帶寬有限的信道,信號傳輸存在衰減或失真。對于接收器在要在功耗和性能間折衷,有兩種自適應的過濾方式。如果要功耗優先,則接收器有一種低功耗模式(LPM)。如果要信號失真減少,則選擇DFE模式。相比于使用線性均衡器,DFE可以更好的調整過濾參數來補充發送信道的衰減,它是一個離散時間自使用高通濾波器。

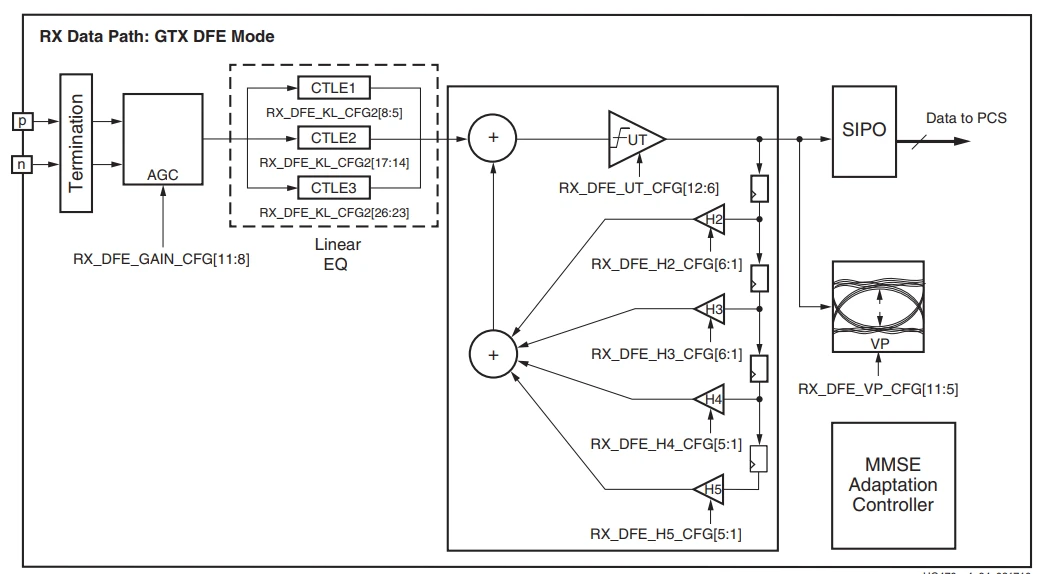

GTX接收器的DFE模式結構如下圖

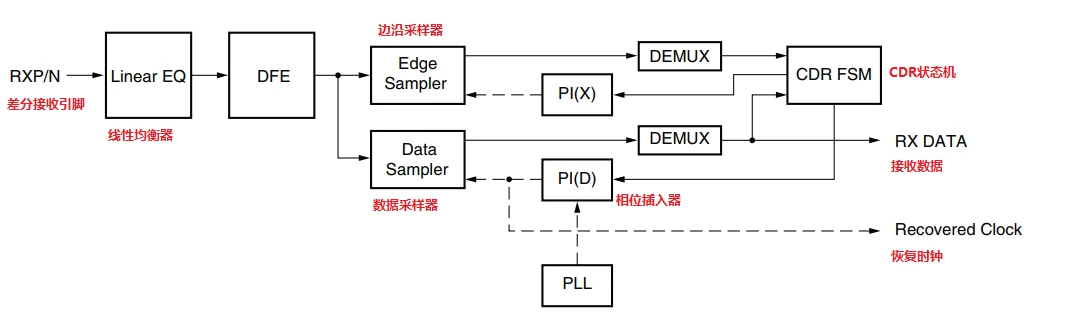

4.RX CDR:RX CDR電路用于從一個輸入數據流中恢復出其中的時鐘信號。

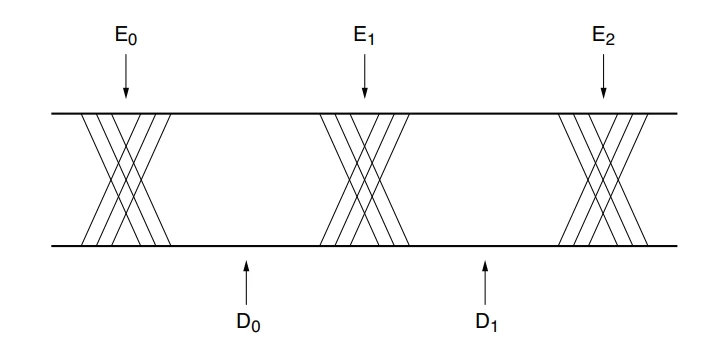

CDR狀態機使用來自邊沿采樣器和數據采樣器的數據來決定輸入數據流的相位以及控制相位插入器(PIs)。當數據采樣器的相位處于數據眼圖的中間位置時,邊沿采樣器的相位將鎖定在數據流的轉換區域。CPLL/QPLL為相位插入器PI提供基準時鐘,PI反過來產生好的采樣相位使得CDR狀態機有最佳的相位控制。

5.RX Fabric Clock Output Control:和發送器類似,RX時鐘分頻控制模塊主要由兩部分組成:串行/并行時鐘分頻器控制以及選擇器控制

6.RX Margin Analysis:隨著線速率以及信道衰落增加,對于接收端的均衡器要求更高。7系列的RX眼圖掃描可以在均衡器后測量以及將接收器眼圖邊沿可視化。

7. RX Polarity Control:如果差分引腳RXP和RXN在PCB上意外地被交換了,RX接收到的數據將會取反。一種辦法是在SIPO后并行數據進入PCS中將其極性取反,來抵消在差分對上的極性取反。也可以通過RX極性控制模塊來實現數據的極性取反。

8.RX Pattern Checker:RX模式檢查器可以設置去檢查四種行業PRBS模式(PRBS-7/PRBS-15/PRBS-23/PRBS-31)的任意一種,檢查器是自同步并且在"逗號"對齊或解碼前處理輸入數據,主要用于測試信道上信號的完整性。

RXPRBSSEL用于選擇PRBS模式,值與對應模式關系如下

001: PRBS-7

010: PRBS-15

011: PRBS- 23

100: PRBS-31

當PRBS檢查器運行時,會嘗試在輸入數據中去尋找選擇的模式,如果輸入數據已經發送器或差分對取反,接收到的數據將會通過RXPOLARITY來進行取反。當查找到選擇的模式后,將會通過對比輸入的模式與預期的結果模式來檢測PRBS錯誤,預期的模式時來自之前的輸入數據。檢查器會統計錯誤字(每個字20bit)的數量。因此,如果輸入的并行數據包含2個以上的錯誤時,錯誤的字數和錯誤的bit數就會出現不一致的情況,當統計的錯誤數達到0XFFFF時計數器停止計數。

9.RX Byte and Word Alignment:串行數據在被用于并行數據前必須按符號對齊,為了對齊成為可能,發送器發送一個可識別的序路,該序列稱為“逗號”。接收器在接收數據中查找“逗號”,找到逗號后會將其移除。

10.RX 8B/10B Decoder:如果接收到的是8B/10B編碼,接收器一定能解碼,因為接收器有一個自帶的8B/10B解碼器,該解碼器有以下特點

1)支持2字節,4字節,8字節的數據路徑操作

2)為差異提供菊式聯機運行

3)生成K字符和狀態輸出

4)如果輸入數據不是8B/10B編碼可以轉為Bypassed模式

5)當遇到非表內錯誤時,可以輸出10bit的編碼值

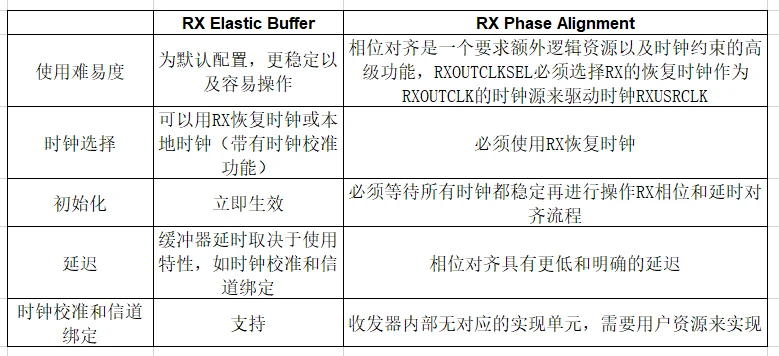

11.RX Buffer Bypass:RX相位對齊電路用于調整SIPO并行時鐘域和RX XCLK時鐘域間的相位差,從而使得數據有效地從SIPO傳輸到PCS.同時可以通過調整RXUSRCLK實現RX延時對齊從而消除溫度和電壓變化的影響。

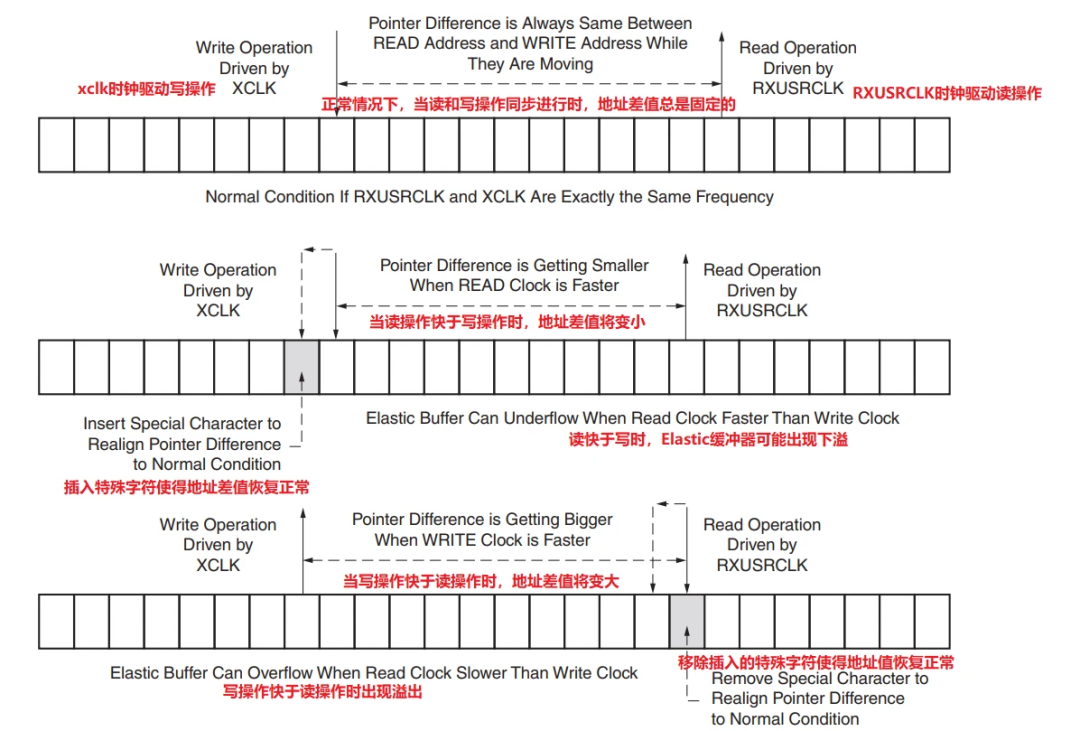

12.RX Elastic Buffer:RX數據路徑上在PCS中有2個內部并行時鐘域,PMA并行時鐘域XCLK和RCUSRCLK時鐘域。為了接收數據,PMA并行速率必須足夠的接近RXUSRCLK速率,兩者之間的相位差必須要消除,這個就需要靠RX Elastic緩沖器。

13.RX Clock Correction:前面提到RX Elastic緩沖器可以消除兩個不同時鐘域的相位差,但XCLK和RXUSRCLK不是完全相同,RX elastic緩沖器可能會溢出或空缺多。為了解決這種問題,TX會周期性的發送一個或多個特殊字符,接收器接收到該特殊字符會將其移除或復制。當緩沖器滿了時會將其移除,當緩沖器很空時會對齊進行復制,從而避免溢出或空缺的狀態。

14.RX Channel Bonding:像PCIE和XAUI協議可以將多個串行收發器連接成一個單個的高流量信道,每個串行收發器為一個lane。除非每個串行連接是完全相同的長度,否則兩個lane間即使是同時發送,接收也會出現不同步,從而有偏斜。通過信道綁定可以消除這種偏斜,對于一個綁定信道的收發器,所有發送器同時發送一個信道綁定字符(或一個字符序列),接收器接收到該字符后,接收器會根據字符的偏斜調整RX elastic緩沖器的延遲,從而數據可以無偏斜的到達RX的用戶接口。信道綁定支持8B/10B編碼,但不支持64B/66B,64B/67B,128B/130B以及擾碼數據。

15.RX Gearbox:同發送端一樣,RX gearbox也支持64B/66B和64B/67B頭和載荷分離

16.FPGA RX Interface:RX接口是進入RX數據路徑的網關,也即是數據經過接收器后進入到FPGA內部邏輯的控制接口。通過在時鐘RXUSRCLK2的上升沿讀取來自RXDATA端口的數據從而接收數據。端口的寬度也是可配置的,可為2,4,8個字節。

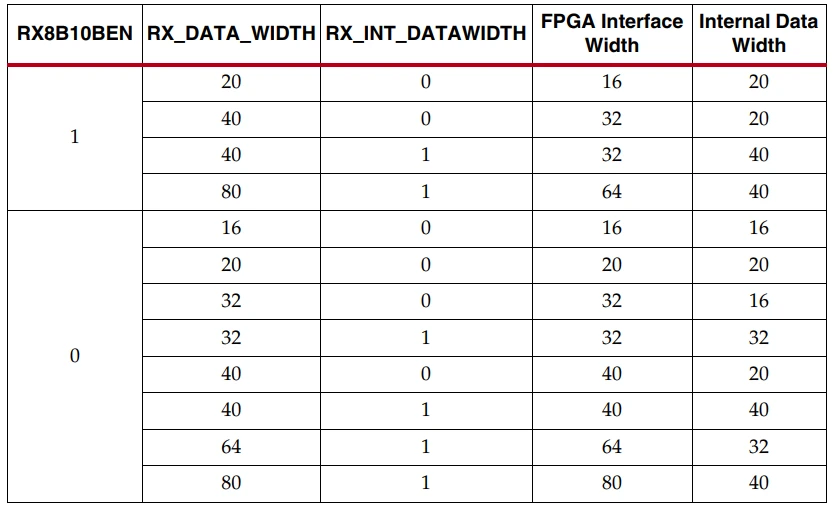

同TX接口類似,屬性RX_INT_DATAWIDTH控制內部數據寬度是2字節還是4字節,屬性RX_DATA_WIDTH控制FPGA接口寬度。但與TX有差異的是,也支持8B/10B為bypassed模式時的寬度配置,也即下圖RX8B/10BEN為0時的場景。

4.3 TX與RX全流程分析

借用前面的GTXE2_CHANNEL的內部結構圖,左右各加上信道傳輸模塊,FPGA內部邏輯,即是一個完整的閉環。圖中數字為根據數據流程對一些主要流程進行標記

發送流程:FPGA內部的串行數據通過TX接口進入到TX內部,經過8B/10B進行編碼處理,在TX buffer上進行相位調節,Polarity中極性極性處理,進入到PISO完成并串轉換,最后由TX Driver將串行數據發送出去。

接收流程:TX發送的數據經過傳輸信道進入到RX中,先是通過RX EQ/DFE或RX OOB對信道衰減進行的一些處理,進入SIPO實現數據串行轉換成并行數據,完成極性處理以及相位對齊,然后進行解碼操作,數據對齊后再通過RX接口進入到FPGA的內部,從而一個收發流程完成。

-

收發器

+關注

關注

10文章

3424瀏覽量

105959 -

數據傳輸

+關注

關注

9文章

1880瀏覽量

64554 -

時鐘

+關注

關注

10文章

1733瀏覽量

131446

原文標題:Xilinx 7系列收發器GTX入門講解

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于Xilinx 7系列GTX高速收發器的初步調試方案

Vertex 7 GTX收發器中沒有丟失同步是什么

7系列設備中的GTX收發器如何獲得最佳功耗?

請問如何提高GTX收發器的RX能力?

介紹Xilinx 7系列FPGA收發器硬件設計主要注意的一些問題

Xilinx 7系列FPGA收發器架構之硬件設計指導(一)

Xilinx 7系列收發器GTX入門講解

Xilinx 7系列收發器GTX入門講解

評論