產品簡述

MS9280 是單芯片、單電源、10bit、35MSPS 模數轉換器,內部集成

采樣保持放大器和電源基準源。MS9280 使用多級差分流水線架構,保

證 35MSPS 數據轉換速率下,全溫度范圍內無失碼。

MS9280 的輸入適合圖像視頻和通信系統應用。用戶可以根據實際

需要,選擇單端輸入或者差分輸入,也可以選擇輸入范圍和消除失調。

MS9280 內部集成的采樣保持放大器,既適合復用系統,又適合開

關全波電壓范圍的連續信道。采樣單信道的輸入頻率可以超過奈奎斯特

頻率。借助內部的鉗位電路,交流耦合輸入可以移位到一定的固定電平,

動態性能非常完好。

MS9280 內部集成可編程基準源。根據系統需要,可以選擇外部高

精度基準,以滿足系統精度的要求。

出量化范圍檢測位信息表示輸入信號超過了最小和最大量化范圍的。

MS9280 可工作在 2.7V ? 5.5V 單電源范圍,適合高速、低功耗的應

用范圍。MS9280 適合工業溫度范圍,-40°C 到+125°C。

主要特點

?10 bit、35 MSPS 流水線 ADC

?低功耗:90mV (3V 電源下)

?寬工作范圍:2.7V ? 5.5V

?高線性度: DNL:0.2 LSB

?低功耗控制模式

?三態門輸出

?量化范圍檢測

?內建鉗位功能

?高精度可編程基準電源

?中頻亞采樣高達 135MHz

應用

?圖像視頻

?通信系統

產品規格分類

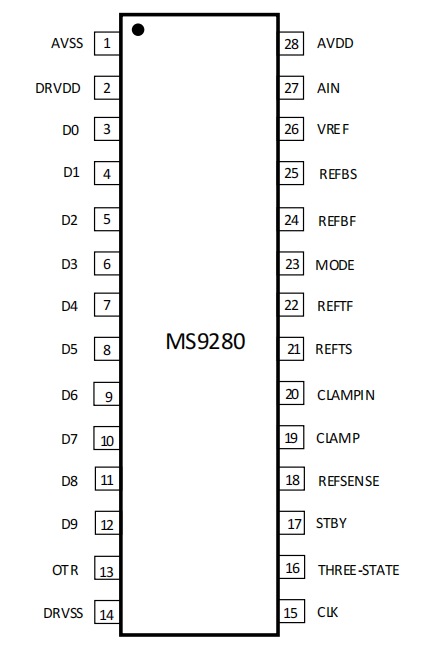

管腳圖

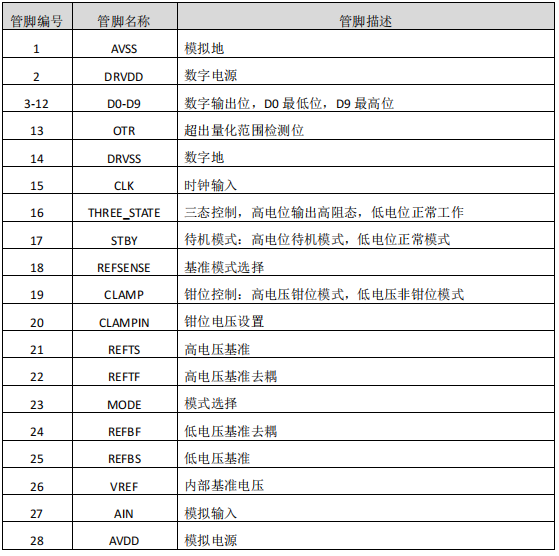

管腳說明

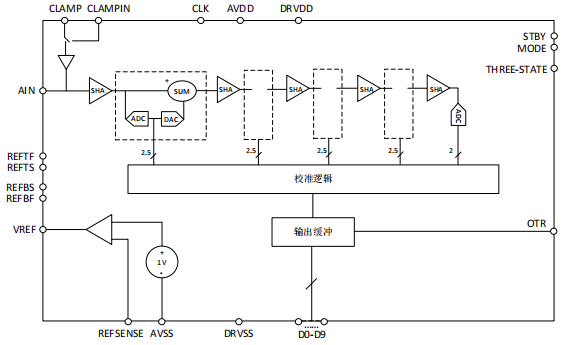

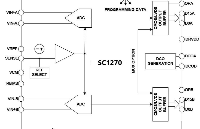

內部框圖

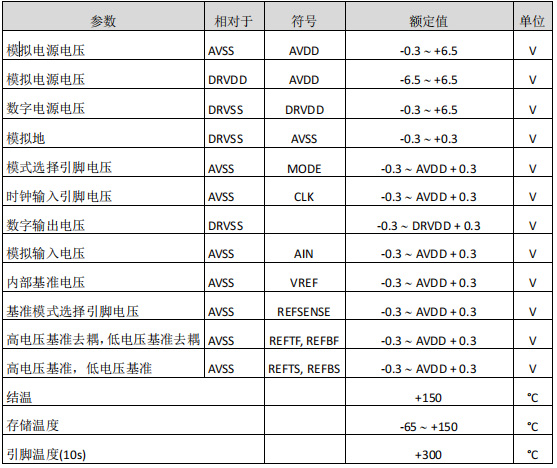

極限參數

芯片使用中,任何超過極限參數的應用方式會對器件造成永久的損壞,芯片長時間處于極限

工作狀態可能會影響器件的可靠性。極限參數只是由一系列極端測試得出,并不代表芯片可以正

常工作在此極限條件下。

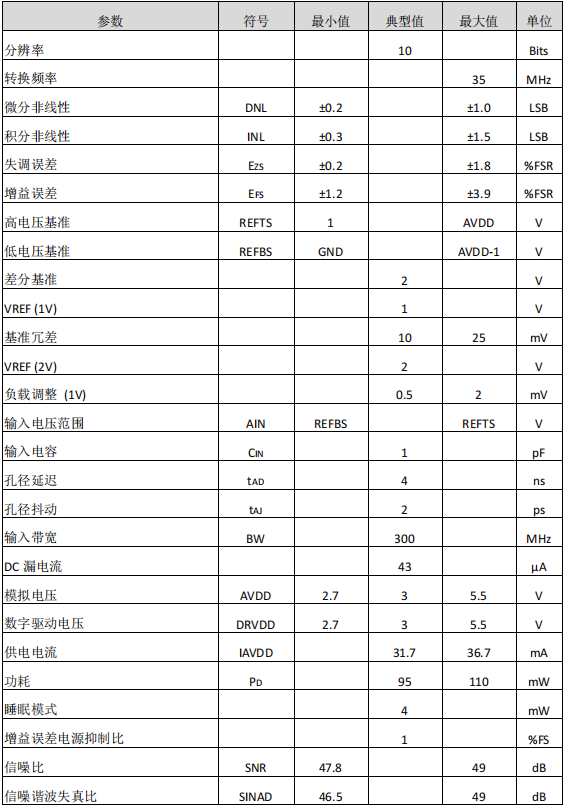

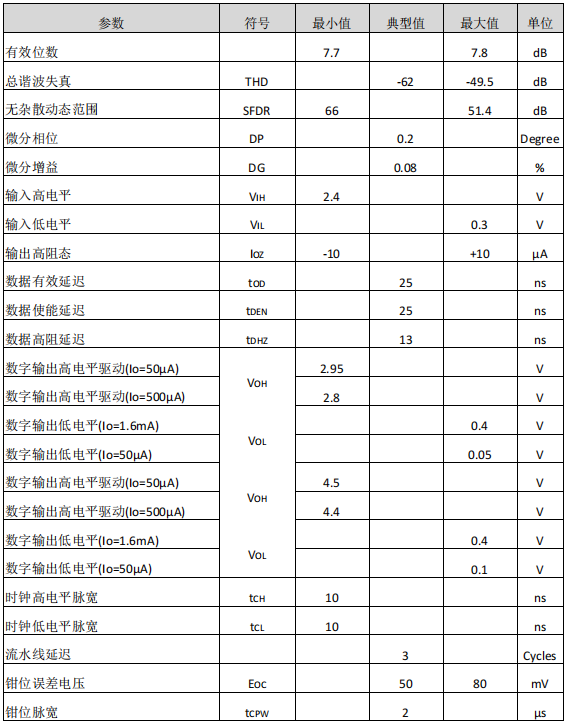

電氣參數

除特殊說明外,AVDD=+3V, DRVDD=+3V, Fs=35MHz (50%占空比),MODE=AVDD,2V 輸入范圍

0.5V 到 2.5V,外部基準。

如有需求請聯系——三亞微科技 王子文(16620966594)

應用說明

MS9280 利用多級流水線架構,實現低功耗高速數據轉換。將整個的轉換精度分成低精度的

單階子轉換器。在時序控制下,各階轉換的結果通過內部數字校準電路,實現高精度的數據轉換。

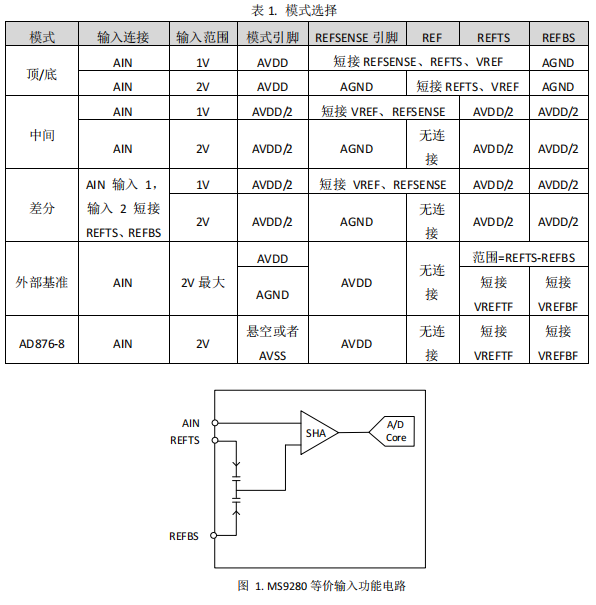

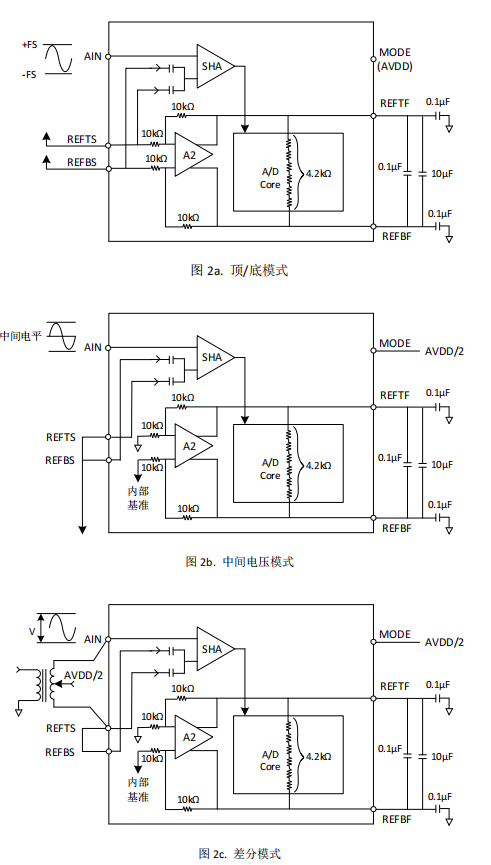

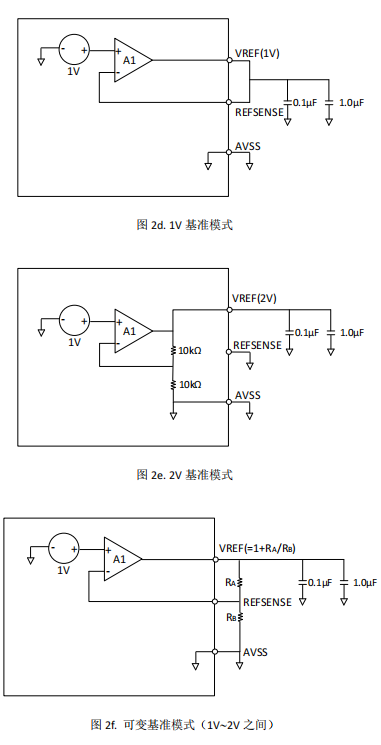

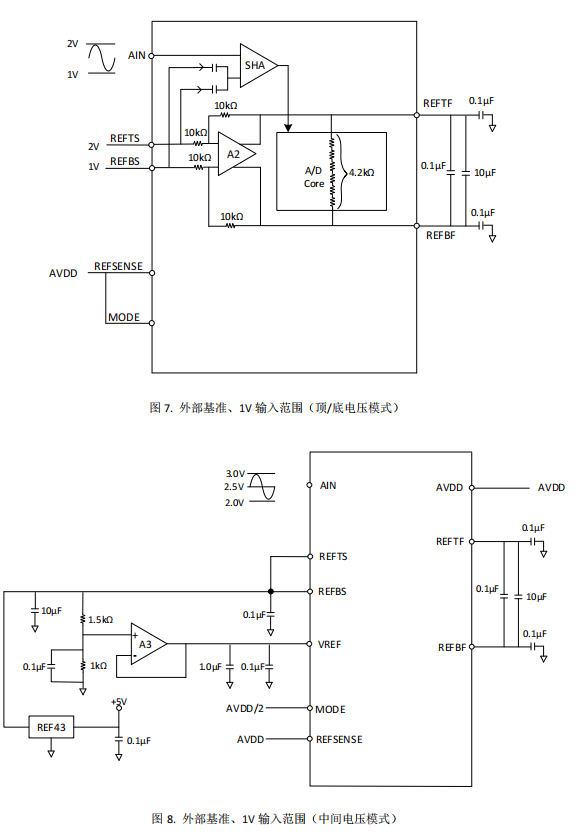

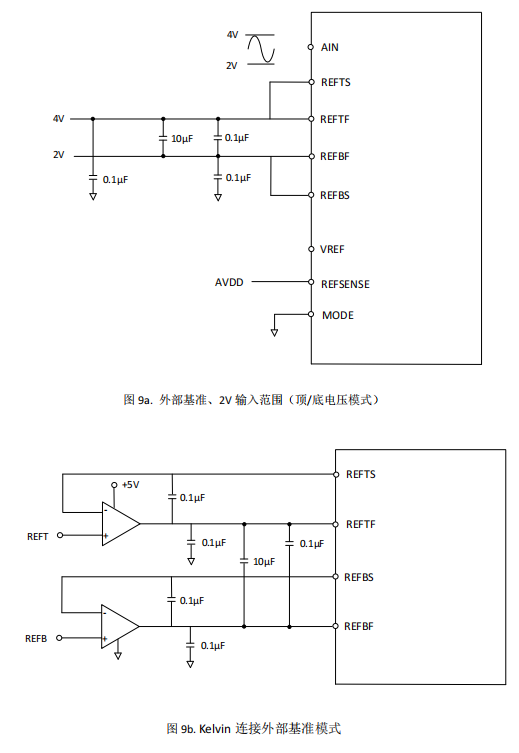

工作模式

MS9280 適合多領域的圖像視頻、通信和儀表應用,包括兼容 AD876-8 系列。可根據具體系

統需要,選擇合適的工作模式進行性能優化。為實現系統的靈活性,內部可編程開關實現了不同

的工作模式。內部的三個模塊:電壓基準、電壓緩沖、模擬輸入,可在不同開關模式下實現不同

的選擇,具體的實現形式和工作模式見表 1 及模式說明圖例。

如有需求請聯系——三亞微科技 王子文(16620966594)

如有需求請聯系——三亞微科技 王子文(16620966594)

睡眠模式

通過設置引腳 STBY 為邏輯高電平且時鐘保持在低電平,MS9280 進入睡眠模式。在這個模

式下,典型的功耗約 4mW。芯片在 STBY 變成低電平后,約 400ns 后進入正常模式。

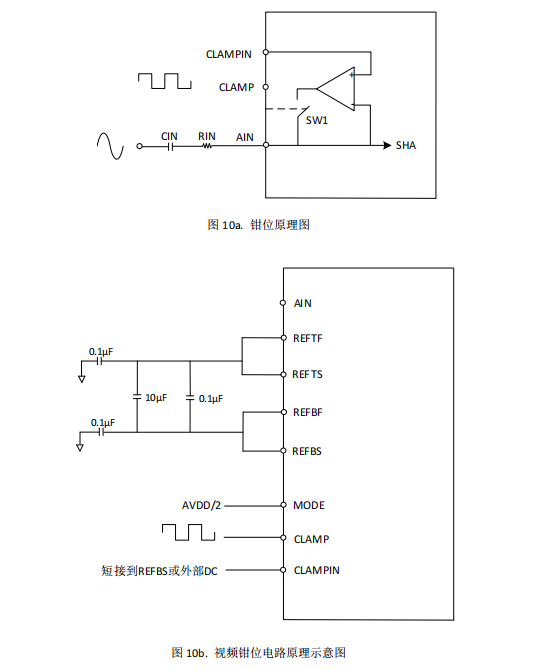

鉗位功能

為實現交流耦合輸入信號或視頻信號直流恢復的功能,MS9280 內部集成鉗位功能電路。圖

10 顯示內部鉗位電路和鉗位工作需要的外部控制信號。為了保證鉗位使能,應用邏輯高電平于

引腳 CLAMP。這將關閉開關 SW1。內部的鉗位放大器工作在緩沖器模式,引腳 CAMPLIN 的電壓

鉗位 AIN 輸入的直流電壓。獲得期望的鉗位電壓后,開關 SW1 由于引腳 CLAMP 變成邏輯低電平

而打開。在忽略由于輸入偏置電流引起的電壓變化外,輸入電容保持鉗位的直流電壓值,直到下

一個鉗位間隔到來。為保證內部鉗位放大器的閉環穩定性,推薦輸入電阻的最小值為 10Ω。

引腳 CLAMPIN 允許的電壓范圍取決于內部鉗位放大器的工作限制,推薦值在 0.5V ? 2.5V 之

間。

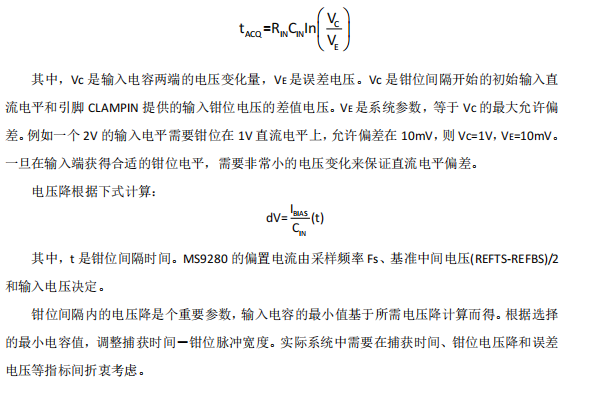

輸入電容大小根據在鉗位間隔內輸入電壓 AIN 允許的足夠捕獲時間和鉗位間隔之間的最小

電壓降來確定。具體來說,開關關閉后的捕獲時間由下式給出:

模擬輸入的驅動電路

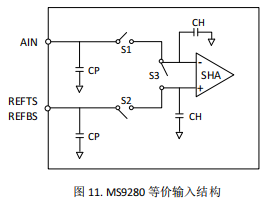

圖 11 說明等價的模擬輸入電路,MS9280 內部集成了采樣保持放大器。在時鐘低電平輸入

時,開關 1 和 2 閉合,開關 3 斷開。輸入模擬信號對采樣電容 CH 進行充電。當時鐘由低電平轉

變成高電平時,開關 1 和 2 斷開,采樣保持電路進入保持模式,開關 3 關閉,運放的輸出等于

采樣電容儲存的電壓。當時鐘由高電平轉變成低電平時,開關 3 首先斷開,開關 1 和 2 然后閉

合,采樣保持放大器進入跟蹤模式。

輸入采樣保持電路的結構對模擬信號輸入驅動能力有一定的要求。引腳電容 CP 和保持電容

CH 一般小于 5pF。輸入信號源必須能夠在半個時鐘周期內,把這些電容充電或放電到 10bit 精度

所需要的電壓值。當采樣保持放大器進入跟蹤模式時,輸入信號源必須對保持電容 CH 充電或放

電,從上一周期儲存的電壓到一個新的電壓。最壞情況下,輸入信號源提供充電電流在半個時鐘

周期內,通過開關 1 導通電阻 Ron 是采樣電容發生最大輸入信號峰值的轉變。這情況等效于驅

動一個低輸入阻抗電路。另一個情況,當輸入信號源電壓等于前一時刻儲存的電壓時,保持電容

不需要輸入電流,而且等價輸入阻抗非常高。

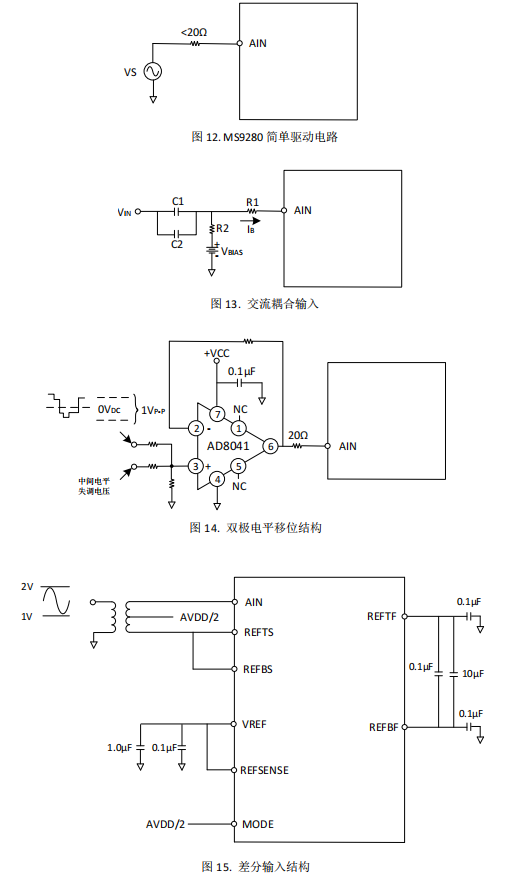

在輸入信號源和 AIN 引腳之間加入串聯電阻,可以減少對信號源驅動能力的要求,如圖 12

所示。某些特殊應用的帶寬限制了串聯電阻的大小。為了保證系統的性能指標,電阻限制在 20Ω

以內。對于信號帶寬小于奈奎斯特頻率的應用,用戶可以適當增加電阻大小。另外加入一個對地

的并聯電容,可以減小交流負載阻抗,電容的大小需要根據信號內阻和需要的信號帶寬來選擇。

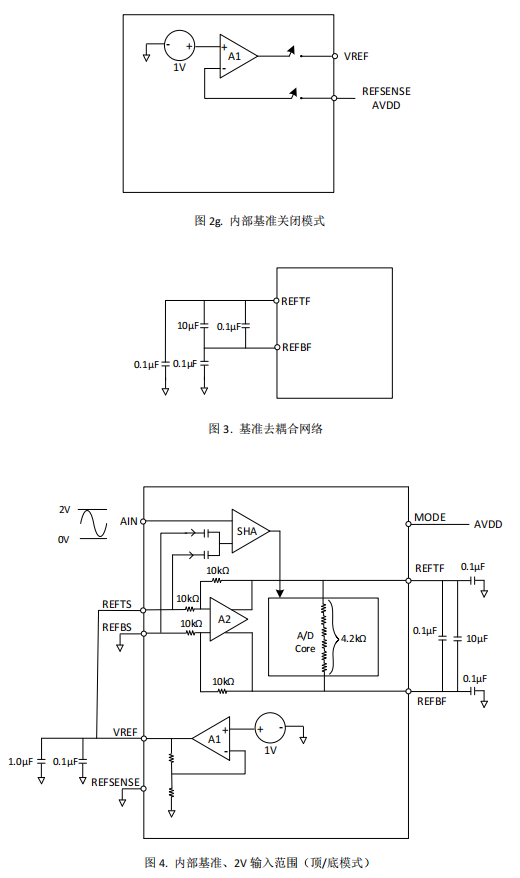

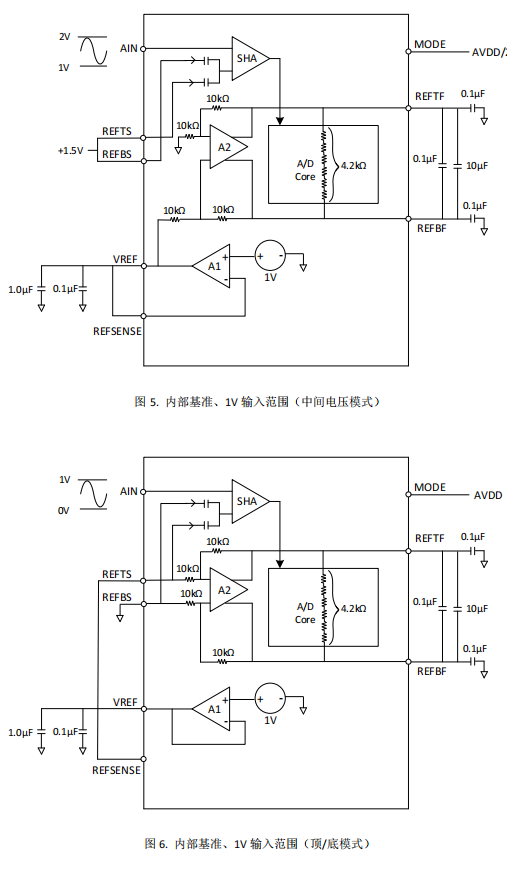

MS9280 的信號輸入范圍是基準電壓的函數。對于輸入范圍的選擇,根據基準部分中內部基

準和外部基準的不同編程來選擇確定。

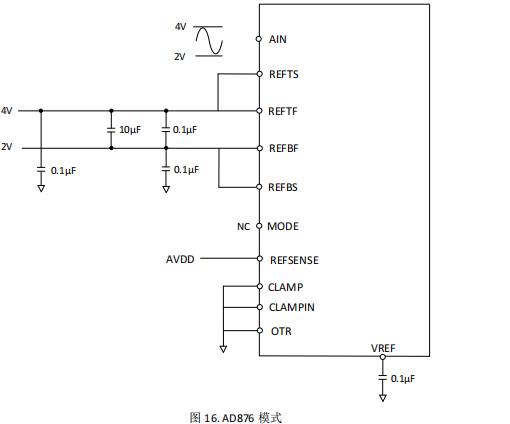

在許多應用中,尤其是單電源工作,交流耦合提供了一種方便的方法,在合適的量化范圍內,

偏置模擬輸入信號。圖 13 說明了交流耦合模擬輸入信號的典型結構。這種結構的高通-3dB 角頻

率是非常重要的考慮參數。 f =1/(2*pi*R2*C ) -3dB EQ ,其中 CEQ 是 C1 和 C2 的并聯。

選擇電阻值需要特別考慮,交流耦合電容在輸入端集成開關傳輸特性,導致節點直流偏置電

流流入輸入。偏置電流的大小隨著輸入信號幅度偏離中間參考電壓值的大小和采樣頻率的增加而

增加。當輸入信號等于基準中間值時,輸入偏置電流最小,同時導致輸入失調誤差 (R1+R2)*IB 。

如果需要補償這個誤差,考慮減小 R2 或者調整 VBIAS 以滿足需要的失調要求。

在系統應用中,必須使用直流耦合。通過運放,改變參考地的信號直流電平,以實現輸入信

號在合適的量化范圍內。圖 14 顯示 AD8041 同向模式的電路結構。

MS9280 可以采用差分輸入的信號模式。這種結構需要通過短接 REFTS 和 REFBS 兩個輸入端

作為一個差分輸入端。圖 15 顯示 1V P-P 信號的差分輸入模式。

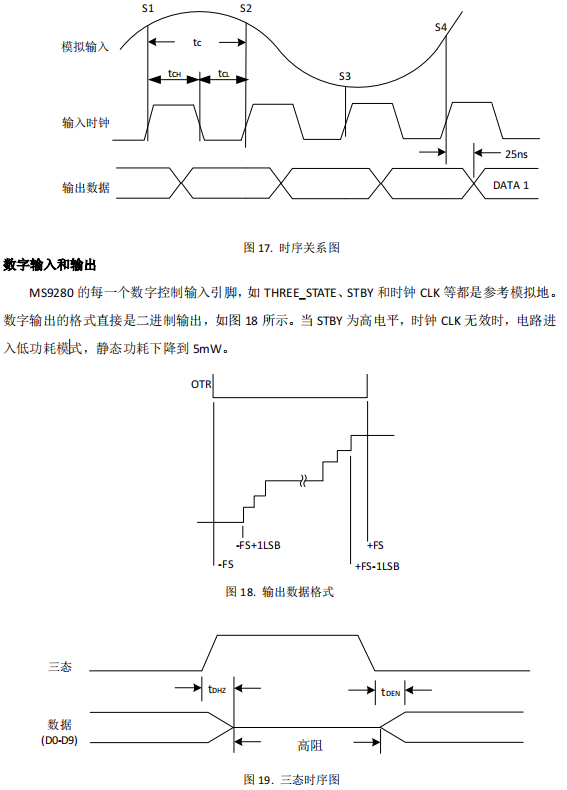

AD876-8 工作模式

MS9280 可以通過引腳配置,替代 AD876-8 系列,從而降低原來使用 AD876-8 的系統功耗。

圖 16 說明了 MS9280 替代 AD876-8 的引腳配置。通過 REFSENSE 接地,MODE 引腳懸空,CLAMP

引腳接地,使用外部基準模式就可以替代原來的 AD876-8.

如有需求請聯系——三亞微科技 王子文(16620966594)

時鐘輸入

MS9280 時鐘輸入通過內部的反向器緩沖器給電路提供時鐘,且內部反向器由 AVDD 引腳供

電。這種結構保證了時鐘滿足+5V 或+3.3V CMOS 邏輯輸入信號,輸入閾值電壓在 AVDD/2。

MS9280 的流水線結構既工作在時鐘的上升沿又工作在下降沿。為了最小化占空比的偏差,

推薦采樣高速或先進 CMOS 邏輯時鐘(HC/HCT, AC/ACT)。CMOS 邏輯提供對稱的電壓閾值電平和足

夠的上升和下降時間,以滿足 35MSPS 的采樣速率。MS9280 設計的最高時鐘頻率位 35MHz,更

高的時鐘頻率將要弱化系統的性能指標。選擇更低的時鐘頻率可以提高系統的性能指標。輸出緩

沖的功率消耗主要正比于時鐘頻率,更低的時鐘頻率可以降低功耗。

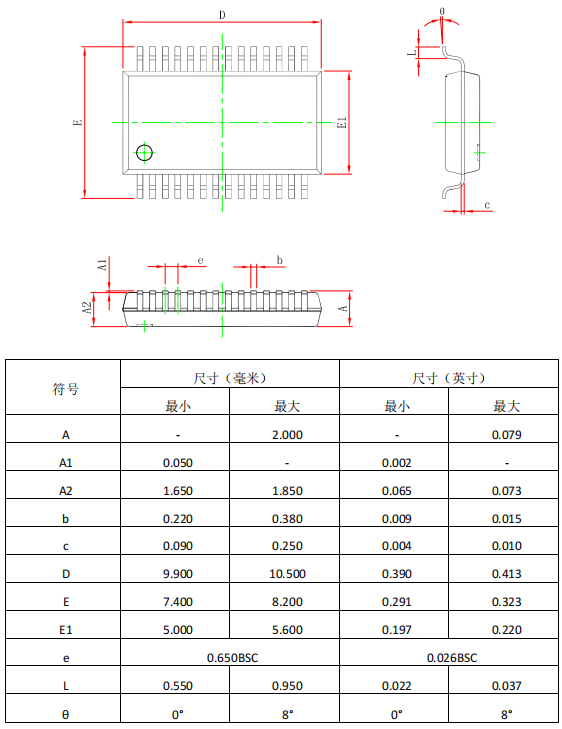

封裝外形圖

SSOP28

——愛研究芯片的小王

審核編輯 黃宇

-

模數轉換器

+關注

關注

26文章

3200瀏覽量

126810 -

10bit

+關注

關注

0文章

3瀏覽量

2684

發布評論請先 登錄

相關推薦

MS5110S——16-bit 內置基準模數轉換器

MS5175——16-Bit、四輸入、內置基準模數轉換器

MS1112——16-bit 多輸入內置基準模數轉換器

ADC1175-50低功耗、50 MSPS模數轉換器數據表

THS10082低功耗、10位、8 msps模數轉換器(ADC)數據表

THS1007低功耗、10位、6 msps模數轉換器(ADC)數據表

ADS5463-SP 12位500 MSPS模數轉換器數據表

ADS7884一款10位、3 MSPS模數轉換器(ADC)數據表

TLV5535一款8位35 MSPS高速模數轉換器數據表

ADS5424 14位、105 MSPS模數轉換器(ADC)數據表

MS9280——10bit、35MSPS 模數轉換器

MS9280——10bit、35MSPS 模數轉換器

評論