一、前言

本文將介紹Vivado進行綜合,以及布局布線的內部流程,熟悉該流程后結合Settings中對應的配置選項,對于時序收斂調試將更具有針對性。

二、Implementation(實現)

實現流程由一系列的子流程組成,包括:Design Initialization設計初始化、Opt Design設計優化、Power Opt Design功率優化【可選項】、Place Design布局、Post-Place Power Opt Design布局后期設計功率優化【可選項】、Post-Place Phys Opt Design布局后期設計物理優化【可選】、Route Design布線、Post-Route Phys Opt Design布線后期設計物理優化【可選項】、Write Bitstream寫入比特流、Write Device Image寫入器件備份文件。

下面將重點介紹和布局布線相關的流程,其他簡略帶過。

Opt Design:對邏輯設計進行優化,使其與器件匹配

Power Opt Design: 對設計的單元進行優化從而降低功耗

Place Design:將設計布局到器件上

Post-Place Power Opt Design:在布局后進行進一步的優化來降低功耗

Post-Place Phys Opt Design:對時序違例的路徑進行優化

Route Design:對于布局后的設計進行布線

Post-Route Phys Opt Design:通過實際的布線延時值進行邏輯,布局,布線優化

Write Bitstream :生成器件配置的比特流

Write Device Image:生成器件備份文件

三、布局布線

3.1 Placement(布局)

布局通俗理解就是布局器會將來自網表的單元布局到芯片的確定位置,可細分為7個子流程。

3.1.1 設計布局優化

布局優化對象主要是時序違例路徑較大的單元,線長較大的部分以及通過監控引腳密度來提前進行布局分散從而避免后期布線擁塞

3.1.2 設計規則檢查

開始布局前,會先進行設計規則檢測DRC,DRC有兩類,一類是用戶在report_drc中設置的規則,另一類是軟件自定義的規則,如存儲器IP單元沒有進行位置約束或者是IO banks和IO標準沖突

3.1.3 布局時鐘單元和I/O

完成DRC后,布局器會優先布局時鐘單元和I/O單元。時鐘和I/O一般是同時進行布局的,因為在指定器件中,布局規則中二者關聯性很強。對于Ultrascale/Ultrascale+系列的器件,布局器也布局時鐘軌道,對時鐘預布線。如果觸發器會合并進入到I/O邏輯單元,也在這階段進行布局,否則布局失敗時,會有嚴重告警打印。

在這一階段,布局器要完成的布局對象有I/O端口和與之關聯的邏輯,全局時鐘緩沖器,時鐘管理單元(MMCMS和PLL),GT單元。同時,布局器也要考慮設置的位置約束屬性和區域約束屬性。

當時鐘或I/O布局失敗時,布局報告會打印相關錯誤,對錯誤進行簡單描述。通常,布局失敗的原因有以下幾點

a. 因為約束沖突導致的時鐘樹問題

b.過于復雜的時鐘樹問題

d.資源不足

f.違反了I/O bank的一些規則

3.1.4全局布局,詳細布局和后期布局優化

完成時鐘和I/O布局后,依次是全局布局,詳細布局,后期布局優化。

3.1.4.1 全局布局

全局布局分為布局資源規劃(floorplanning)和物理綜合。布局資源在I/O和時鐘布局后被分成很多小的相關聯的邏輯,Pblock約束是需要考慮的,是硬性要求。

在布局資源規劃后是物理綜合,在基于布局資源規劃基礎上,布局器將對網表運行不同的物理優化策略進行設計的初始化布局。例如,基于復制的扇出,復制的驅動源將和load放一起,因為初始位置是確定的。優化也會考慮內部的參數設置以及時序相關的。只有時序有所改善,優化才會真正進行。

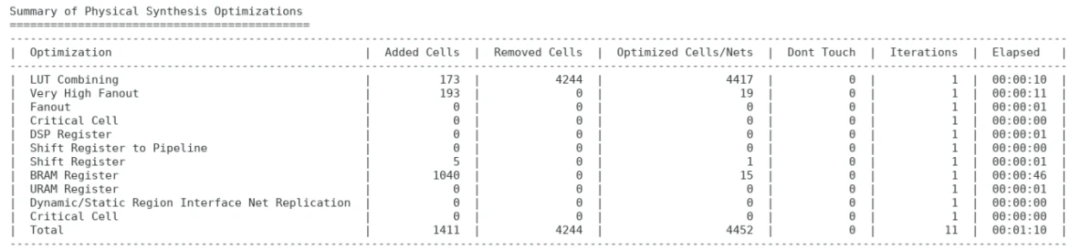

在物理綜合階段,下圖是優化概要示例。

LUT的分解與重組:如果LUTs有SOFT_HLUTNM屬性并且LUT分解和重組能改善時序,布局器將進行該操作

基于屬性的重定時:用戶可以通過設置一個屬性在寄存器或LUT上實行重定時,對于時序起點和終點有足夠距離的關鍵路徑來說作用較明顯。在PSIP有兩個控制重定時的屬性:PSIP_RETIMING_BACKWARD,PSIP_RETIMING_FORWARD,值都設置為true時表示執行后向重定時和前向重定時。

同時,在以下場景下設置重定時屬性將不會起作用

a.移動的邏輯經過了一些大塊單元,如BRAM,URAM,DSP

b. pack到了I/O上的寄存器

c.路徑的起點與終點時鐘不同

d.路徑上含有時序例化的設置

e.含有阻止優化的屬性,如DONT_TOUCH等

高扇出優化:高扇出通過復制寄存器來驅動高扇出nets(扇出大于1000,slack值小于2ns)

關鍵單元優化:在失敗路徑上通過復制單元來進行優化,如果已布局的單元的load距離太遠,該單元將會被賦值然后放置到距離load更近的位置。通常在一些塊狀RAM,URAM,大量的DSP布局較為分散時,該優化使用較多

扇出優化:對于設置了MAX_FANOUT的nets,當nets的實際扇出數量大于設置的MAX_FANOUT時,將會進行優化。用戶可以通過添加FORCE_MAX_FANOUT到該nets上,從而強制對驅動該nets的寄存器或LUT進行復制,并且此處提到的load都是實際物理連接的loads,不是邏輯loads。

DSP寄存器優化:DSP寄存器優化是指將寄存器從DSP中移出到邏輯組中,或者從邏輯單元移入到DSP中,從而改善關鍵路徑的時延

移位寄存器流水線優化:操作是將有固定長度的移位寄存器改成動態調整寄存器流水線,然后再布局流水線流水線來改善時序,動態的SRLs不支持該優化

移位寄存器優化:該優化是針對在移位寄存器單元和其他邏輯單元間存在時序違例的路徑

塊狀RAM寄存器優化:塊狀RAM寄存器優化是指將寄存器從塊狀RAM中移出到邏輯組中,或者從邏輯單元移入到塊狀RAM中,從而改善關鍵路徑的時延

動態/靜態區域接口網線復制:在DFX流程中,將靜態設計復制到可重配的模塊便捷路徑上

等價驅動源重布線優化:將邏輯上相等的驅動源進行load的重新分配,減少布線的重復,也能為驅動源和負載提供更優的位置。這個可以減少資源使用和布線擁塞

3.1.4.2 詳細布局

通過詳細布局,可以讓設計從初始化的全局布局成為全部布局。通常是先對大塊單元,如多列的URAM,塊狀RAM,DSP塊組布局,然后是LUTRAM組,用戶在XDC中定義的更小一些的大塊。邏輯單元布局時是不斷迭代,以保證線長,時序最優,不擁塞。在CLBs的LUT-FF對和CLB中的寄存器必須共用普通的控制集

3.1.4.3后期布局優化

在所有的邏輯單元位置都確定后,后期布局優化將進行改善時序和擁塞的最后一步,包括改善關鍵路徑的布局,BUFG復制,可選的BUFG插入。在BUFG復制階段,BUFG驅動的nets跨多個SLRs時,每個SLRs都會分配一個BUFG。在布局或布線沖突,以及有阻止復制或時鐘降級的約束時,該優化將不會進行。

在BUFG插入階段,布局器將高扇出的net布線到全局布線路徑上,從而釋放普通布線資源,驅動控制信號的高扇出nets如果slack值大于1ns將會優化。

3.2Routing(布線)

在完成布局后,布線器將會進行布線。布線器提供了2個布線選項,對整個設計布線或對單個的引腳或nets布線。當對整個設計布線時,流程是時序驅動的,在時序約束的基礎上,使用自動的時序計算規則。當對單個nets或引腳布線時,有迭代布線和自動延時兩種模式。

布線的子流程包括:設計規則檢查DRC,布線優先級。

3.2.1 設計規則檢查

設計規則檢查主要有兩類檢查,第一類是用戶從report_drc中設置的規則,第二類是vivado軟件內部的檢查規則

3.2.2 布線優先級

布線器首先布線全局資源,如時鐘,復位,I/O和其他降級的資源。在布線器內部有默認的優先級,然后根據時序重要性對數據信號布線。

-

布線

+關注

關注

9文章

782瀏覽量

84764 -

布局

+關注

關注

5文章

272瀏覽量

25228 -

Vivado

+關注

關注

19文章

821瀏覽量

67837

原文標題:Vivado之實現(布局布線)流程淺析

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Vivado下顯示指定路徑時序報告的流程

PCB的布局與布線介紹

如何實現良好的電路板布局布線

用 TCL 定制 Vivado 設計實現流程

pcb布線心得(流程詳解、元件布局布線與EMC)

Vivado設計之Tcl定制化的實現流程

Vivado使用誤區與進階——在Vivado中實現ECO功能

評論