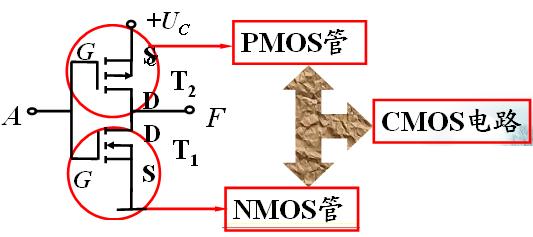

當今的電子設計領域,CMOS邏輯IC因其低功耗、高集成度和良好的噪聲抑制能力而得到廣泛應用。然而,要充分發揮CMOS邏輯IC的性能優勢,確保系統的穩定可靠運行,必須嚴格遵守一系列使用注意事項。從本期芝識課堂起,芝子將向大家奉上一份詳細的設計指南,幫助大家更好地避免潛在的設計陷阱和故障。

對于未使用輸入引腳的處理

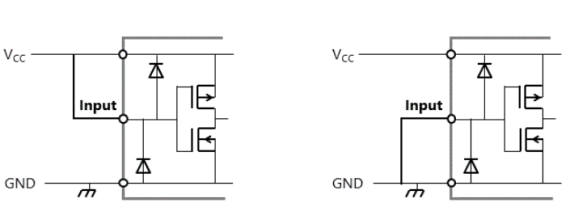

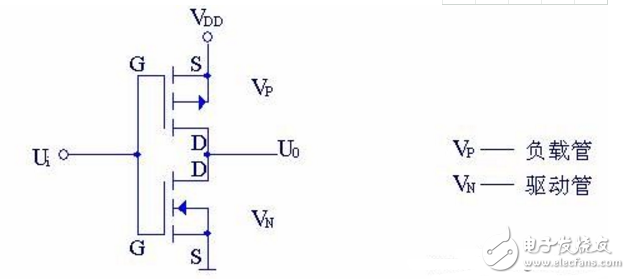

在設計和使用CMOS邏輯IC時,正確處理未使用的輸入引腳是確保系統穩定性和可靠性的關鍵步驟。通常而言,所有未使用的輸入端都應連接到VCC或GND。

連接到VCC或GND的CMOS邏輯IC的未使用輸入端

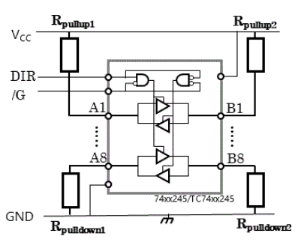

對于可配置為輸出端的雙向總線緩沖器來說,任何引腳(如總線引腳)應通過上拉電阻器連接到VCC或通過下拉電阻器連接到GND。同時,建議將緩沖器兩端上拉或下拉至相同電位,以避免不必要的電流流動。但是,請保持總線引腳的輸入引腳保持為打開狀態。

雙向總線緩沖器的未使用的雙向引腳上拉至VCC或下拉至GND

即使采用典型的CMOS邏輯IC,仍會在電源接通瞬間,因寄生電容而產生短暫的浪涌電流。雖然這種電流通常較小(幾毫安量級),但在某些敏感應用中仍需注意。通過將未使用的輸入引腳連接到VCC或GND,可以有效降低這種浪涌電流的影響,提高系統可靠性。

另外,由于CMOS邏輯IC具有非常高的輸入阻抗,任何開放的輸入端都可能由于周圍電場的影響而導致錯誤的輸出值。此外,直通電流可能會在VCC和GND的中點流動,從而導致電流增加,這可能會導致器件損壞。除非數據手冊中另有說明,否則務必將這些注意事項應用至所有不具有總線保持能力的輸入端。

輸入上升和下降時間規范

在數據表中,針對通用CMOS邏輯集成電路(IC)明確界定了其輸入信號的上升與下降時間標準,這些標準旨在確保IC在預定的工作環境下能夠穩定且高效地執行其功能。遵循這些時間規范對于防止因輸出信號振蕩等不利現象導致的系統故障至關重要。

當向CMOS邏輯IC的輸入端施加緩慢的上升或下降信時,切換過程中可能會產生顯著的電流峰值。這些峰值電流不僅可能引發電源電壓(VCC)和地電位(GND)的瞬態波動(俗稱“彈跳”),還可能進一步導致輸出信號的振蕩或功能異常。

為應對這一挑戰,可使用帶有施密特觸發器輸入的IC來緩慢更改輸入。但是如果輸入變化過慢,即使帶有施密特觸發器輸入的IC仍可能無法抑制電源或信號線上的噪聲,從而導致輸出振蕩或不穩定。

下表顯示了每個系列中典型IC的上升和下降時間。

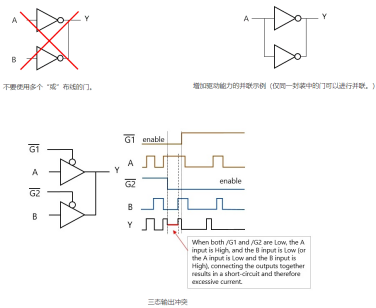

通用CMOS邏輯IC的多個輸出

發生沖突(短路)

與二極管不同,典型CMOS邏輯IC的輸出不能進行線或運算,除非具有三態輸出。即使是具有三態輸出的CMOS邏輯IC,如果同時啟用,也可能會有非預期電流流動,導致IC劣化。所以在創建電路設計時,請確保在任何既定時間都不會啟用多個輸出。此外,如果所有的CMOS邏輯IC都被禁用(即處于高組態),而沒有被上拉到VCC或下拉到GND,那么不具有總線保持功能的CMOS邏輯IC的輸出就會變得不穩定。

僅同一封裝中的門才可以進行線與運算,以增加驅動能力(即輸出電流)。但是,建議使用高驅動IC(IO為±24 mA)。

正確使用CMOS邏輯IC不僅需要理解其電氣特性,還需要關注實際應用中的細節。通過本文提供的指南,設計師可以預防常見的設計錯誤,提高電路的整體性能和可靠性。在后續文章中,們將繼續探討如何優化CMOS邏輯IC的性能和電容連接技巧,敬請期待。

關于東芝電子元件及存儲裝置株式會社

東芝電子元件及存儲裝置株式會社是先進的半導體和存儲解決方案的領先供應商,公司累積了半個多世紀的經驗和創新,為客戶和合作伙伴提供分立半導體、系統LSI和HDD領域的杰出解決方案。

東芝電子元件及存儲裝置株式會社十分注重與客戶的密切協作,旨在促進價值共創,共同開拓新市場,期待為世界各地的人們建設更美好的未來并做出貢獻。

-

CMOS

+關注

關注

58文章

6056瀏覽量

239350 -

噪聲

+關注

關注

13文章

1141瀏覽量

48353 -

引腳

+關注

關注

16文章

1831瀏覽量

53429 -

GND

+關注

關注

2文章

545瀏覽量

40047 -

邏輯IC

+關注

關注

0文章

29瀏覽量

6748

原文標題:芝識課堂【CMOS邏輯IC的使用注意事項】—深入電子設計,需要這份指南(一)

文章出處:【微信號:toshiba_semicon,微信公眾號:東芝半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

CMOS邏輯IC使用時如何應對電路中的危害、亞穩態、鎖存以及ESD—東芝半導體帶你深入電子設計

如何利用CMOS模擬開關實現平衡混頻器?有什么注意事項?

膽機使用的注意事項

CMOS集成邏輯門電路的使用注意事項

評論