原創 Lee 問芯

引領集成電路行業數十年高速發展的“摩爾定律”如今日趨放緩。隨著芯片工藝制程節點向 3nm、2nm 演進,量子隧穿效應、短溝道效應等帶來的漏電、發熱等問題愈發嚴重,在有限的面積內增加更多晶體管變得愈發困難,成本大幅攀升,業界不得不探索其他技術路線。

作為當今“后摩爾時代”的芯片設計技術,Chiplet(芯粒、小芯片)應運而生。與傳統 SoC 芯片設計方法不同,Chiplet 能讓不同功能模塊采用最適合其性能需求的工藝節點制造,從而優化成本效益比,提高設計靈活性,是一種更為經濟高效的解決方案。

圍繞 Chiplet 技術,標準化有助于更快形成設計生態,進一步推動 chiplet 技術廣泛應用,并推動產業鏈上下游企業協作,加速產品研發周期,降低研發成本。

近期,「問芯」專訪了國內和 IEEE Chiplet 標準制訂牽頭人、中國科學院計算技術研究所郝沁汾研究員,訪談中他圍繞 Chiplet 技術的發展現狀、未來趨勢,以及 Chiplet 技術標準制訂等多個方面進行了分享和解讀。

圖|中國科學院計算技術研究所郝沁汾研究員(來源:受訪者)

2001 年,郝沁汾博士畢業于中國科學院計算技術研究所計算機系統結構專業,從業 20 余年間他先后就職于聯想、北京航空航天大學、華為等,專注于高性能服務器、高端 SMP 服務器、高速緩存一致性互連芯片、CPU 芯片的設計和研究工作。此外,他還是中國和 IEEE Chiplet 技術標準的主要發起人和起草人,曾參與過多項國家級科研項目,在國內外學術會議及核心刊物上發表學術文章 50 余篇,申請國內外發明專利 100 余項。

目前,郝沁汾是中國科學院計算技術研究所研究員、博士生導師,現階段的研究方向主要是圍繞基于 Chiplet 架構的處理器、基于芯片級光互連的計算機系統結構等。

“Chiplet 作為新的設計方法學可加速芯片設計”

Chiplet 的設計理念最早可追溯至上世紀 70 年代的“多芯片模組”概念,近幾年 Chiplet 技術突然升溫,在郝沁汾看來,“任何一個先進技術概念誕生之初都存在時代局限性,當時技術基礎可能并不完備,比如缺乏應用需求、標準、功能芯粒、EDA 工具等,所以長期停留在概念層面。”

之所以 Chiplet 在近幾年變得業界矚目,他認為有兩方面的因素:其一,先進工藝制程達到物理極限;其二,大公司希望提升良率,中小公司希望有更好的方法設計芯片,或者降低芯片設計的門檻,尤其在面向業務的芯片設計方面。

具體而言,“首先,是先進工藝制程發展面臨瓶頸,晶體管密度達到物理極限,因此需要尋求其他解決方案,而 Chiplet 技術為有效技術之一,本質是通過擴展面積從而實現性能繼續提升。其次,即使不采用先進工藝,如今的芯片面積越來越大,對良率造成影響,Chiplet 技術依然可以用來提升大算力芯片的良率,而由于面積較小,IoT 等芯片對良率不敏感,但種類繁多,IoT 芯片設計公司更側重芯片設計效率,多方面因素讓 Chiplet 變得非常熱門。”郝沁汾解釋道。

與此同時,就國內而言,先進工藝發展與國際層面存在差距,在工藝相對落后的情況下,通過 Chiplet 開發芯片也是一種切實可行的策略。“采用 Chiplet 方式開發的芯片,在功能和性能方面接近采用先進工藝開發的芯片,或許芯片的功耗、面積會稍大,但在一些對功耗、面積不敏感的場景是較好的解決方案。”他表示。

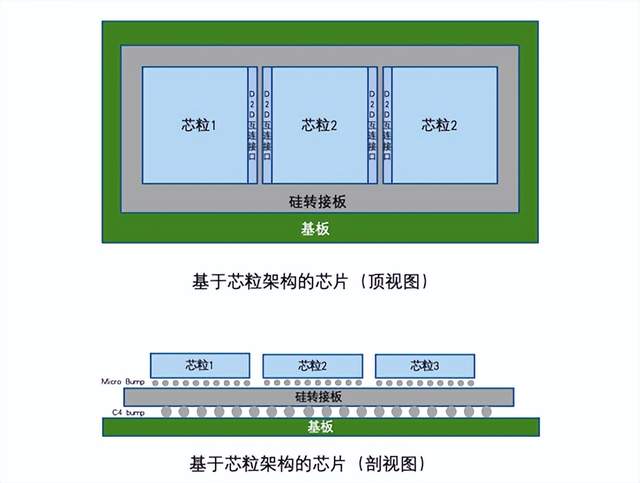

圖|Chiplet 技術示意(來源:受訪者)

在郝沁汾看來,Chiplet 技術的發展大致可劃分為兩個階段:Chiplet 1.0 階段(此前 3-4 年間)和 Chiplet 2.0 階段(目前及未來 10 年間)。

“在 1.0 階段,Chiplet 技術的開發主要集中在一些大型芯片企業(比如英特爾、AMD 等),其核心訴求是為了解決芯片良率問題。”他指出。隨著 SoC 面積的增大,如果繼續沿用傳統單芯片的設計方案,那么芯片面積會越來越大,良率會逐漸下降,進而導致成本增加,所以大型芯片企業采用 Chiplet 的設計方式來解決生產良率問題。

“在 2.0 階段,則主要是為了解決芯片設計效率問題。”他表示。設計大芯片的企業關心良率,而設計中小芯片的公司(如 IoT 芯片設計企業)側重的是芯片開發的門檻問題,即如何找到一種更高效的方法去設計開發芯片,這是中小芯片設計公司面臨的主要訴求。

不同于傳統單芯片的設計模式,Chiplet 將“大芯片拆分為小芯片”進行生產并集成封裝。“Chiplet 的本質其實是一種‘分開設計’的模式,小公司若要加速芯片的設計效率,采用 Chiplet 方式能起到較好的效果。”郝沁汾說道。

例如,整顆芯片上包含多個小芯片,小公司可以完成其中的一個業務邏輯芯片,其他的諸如功能芯片則可以從“芯粒庫”(包含大量的已經設計好的小芯片)中挑選,然后將所有小芯片通過先進封裝技術進行組裝,如此一來,能大幅降低芯片開發難度,進而加速芯片整體設計效率。

但就現階段而言,Chiplet 技術發展也面臨一些挑戰。“Chiplet 技術最大的挑戰主要在 2.0 階段。一方面,中小型芯片設計公司的訴求并沒有得到業界充分關注,而大公司采用 Chiplet 設計芯片其實不需要技術標準,因為自己設計的芯粒進行對接并不需要標準,比如英特爾并沒有通過 UCIe 協議和任何第三方芯粒對接,UCIe 更多的是作為開放給業界的一種芯粒接口標準,但由于設計極其復雜(如狀態機等),并不一定適合所有的芯片種類。因此,究竟誰該來用‘Chiplet 技術標準’,我覺得現階段是存在誤區的。”郝沁汾指出。

“另一方面,目前‘芯粒庫’依然缺乏功能芯粒,只有在具備大量現成的功能芯粒的前提下,Chiplet 2.0 階段才能順利推進。”他說道。

市場層面,郝沁汾表示,“很大程度上,Chiplet 可以說是一種不得不用的設計方法,幾乎所有的芯片相關公司開發下一代芯片都有嘗試和探索這種方法,因此,其市場規模將會逐步增長。”

“需要注意的是,其實 Chiplet 并不是脫離于當前集成電路行業的一個新的獨立市場,而是基于現有集成電路市場上的一種新的設計方法學,即在原有集成電路產業上疊加的一個技術,而疊加了 Chiplet 以后的集成電路行業也就變成 Chiplet 的市場。”他說道。

“終極目標是‘讓天下沒有難設計的芯片’”

2021 年 5 月,中國計算機互連技術聯盟(CCITA)在中國電子工業標準化技術協會立項了 Chiplet 技術標準《小芯片接口總線技術要求》,作為中國 Chiplet 技術標準的主要發起人和起草人,郝沁汾坦言,“國內 Chiplet 標準制定的挑戰性很大,而且后期面臨的挑戰還會越來越大。比如,在 Chiplet 標準制定過程中我也曾聽到一些諸如‘標準的制定應當由大公司來牽頭,而不是科研院所’等反對的聲音。”

他繼續說道,“大公司希望通過 Chiplet 提升良率,然而大公司其實并不需要標準,它們有足夠的實力自主開發基于 Chiplet 架構的芯片,而這也是我們在起草和制定國內標準過程中才逐漸認識到的問題,真正需要 Chiplet 標準幫助降低芯片設計門檻的是小型芯片設計公司,以及希望通過 Chiplet 方式去充分利用資源的中等規模芯片設計公司,然而這些中小公司可能并不太受到重視。”

郝沁汾認為,“放眼全球,半導體行業的技術創新很大一部分來自中小公司,相較之下大公司的技術創新有所局限,更多的是為了尋求穩健。所以從這個角度出發,若讓大公司來牽頭 Chiplet 標準的制定,那將會是偏保守的,為‘求穩’而不愿采納創新技術。”

“既然我們作為科研院所來牽頭 Chiplet 標準的制定,那就需要融入一些對創新和未來的考量,要解決的也并不單純是當下的問題,重點是如何更好的服務于中小企業,終極目標是實現‘讓天下沒有難做的芯片’,并以這種方式促成國內芯片設計群體的崛起。我覺得,這是我們科研院所能夠做出的貢獻。”郝沁汾說道。

圖|Chiplet 標準研討會(來源:受訪者)

除了國內標準,郝沁汾還牽頭了國際 Chiplet 標準制定。“畢竟技術無國界,圍繞技術本身我認為還需要有一個全球化的、開放的平臺進行交流,而 IEEE 是這樣的平臺。”郝沁汾說道。

據介紹,IEEE 的 Chiplet 標準(工作組編號 P3468)于今年 3 月立項,5 月在新加坡 2024 國際電路與系統研討會(ISCAS 2024)上正式啟動標準制定工作,工作組匯集了全球 170 余位業內專家,預計 2027 年完成標準制定。

談及國際標準與國內標準的區別,郝沁汾表示,“國內標準主要圍繞 Chiplet 接口電路對接的定義層面,而 IEEE 的 Chiplet 標準主要聚焦在接口電路的實現層面技術的標準化,并考慮兼容多協議。換句話說,從實現的層面上,是否可以盡可能的多去支持一些現有的 Chiplet 標準。通過一個標準物理電路的實現去支持多個標準,這是兩者的區別所在,而在為了實現這個目標的過程中,需要進行大量的技術創新,比如需要更寬頻率的 PLL,這也和現存的 Chiplet 標準主要是規格的制定有較大區別。”他指出。

據悉,11 月 26 日,中國計算機互連技術聯盟(CCITA)在無錫芯光互連技術研究院舉辦了由 40 余位專家參與的“構建芯粒庫,進軍 Chiplet 2.0 時代”技術研討會“,與會專家齊聚一堂,圍繞如何推動“芯粒庫”的建設紛紛建言。“若干年后再回顧,也許這一天會成為 Chiplet 2.0 時代的起點。”他說道。

制定國內 Chiplet 標準的意義重大,“國內 Chiplet 標準與英特爾牽頭的 UCIe 基本是同期發布的,但國外標準討論的過程中對國內企業有所限制,只有極少數企業能夠參與其中,并且也難以全程參與。”他表示。

在郝沁汾看來,大公司和中小公司存在的價值不同。“中小公司為創新主體,是創新的發起者,而大公司的作用更多的是穩健地把控某個領域,中小公司在一些領域發起創新挑戰,逐漸超越并慢慢成長為大公司。在中小公司成長過程中,我們制定的 Chiplet 標準若能起到助推作用,并通過這種方式幫助國內的集成設計群體崛起,那將是非常有價值的。”他總結道。

審核編輯 黃宇

-

芯片

+關注

關注

459文章

52145瀏覽量

435948 -

IEEE

+關注

關注

7文章

388瀏覽量

48018 -

芯粒

+關注

關注

0文章

62瀏覽量

243

發布評論請先 登錄

靈動微電子助力汽車芯片可靠性提升

瑞為技術牽頭制定的國家標準《信息技術 可擴展的生物特征識別數據交換格式 第1部分:框架》正式發布

華大九天牽頭制定車規級EDA團體標準

九聯科技參與起草的一項國家標準發布

PPEC為電力電子科研教學賦能,開啟教學科研新路徑

中國新的汽車GNSS技術標準:準備進行合規性測試

Chiplet技術有哪些優勢

Imec牽頭啟動汽車芯粒計劃

IMEC組建汽車Chiplet聯盟

博泰車聯網牽頭制定的國家標準和行業標準正式發布

評論