在半導(dǎo)體領(lǐng)域,微控制器(MCU)是一個(gè)很卷的賽道。為了能夠從眾多競(jìng)爭(zhēng)者中脫穎而出,MCU產(chǎn)品一直在不斷添加新“技能”,以適應(yīng)市場(chǎng)環(huán)境的新要求。因此,時(shí)至今日,如果你“打開(kāi)”一顆MCU,會(huì)發(fā)現(xiàn)其早已不再是一顆傳統(tǒng)意義上簡(jiǎn)單的計(jì)算和控制芯片,而是集成了CPU內(nèi)核以及豐富外設(shè)功能模塊的SoC。

尤其是在CPU內(nèi)核趨向同質(zhì)化的今天,想要在產(chǎn)品設(shè)計(jì)上實(shí)現(xiàn)差異化,MCU廠商更是要在CPU內(nèi)核之外的外設(shè)功能的集成上大做文章,讓自己的產(chǎn)品具有與眾不同的賣(mài)點(diǎn)。

“可以將哪類(lèi)外設(shè)功能集成到MCU中”,對(duì)于這個(gè)問(wèn)題,MCU廠商已經(jīng)進(jìn)行了諸多嘗試:存儲(chǔ)器、定時(shí)器、模擬外設(shè)、通信接口,甚至是射頻收發(fā)器……不一而足。今天,Microchip更是腦洞大開(kāi),給出了一個(gè)新思路——將一個(gè)“微型FPGA”集成到MCU中!

在8位MCU中集成可編程邏輯

電子工程師都知道,在相當(dāng)長(zhǎng)的時(shí)間里,MCU和以FPGA為代表的可編程邏輯,是兩個(gè)特性迥異的開(kāi)發(fā)平臺(tái):前者是在通用CPU架構(gòu)的基礎(chǔ)上,通過(guò)軟件編程去滿足不同應(yīng)用的設(shè)計(jì)要求,具有較高的靈活性和可擴(kuò)展性,不過(guò)代價(jià)就是在性能和功耗上有所折中;而后者由于具有硬件可編程特性,開(kāi)發(fā)者可以根據(jù)應(yīng)用“定制”所需的硬件電路,在性能和功耗上自然更勝一籌,不過(guò)開(kāi)發(fā)門(mén)檻相對(duì)較高。

之前也有?商將兩者結(jié)合在?起,開(kāi)發(fā)出兼具靈活性和?能效的異構(gòu)平臺(tái),不過(guò)它們?都定位于中?端的產(chǎn)品。將可編程邏輯與8位MCU整合在?起的嘗試,并不多?。?Microchip正是找到了這個(gè)獨(dú)特的市場(chǎng)切?點(diǎn),推出了PIC16F13145 系列MCU。

具體來(lái)講,與傳統(tǒng)的8位MCU不同,PIC16F13145系列的外設(shè)中,除了ADC、DAC、?較器和定時(shí)器等這些“常規(guī)”配置,還有?個(gè)特別的可配置邏輯塊(CLB)模塊。

CLB由32個(gè)基本邏輯元件(BLE)陣列(每個(gè)BLE都能夠模擬AND / OR / NAND / NOR?)以及緩沖器/反相緩沖器、D觸發(fā)器、JK觸發(fā)器、多路復(fù)?器或四輸?LUT構(gòu)成。

這意味著,開(kāi)發(fā)者可以利?CLB直接在MCU內(nèi)創(chuàng)建基于硬件的定制組合邏輯功能,實(shí)現(xiàn)??想要的硬件電路,?不受通?MCU固定硬件架構(gòu)的限制,就好像在MCU中添加了?個(gè)“微型FPGA”。

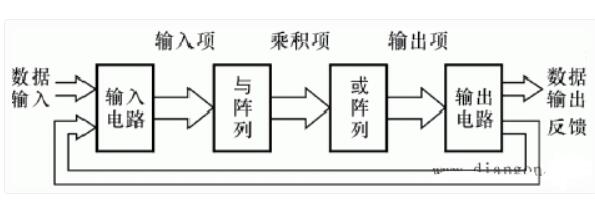

圖:可配置邏輯塊(CLB)架構(gòu)

(圖源:Microchip)

從架構(gòu)上看,CLB與FPGA的可編程邏輯結(jié)構(gòu)很相似。構(gòu)成CLB的每個(gè)BLE由?個(gè)4輸?LUT(Lookup-Table, 查找表)和?個(gè)D觸發(fā)器組成。CLB的輸入接口提供了16個(gè)輸入的選擇鎖存器,每個(gè)選擇鎖存器可以選擇最多40種不同的信號(hào)之一的信號(hào)來(lái)作為輸入,這些信號(hào)可以是通過(guò)外部引腳輸入的信號(hào),內(nèi)部外設(shè)的輸出信號(hào)以及軟件操作的寄存器的信號(hào)。CLB輸入端都嵌入了可編程的邊沿檢測(cè)器,這些邊沿檢測(cè)器默認(rèn)由上升沿觸發(fā),但可以編程為由下降沿觸發(fā)或完全旁路。

另外,CLB支持8路輸出可以路由到外部引腳、內(nèi)部寄存器或內(nèi)部外圍設(shè)備的輸?。CLB還包含?個(gè)3位硬件計(jì)數(shù)器,以幫助使?CLB構(gòu)建狀態(tài)機(jī)。當(dāng)MCU需要執(zhí)?簡(jiǎn)單的多任務(wù)并?處理,或者需要實(shí)現(xiàn)少量硬件級(jí)實(shí)時(shí)處理時(shí),CLB的作?就會(huì)更?程度地顯現(xiàn)出來(lái)。開(kāi)發(fā)者可以使?CLB來(lái)實(shí)現(xiàn)狀態(tài)機(jī)或“?速”外設(shè),例如軟件驅(qū)動(dòng)的信號(hào)多路復(fù)?器、計(jì)數(shù)器、正交解碼器、步進(jìn)電機(jī)控制器或?速PWM(脈寬調(diào)制器)等。

全新的開(kāi)發(fā)體驗(yàn)

實(shí)際上,對(duì)于Microchip來(lái)說(shuō),在MCU中集成可編程邏輯功能并不是?個(gè)全新的課題。早在?多年前,Microchip就曾在其MCU中引?了?種被稱為可配置邏輯單元(CLC)的可編程邏輯外設(shè),這?設(shè)計(jì)思路的價(jià)值已經(jīng)被市場(chǎng)所驗(yàn)證。隨著實(shí)際應(yīng)?中對(duì)更復(fù)雜的可編程邏輯需求的增加,終在PIC16F13145系列中演化出了CLB這個(gè)規(guī)模更?、更復(fù)雜的可編程邏輯塊,完成了?次重要的迭代升級(jí),也使得該系列MCU能夠?于以往屬于獨(dú)?可編程邏輯器件的應(yīng)?領(lǐng)域。

PIC16F13145系列MCU這一獨(dú)特的定位,可以為開(kāi)發(fā)者帶來(lái)諸多好處。

首先,集成到MCU的CLB,是通過(guò)硬件的方式實(shí)現(xiàn)邏輯功能,在性能上明顯優(yōu)于“通用MCU+軟件”的模式,有利于優(yōu)化嵌入式控制系統(tǒng)的速度和響應(yīng)時(shí)間,提升整體的系統(tǒng)性能。而且由于在系統(tǒng)設(shè)計(jì)時(shí),無(wú)需增加額外的外部邏輯器件,還可以降低BOM成本,可謂是一舉兩得。

其次,作為獨(dú)立于CPU內(nèi)核的外設(shè),PIC16F13145中的CLB可以在CPU處于睡眠模式時(shí)運(yùn)行,以響應(yīng)和處理來(lái)自外部和內(nèi)部的任務(wù),更大限度地降低MCU的功耗。CLB還可以與其他外設(shè)(如定時(shí)器、ADC、PWM模塊等)結(jié)合使用,進(jìn)一步優(yōu)化系統(tǒng)功耗性能。

此外,CLB還有助于PIC16F13145系列MCU實(shí)現(xiàn)更強(qiáng)的可擴(kuò)展性。在實(shí)際工作中,隨著需求的變化,設(shè)計(jì)的調(diào)整在所難免,而PIC16F13145系列MCU所具備的可編程邏輯功能,使得開(kāi)發(fā)者無(wú)需“從頭再來(lái)”徹底修改整個(gè)設(shè)計(jì),就能夠通過(guò)靈活的硬件編程快速完成設(shè)計(jì)迭代,簡(jiǎn)化整個(gè)設(shè)計(jì)流程。

由此可見(jiàn),憑借CLB模塊而帶來(lái)的更高的性能、更低的功耗以及更強(qiáng)的可擴(kuò)展性,加之其他豐富的片上資源(包括具有內(nèi)置計(jì)算功能的快速10位ADC、8位DAC、快速比較器、8位和16位定時(shí)器,以及I2C和SPl等通信模塊),PIC16F13145系列MCU無(wú)疑為嵌入式開(kāi)發(fā)者提供了一個(gè)強(qiáng)大而靈活的開(kāi)發(fā)利器。

完善的開(kāi)發(fā)生態(tài)

當(dāng)然,?個(gè)嵌?式硬件平臺(tái),加上配套的軟件開(kāi)發(fā)?具以及相關(guān)技術(shù)資源,才能夠提供完整的開(kāi)發(fā)體驗(yàn)。具體到PIC16F13145系列MCU這個(gè)創(chuàng)新的硬件架構(gòu),更是需要完善開(kāi)發(fā)?態(tài)的?持,盡可能降低開(kāi)發(fā)者上?“嘗鮮”的?檻。

好消息是,這?點(diǎn)Microchip已經(jīng)準(zhǔn)備好了。PIC16F13145 系列MCU 的開(kāi)發(fā), 可以得到MPLAB 代碼配置器(MCC)的?持,MCC是Microchip的MPLAB X IDE中?個(gè)免費(fèi)軟件插件,為開(kāi)發(fā)者提供了?個(gè)基于GUI的簡(jiǎn)便開(kāi)發(fā)界?,?于配置器件和片上外設(shè)(包括CLB)。CLB所需的?定義邏輯配置可通過(guò)MCC創(chuàng)建原理圖,因此??減少了開(kāi)發(fā)時(shí)間,?且?戶可以使?硬件描述語(yǔ)?(Verilog)作為開(kāi)發(fā)語(yǔ)言,增加了開(kāi)發(fā)的靈活性。自定義邏輯配置的原理圖也可以通過(guò)在線方式創(chuàng)建(logic.microchip.com)。

同時(shí),PIC16F13145 Curiosity Nano評(píng)估套件可為使?PIC16F13145系列MCU進(jìn)?設(shè)計(jì)提供全??持,?需外部?具、編程和調(diào)試,簡(jiǎn)單易?,有助于開(kāi)發(fā)者實(shí)現(xiàn)?縫嵌?式開(kāi)發(fā)體驗(yàn),縮短產(chǎn)品上市時(shí)間。

本文小結(jié)

今天,競(jìng)爭(zhēng)激烈的MCU市場(chǎng),迫切需要差異化的創(chuàng)新產(chǎn)品。Microchip的PIC16F13145系列MCU,創(chuàng)造性地將可編程邏輯外設(shè)功能與8位MCU架構(gòu)相結(jié)合,在繼承MCU固有優(yōu)勢(shì)特性的同時(shí),?帶來(lái)了更佳的性能、低功耗特性和可擴(kuò)展性,在實(shí)時(shí)控制、數(shù)字傳感器節(jié)點(diǎn),以及?業(yè)和汽?等細(xì)分市場(chǎng),為嵌?式開(kāi)發(fā)者提供了全新的想象空間和開(kāi)發(fā)體驗(yàn)。

-

微控制器

+關(guān)注

關(guān)注

48文章

7880瀏覽量

153528 -

FPGA

+關(guān)注

關(guān)注

1643文章

21932瀏覽量

612923 -

mcu

+關(guān)注

關(guān)注

146文章

17768瀏覽量

359062 -

microchip

+關(guān)注

關(guān)注

52文章

1539瀏覽量

118678 -

可編程邏輯

+關(guān)注

關(guān)注

7文章

524瀏覽量

44525

原文標(biāo)題:將“微型FPGA”集成到8位MCU,是種什么樣的體驗(yàn)?

文章出處:【微信號(hào):貿(mào)澤電子,微信公眾號(hào):貿(mào)澤電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

什么是可編程邏輯

什么是可編程邏輯控制器?可編程邏輯控制器有哪些特點(diǎn)?

PLD可編程邏輯器件

可編程邏輯器件基礎(chǔ)及應(yīng)用實(shí)驗(yàn)指導(dǎo)書(shū)

什么是PLD(可編程邏輯器件)

可編程SoC(SoPC),什么是可編程SoC(SoPC)

EDA技術(shù)與應(yīng)用(可編程邏輯器件)

可編程陣列邏輯構(gòu)造_可編程邏輯器材的運(yùn)用

可編程邏輯器件和ASIC對(duì)比介紹

可編程邏輯控制繼電器

可編程邏輯器件測(cè)試方法

評(píng)論