在芯片制造與使用的領域中,靜電是一個不容小覷的威脅。芯片對于靜電極為敏感,而HBM(人體模型)測試和CDM(充放電模型)測試是評估芯片靜電敏感度的重要手段。

那么,HBM和CDM,這兩種測試所代表的風險,哪個更大呢?

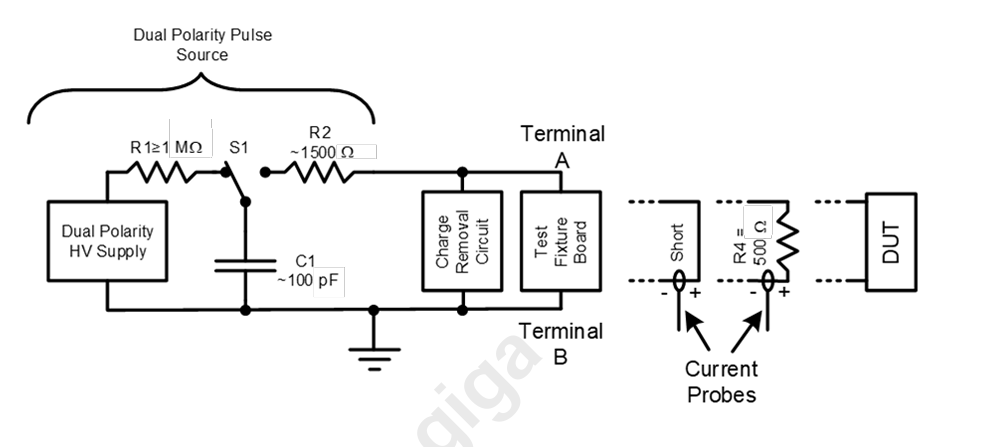

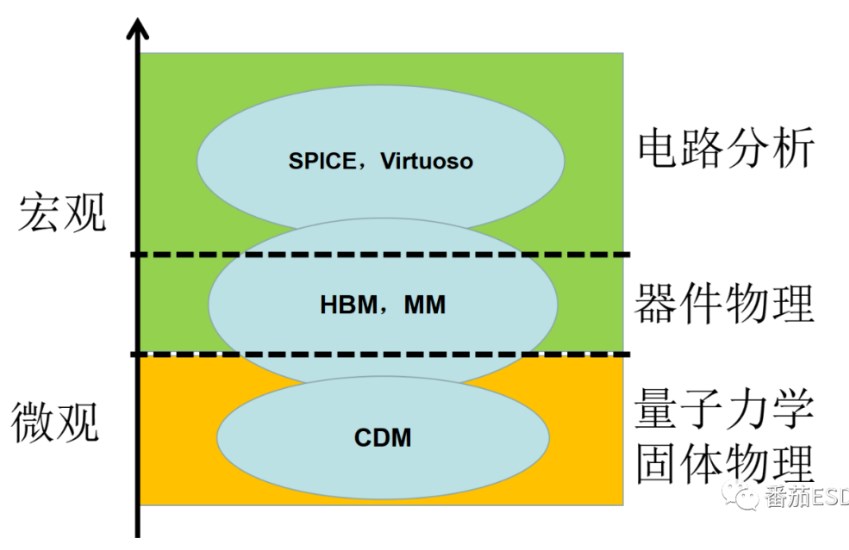

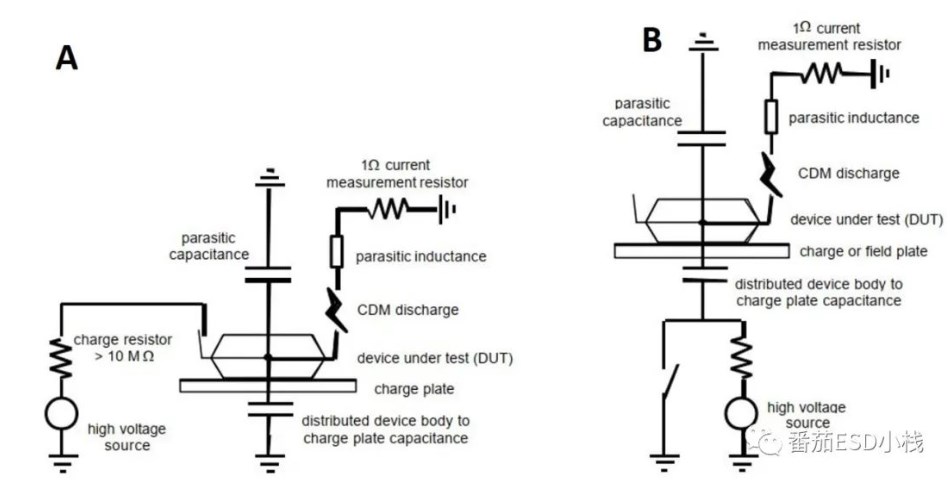

HBM測試主要是模擬人體在接觸芯片時所產生的靜電放電情況。在日常生活中,我們的身體在活動過程中會積累靜電,當這些靜電通過手指等接觸芯片引腳時,就可能對芯片造成損害。在HBM測試中,通過特定的電路模擬出人體靜電的放電波形和能量(如下圖一)。其測試電壓范圍較廣,一般從幾百伏到上萬伏不等。

這種測試方式所代表的風險主要在于:如果芯片在較低的HBM電壓下就出現失效,那么在日常使用中,只要有類似人體靜電放電的情況發生,芯片就可能損壞。比如一些消費電子類芯片,經常會有用戶觸摸操作,如果HBM抗靜電能力差,產品在使用過程中就容易出現故障。

圖一(引用自《ANSI/ESDA/JEDECJS-001-2024》標準)

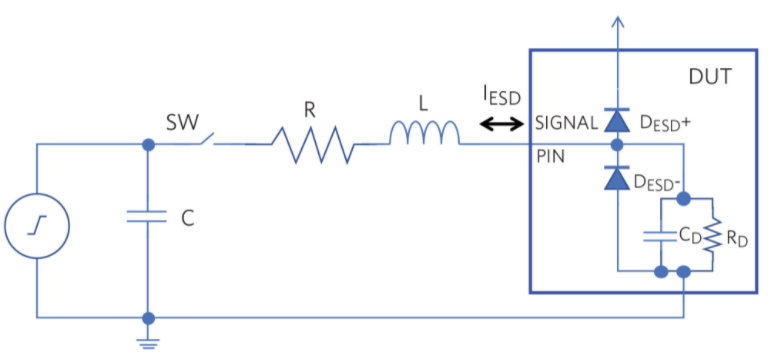

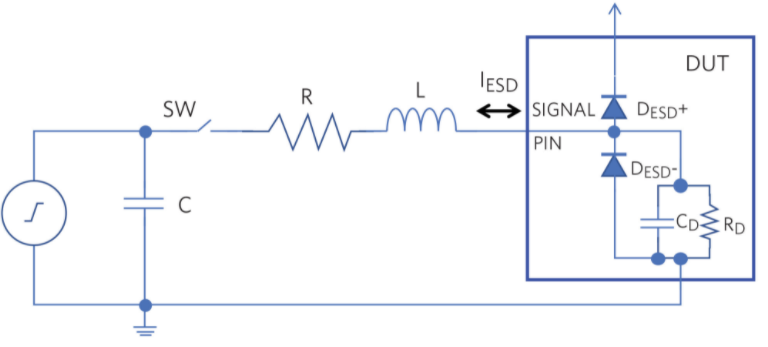

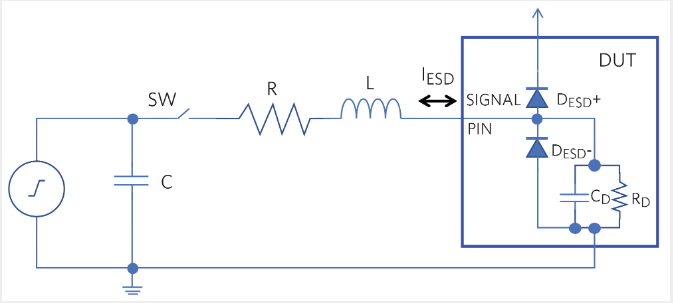

CDM測試則聚焦于芯片自身帶電所產生的靜電放電情況。在芯片的生產、運輸和組裝過程中,芯片可能會因為摩擦等原因而帶上靜電。當芯片與接地的物體接觸時,這些靜電就會瞬間釋放。

CDM測試的特點是放電時間非常短,通常在皮秒級別,但其放電電流卻很大。這意味著芯片在這種情況下所承受的能量沖擊是非常強烈的。例如在芯片制造的自動化生產線中,芯片在高速傳輸過程中如果CDM抗靜電能力不足,就可能在與設備接觸瞬間被靜電損壞,導致生產良率下降。

從芯片的使用場景來看,對于那些經常會被人體接觸的芯片,如手機芯片、電腦鼠標等設備中的芯片,HBM測試所代表的風險就顯得尤為關鍵。

但對于芯片的生產環節,特別是自動化程度高、芯片頻繁在設備之間傳輸的情況,CDM測試的風險則更為突出。

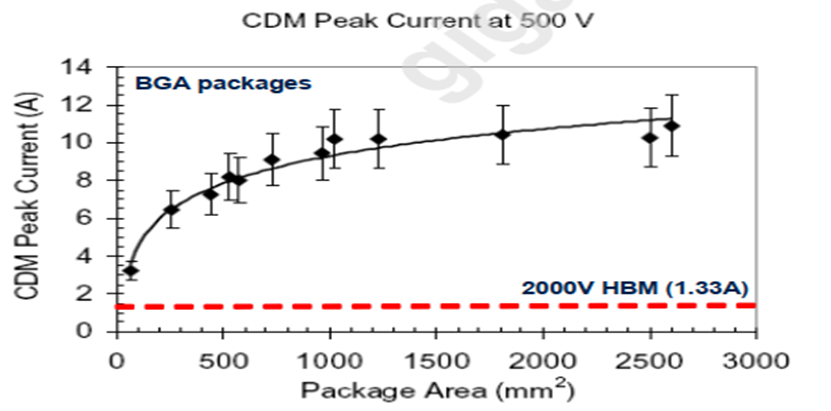

如今隨著芯片功能迭代的增加,采用了先進制程、更小晶體管尺寸的芯片,更大規模的封裝,充放電量更大,更容易被瞬間的大電流破壞;而HBM的ESD能量不變,比較穩定,在迭代過程中風險相對小,所以從某種程度上來說,CDM的風險相對而言大一些。(如下圖二)

圖二(引用自《JEP157》標準)

季豐電子

季豐電子成立于2008年,是一家聚焦半導體領域,深耕集成電路檢測相關的軟硬件研發及技術服務的賦能型平臺科技公司。公司業務分為四大板塊,分別為基礎實驗室、軟硬件開發、測試封裝和儀器設備,可為芯片設計、晶圓制造、封裝測試、材料裝備等半導體產業鏈和新能源領域公司提供一站式的檢測分析解決方案。

季豐電子通過國家級專精特新“小巨人”、國家高新技術企業、上海市“科技小巨人”、上海市企業技術中心、研發機構、公共服務平臺等企業資質認定,通過了ISO9001、 ISO/IEC17025、CMA、CNAS、IATF16949、ISO/IEC27001、ISO14001、ANSI/ESD S20.20等認證。公司員工近1000人,總部位于上海,在浙江、北京、深圳、成都等地設有分公司。

-

芯片

+關注

關注

455文章

50714瀏覽量

423138 -

集成電路

+關注

關注

5387文章

11530瀏覽量

361630 -

靜電測試

+關注

關注

0文章

17瀏覽量

9445 -

HBM

+關注

關注

0文章

379瀏覽量

14744

原文標題:技術文章 | 芯片靜電測試之HBM與CDM,哪個風險更大?

文章出處:【微信號:zzz9970814,微信公眾號:上海季豐電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

HBM靜電測試機尾波的危害

什么是小尺寸集成電路CDM測試?

芯片IC可靠性測試、靜電測試、失效分析

半導體測試HBM了解一下~

同樣都HBM,芯片級(component level)和系統級(system level)的差別在哪里?

靜電放電(ESD: Electrostatic Discharge)是什么?

季豐電子CDM測試機已全部配備高帶寬的6G示波器

什么是AEC-Q-CDM測試?

芯片靜電測試之HBM與CDM詳解

芯片靜電測試之HBM與CDM詳解

評論