在技術推動下,半導體領域不斷突破界限,實現人工智能(AI)、高性能計算(HPC)、5G/6G、自動駕駛、物聯網(IoT)等領域的變革性應用。

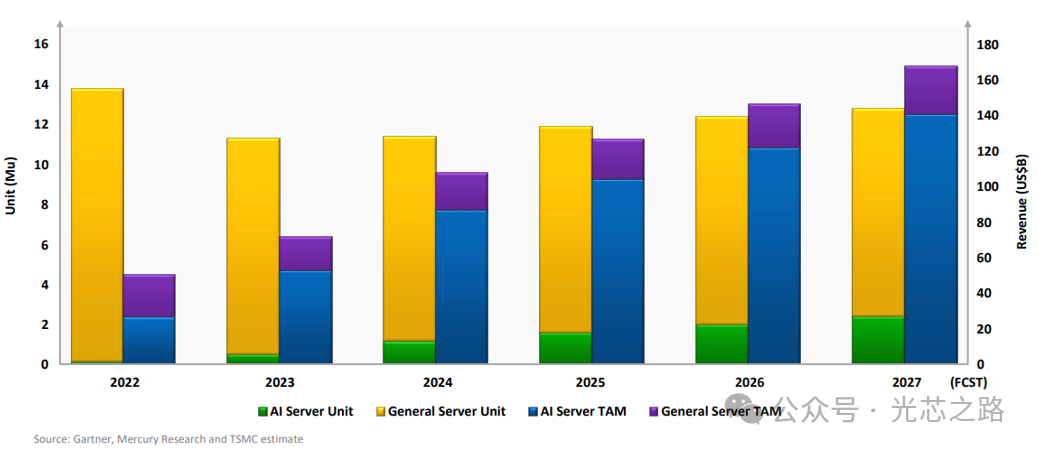

AI Server ASP比General Server高很多,2022~2027年AI服務器單元復合年增長率為73%,收入復合年增長率為39%.

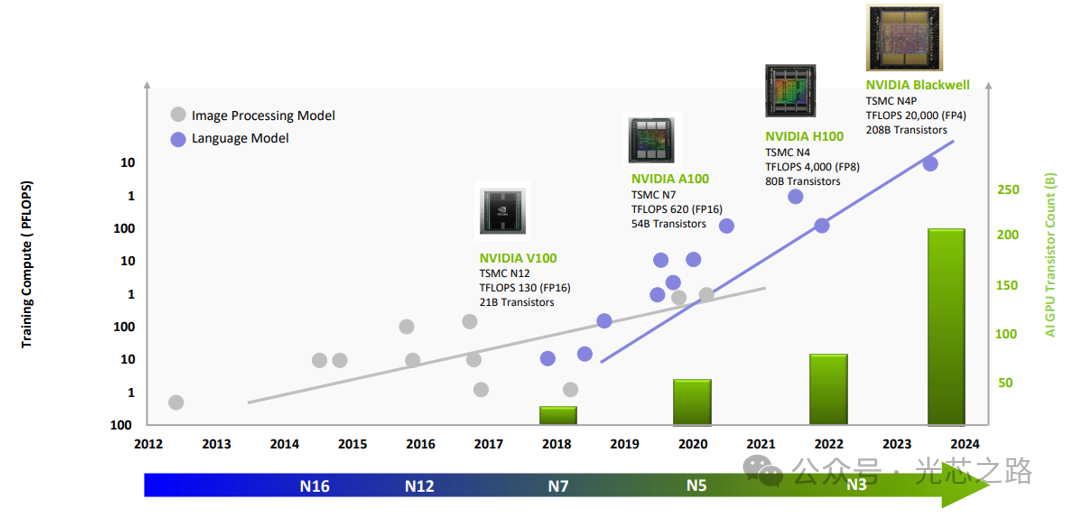

技術進步引發人工智能爆炸式增長,更多的計算,更高的內存帶寬,更大規模的異構集成。

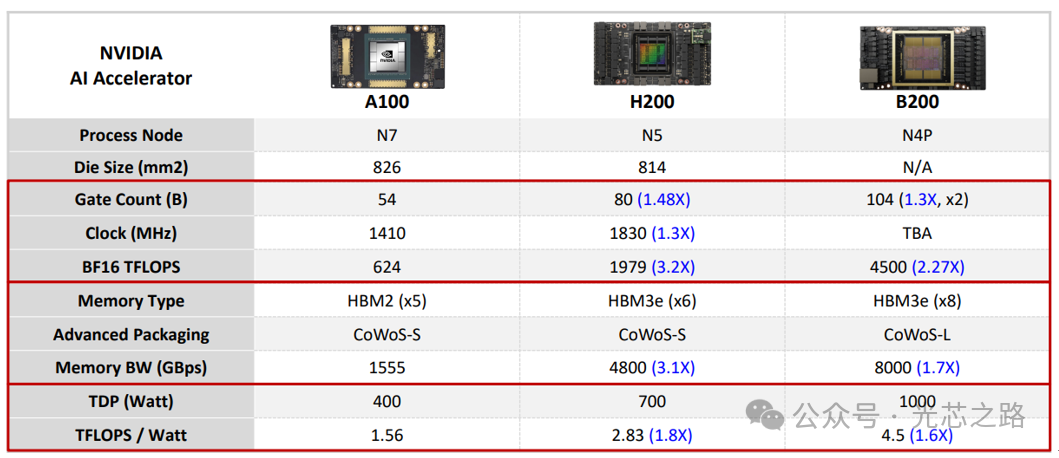

先進的邏輯和封裝技術為人工智能加速器做出了關鍵貢獻,性能、內存帶寬和電源效率都不斷提升。

NVIDIA從V100升級到Blackwell,TSMC制程從N12到N4P,都是基于CoWoS封裝平臺,晶體管數量翻了近10倍,存儲帶寬容量翻了5倍,TFLOPS/W也越來越大。

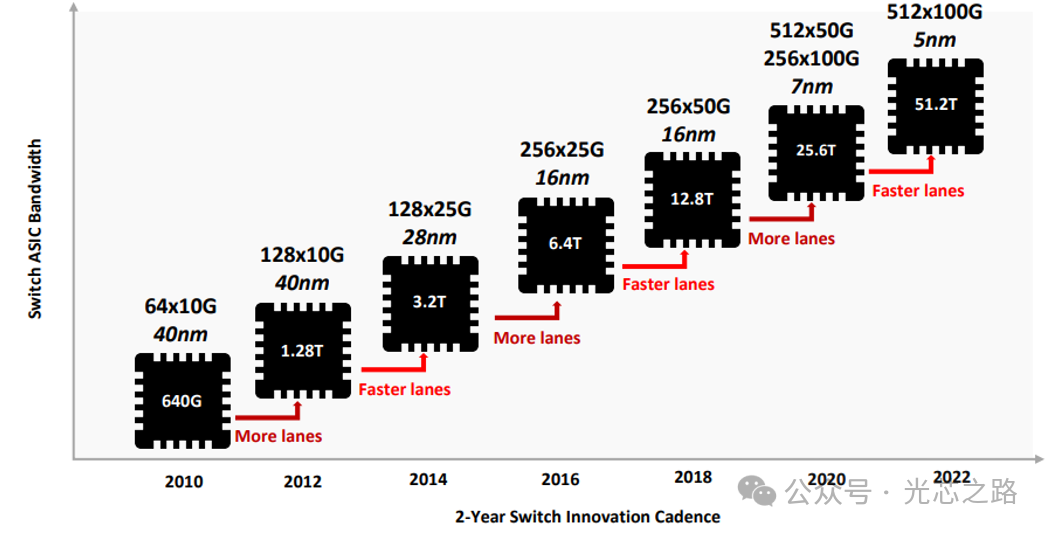

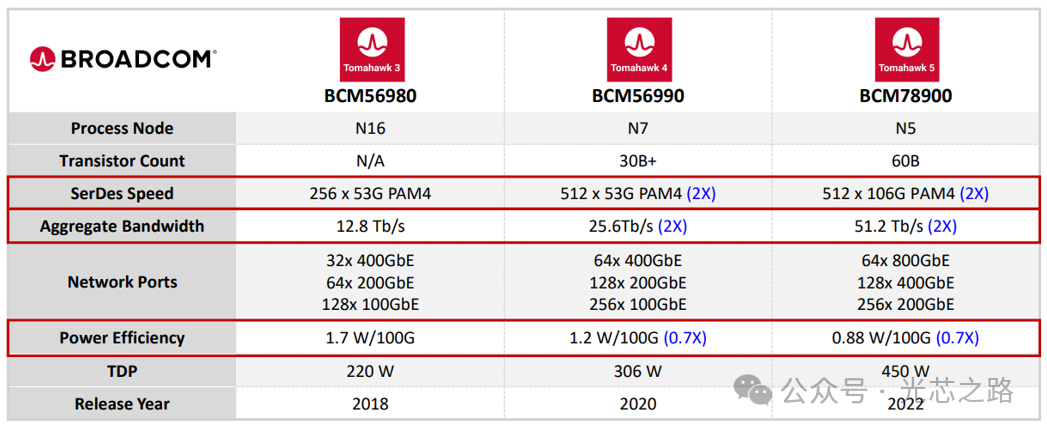

先進的邏輯和封裝技術在交換機產品做出了關鍵貢獻,SerDes性能、網絡帶寬和功耗方面不斷提升。

AI數據中心需要強大后端數據流來支持繁重并行GPU通信,需要更快數據速率和更低功耗的交換機解決方案。

Broadcom交換機容量已經發展到51.2T,基于N5的BCM78900的serdes雙向速率達到512*106G PAM4,雖然整體功耗為450W,但能耗0.88W/100G是降低的。

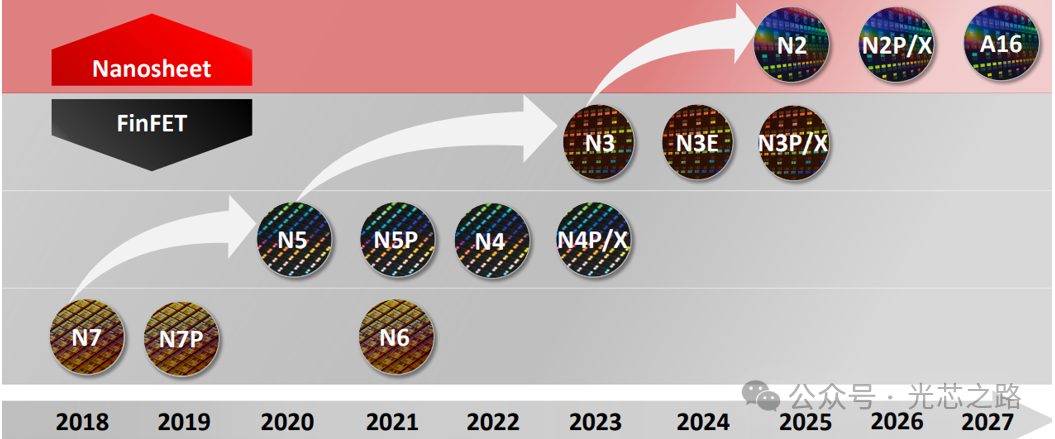

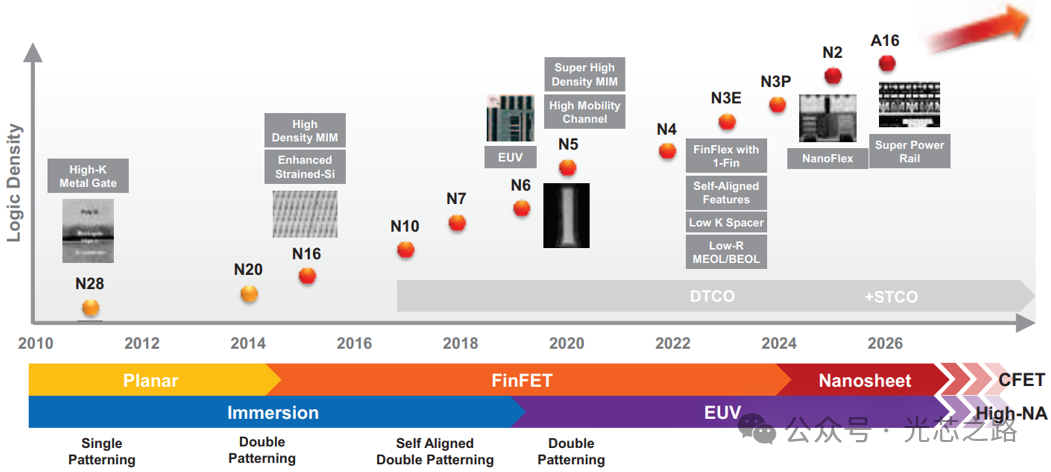

邏輯技術繼續穩步發展,節點的減少意義重大,可以提高密度和能源效率。例如,7nm到5nm,可以增加1.83倍的邏輯密度和13%速率,同時能耗減少21%。如果進一步的,5nm到3nm,可以再次增加1.57倍的邏輯密度和11%速率,同時減少30% 能耗。

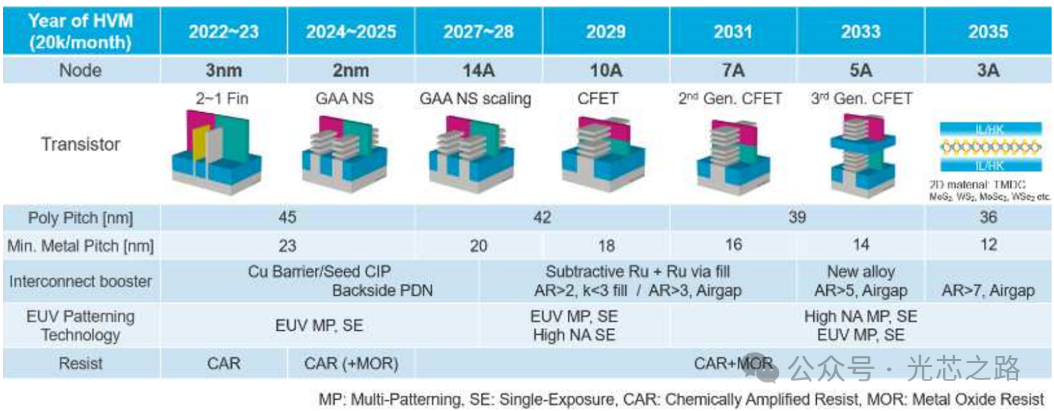

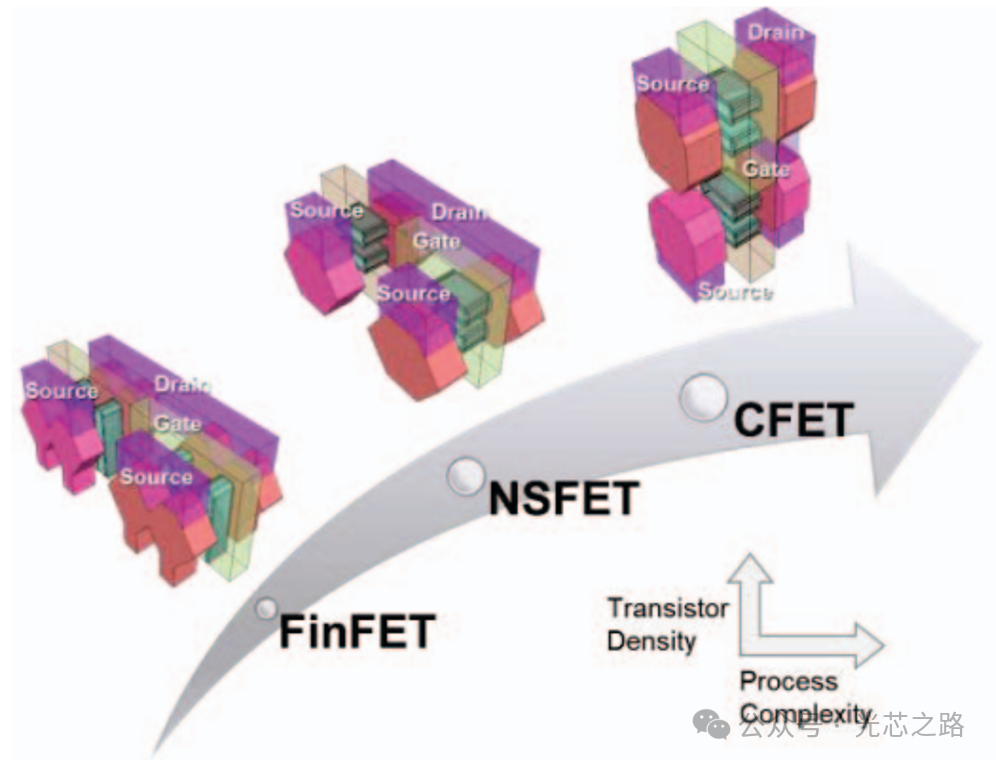

可以預見,如果把制程進一步減少,能獲得更大收益。7nm到3nm仍是基于FinFET。今天,業界繼續通過在3/2nm節點過渡到納米片場效應晶體管(NSFET)器件來縮放晶體管尺寸。為了最大限度地利用器件架構和光刻技術的進步,DTCO至關重要,DTCO不僅推動邏輯技術的性能、功率和面積(PPA),而且還被擴展到優化系統級的性能和功率。

隨著FinFET技術和納米片架構的引入,互補場效應晶體管(CET)架構已經成為未來邏輯縮放的主要競爭者。雖然垂直堆疊的FET預計會增加工藝復雜性和制造成本,但它提供顯著的密度優勢,與傳統CMOS結構相比,在相同柵極間距上,大約高1.5到2倍。

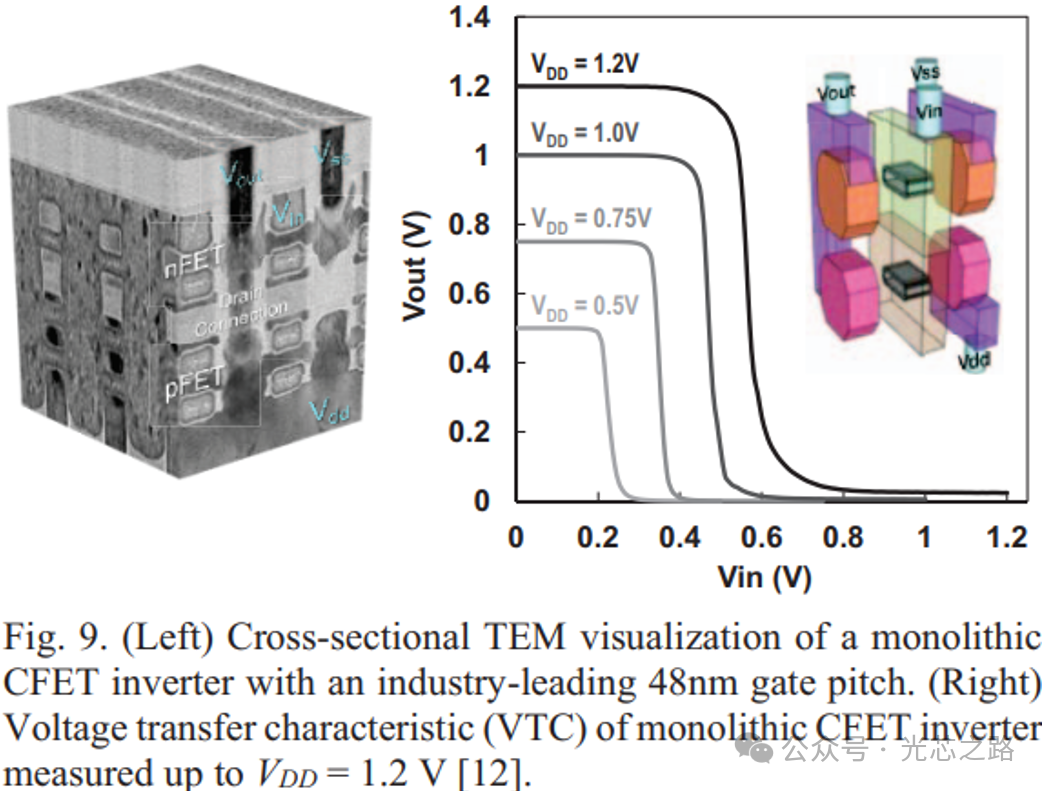

下圖展示最先進的CFET逆變器,具有業界領先的48nm柵極間距,強大的電壓轉移特性(VTC)響應VDD高達1.2 V。這標志著單片CFET技術的開創性突破,為推動未來邏輯技術擴展的工藝架構奠定基礎。

除了CEFET之外,對更高性能和更節能的邏輯技術的持續追求需要加速尋找超越硅基材料的通道材料。例如對于碳納米管來說,通過特定的摻雜技術可以實現與PMOS相當的NMOS性能,增強其高電流密度能力。

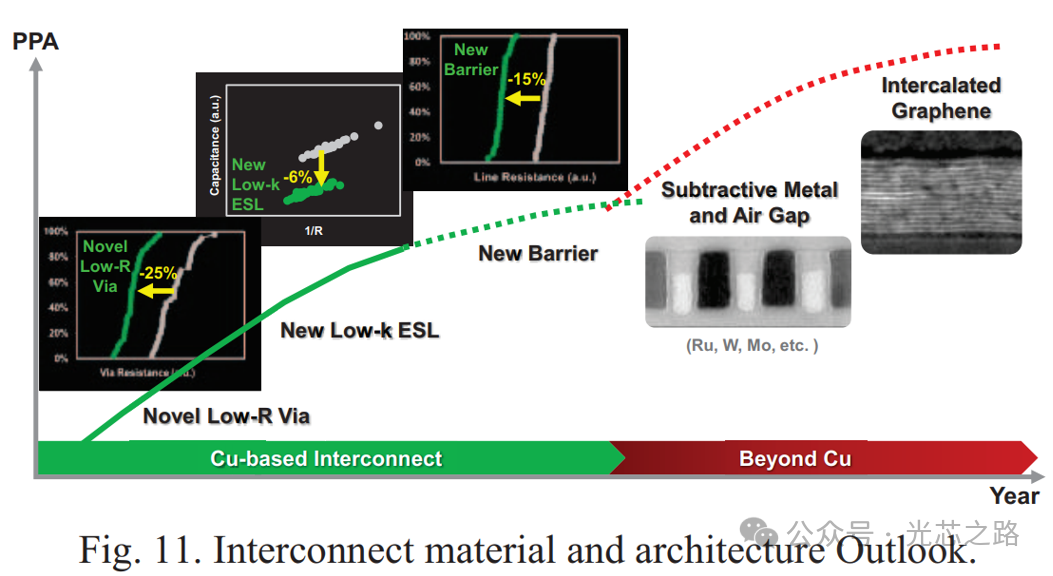

互聯創新是技術進步的另一個關鍵領域。下圖突出顯示該行業正在進行的幾個新開發。通過使用低電阻材料和先進界面工程,MOL電阻降低了40%。正在探索一種新的二維材料,作為銅互連的優越替代品,這種材料在厚度減小的情況下,薄膜電阻率比銅低,提高整體性能。

另一個關鍵技術是BEOL工藝和背面功率傳輸。

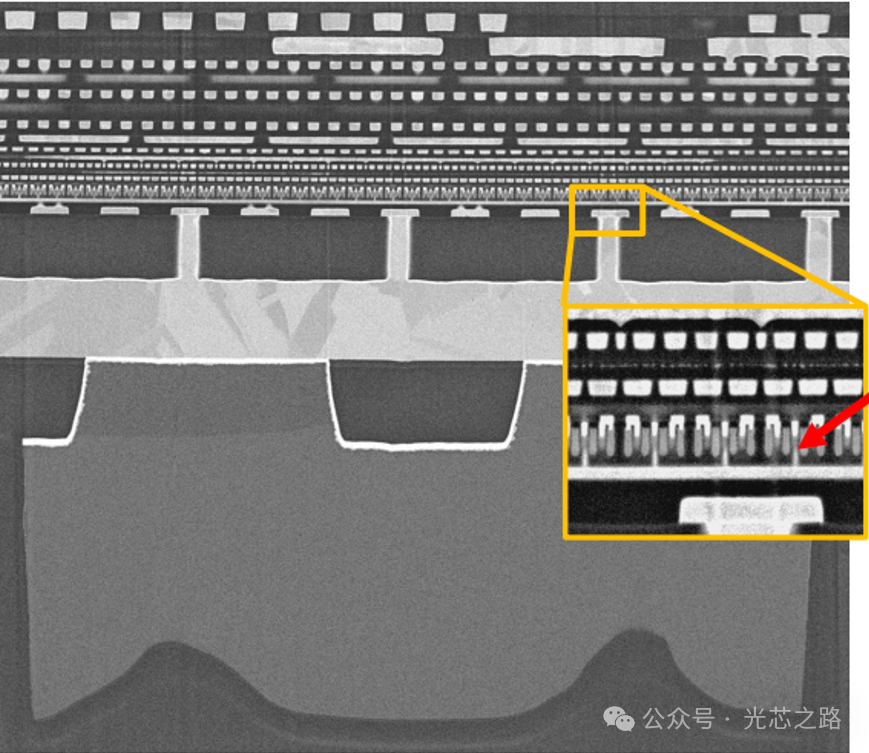

下圖展示最先進的2nm技術的橫截面,該技術具有納米片器件和背面功率傳輸。在晶圓的正面,納米片器件通過結構和DTCO創新提供出色的功率效率。BEOL工藝和材料的創新有助于將RC延遲減少10%,邏輯密度增加3%至4%。在晶圓的背面,直接與器件接觸可以保持柵極密度并保持器件寬度的靈活性。背面金屬化增強功率傳輸,通過將前端路由專用于信號路徑來提高芯片密度和性能。

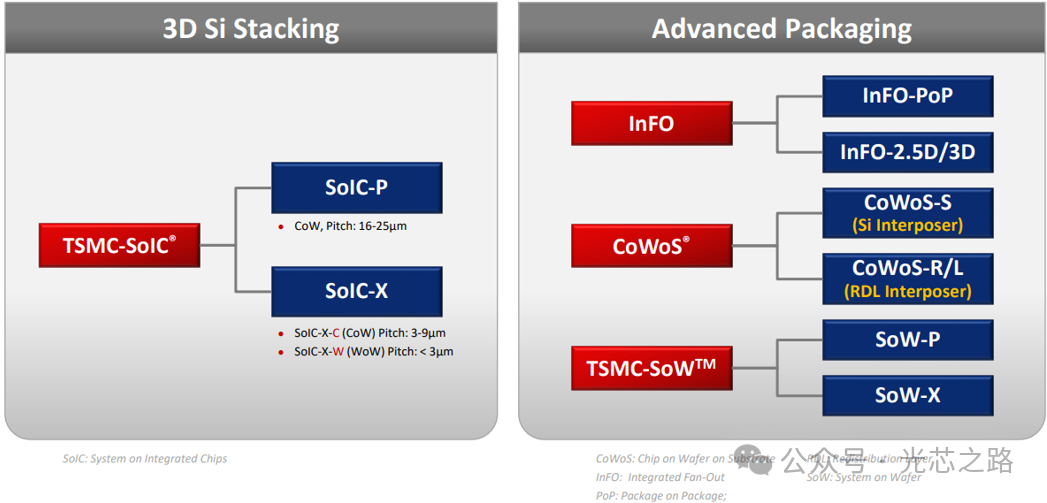

為了釋放異構集成的力量并將系統級性能提高十倍以上,3D堆疊和2.5D先進封裝技術已經相繼引入。TSMC提供CoWos先進2.5D封裝以及SOIC的3D芯片堆疊技術,以適應不同客戶需求。

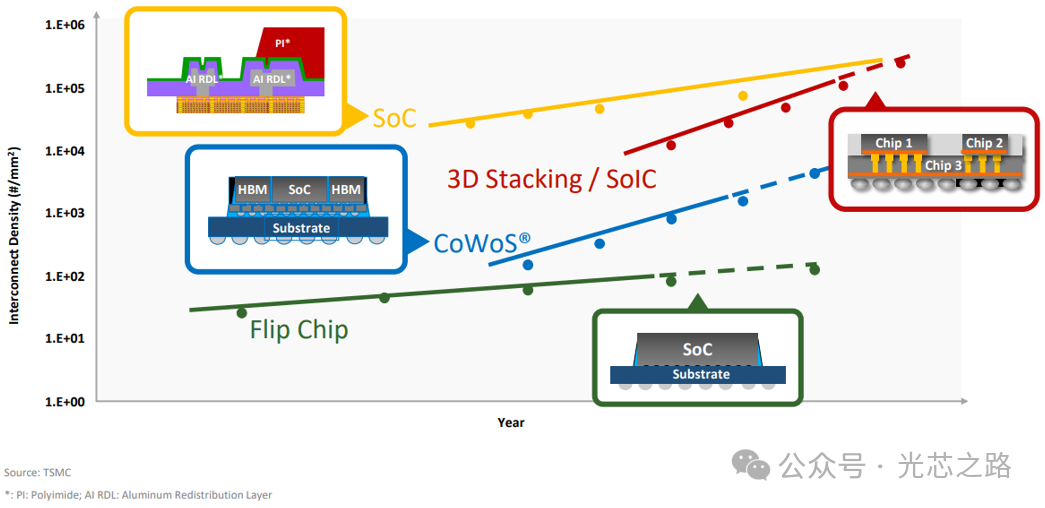

先進的硅堆疊和封裝技術,包括SoIC, InFO和CoWoS,繼續積極地縮小芯片到芯片的互連間距,提供將3D互連密度再提高六個數量級的潛力,這些高級集成功能可提高數據傳輸速率、減少延遲、優化功耗并提高計算系統的整體性能。

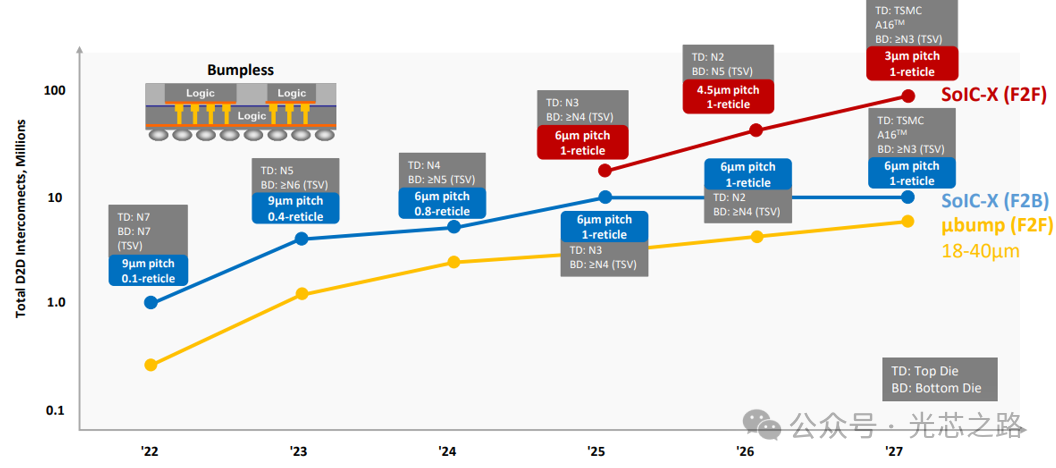

3D堆疊技術提供一個新的維度,可以幫助密度和能效縮放。首款基于3D堆疊技術的用于數據中心的CPU于2022年發布,AI GPU于2023年發布。未來TSMC基于SOIC-X技術,可將間距減少到3um,將D2D互聯達到100 million量級。

2.5D技術范圍正在迅速擴大,以滿足未來人工智能計算的集成需求。

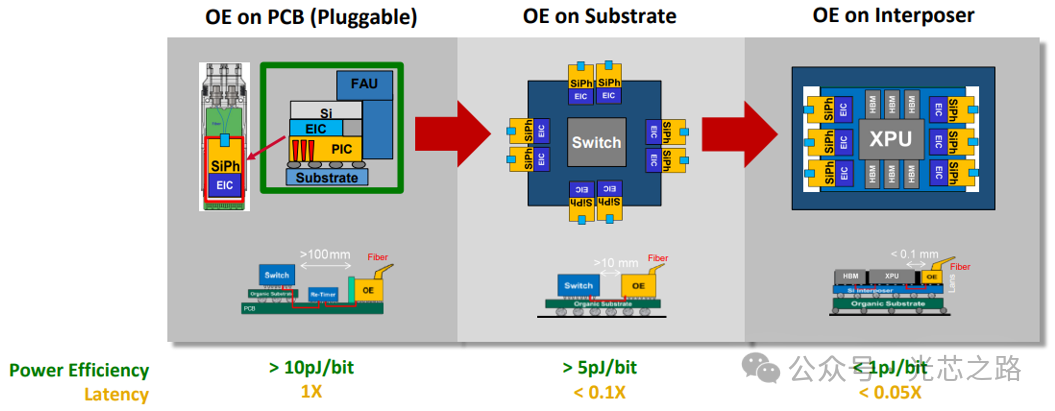

光收發器對于未來的人工智能系統至關重要,可以實現芯片之間高速、低能耗和可靠的數據傳輸。硅光為系統技術改變新的傳輸方式。緊湊型通用光子引擎(COUPE)技術采用創新的SoIC-X工藝無縫堆疊電子和光子芯片,顯著降低功耗和延遲。OE (Optical Engine)通過垂直堆疊,封裝密度高,在電路板、封裝和中介層相比在外形尺寸和功耗降低方面提供實質性好處.

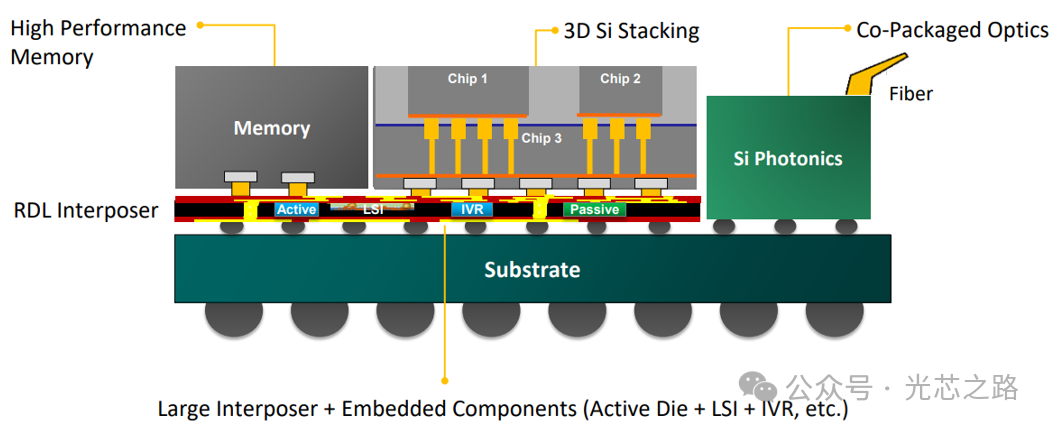

為簡化不同封裝結構和配置的3D IC設計,需要創建一個可以提供異構集成所需的全面覆蓋的技術平臺。該平臺包括先進邏輯技術,堆疊SoIC技術,集成嵌入式組件,連接到計算芯片和高性能存儲器的RDL中間體,以及硅光引擎,以提供足夠的I/O帶寬以滿足計算需求。

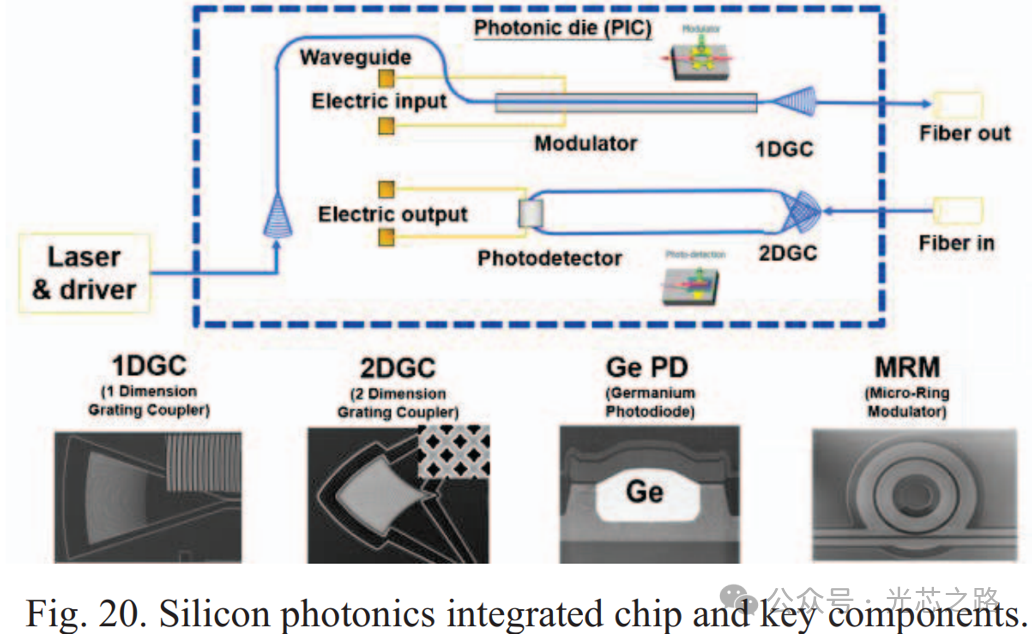

硅光技術將無源和有源光子器件集成到單個芯片中,包括光柵耦合器、調制器、波導和鍺(Ge)光電二極管等組件,但激光源除外。TSMC的硅光利用先進的12英寸工藝技術,提供卓越的工藝能力和可控性。為客戶能夠設計單芯片光學引擎(OE)。

總之,在人工智能的推動下,到2030年半導體產業規模將達到1萬億美元,人工智能對數據中心、邊緣設備、汽車和物聯網產品具有變革性影響。邏輯、內存和封裝技術的進步,為滿足人工智能驅動的需求,繪制一條持續密度和能效擴展的道路。

參考文獻

【1】SemiconductorIndustry Outlook and New Technology Frontiers Yuh-Jier Mii Taiwan SemiconductorManufacturing Company, Hsinchu, Taiwan. Contact email: yjmii@tsmc.com

-

半導體

+關注

關注

334文章

27286瀏覽量

218072 -

場效應晶體管

+關注

關注

6文章

363瀏覽量

19492 -

人工智能

+關注

關注

1791文章

47183瀏覽量

238246

原文標題:IEDM2024:TSMC關于未來整體半導體產業分析

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

芯和半導體邀您相約ICCAD-Expo 2024

造物數科數智成果亮相2024電子半導體產業創新發展大會

興森科技亮相2024電子半導體產業創新發展大會

第六屆意法半導體工業峰會2024

【ISES China 2024精彩回顧】半導體精英齊聚,共促產業創新發展

KOWIN康盈半導體閃耀2024世界半導體大會

揚杰科技亮相2024全球車規級功率半導體峰會暨優秀供應商創新展

喜訊 | MDD辰達半導體榮獲藍點獎“最具投資價值獎”

2024年全球半導體產業發展態勢解析

雖然寒冷,但展望2024,中國半導體和中國半導體人更要成為一束光

Transphorm:氮化鎵應用進一步擴展,2024年下半年半導體市場將回暖

IEDM2024:TSMC關于未來整體半導體產業分析

IEDM2024:TSMC關于未來整體半導體產業分析

評論