CMSO電路:

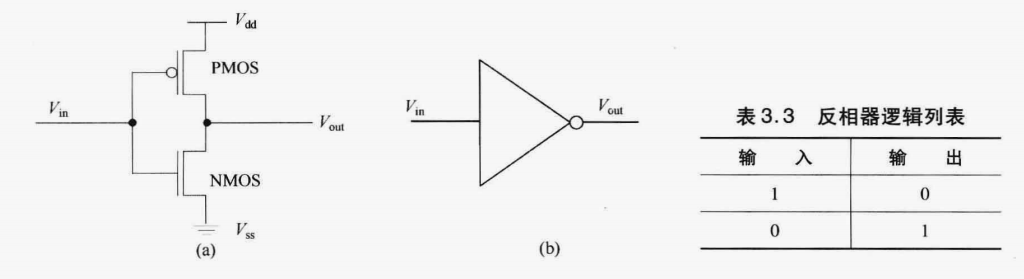

下圖顯示了一個CMOS反相器電路。

從圖中可以看出它由兩個晶體管組成,一個為NMOS,另一個為 PMOS。

當輸入為高電壓或邏輯1時,NMOS 就會被開啟而 PMOS 會被關閉。因為輸出電壓為接地電壓Vss,所以輸出電壓Vout為低電壓或邏輯0。

反之,若輸入為低電壓或邏輯0時,NMOS 就會被關閉而 PMOS 被開啟。輸出電壓為高電壓Vdd,所以輸出電壓Vout為高電壓或邏輯1。

由于CMOS會反轉輸入信號,所以被稱為反相器。這個設計是邏輯電路中使用的基本邏輯單元之一。

理想狀態下,Vdd和Vss之間并沒有電流流動,所以CMOS的耗電量很低。CMOS反相器的主要電能損耗由高頻開關轉換時的漏電流形成。CMOS優于NMOS之處還包括有較高的抗干擾能力、芯片溫度低、使用溫度范圍廣和較少的定時復雜性。

將CMOS和雙載流子技術結合形成的BiCMOS IC在20世紀90年代迅速發展,CMOS電路用于邏輯部分,雙載流子晶體管可增加元器件的輸入/輸出速度。由于BiCMOS已經不再是主流產品,并且當IC的應用電壓降到1V以下時就會失去應用性,所以書中并未對這種工藝做詳細探討。

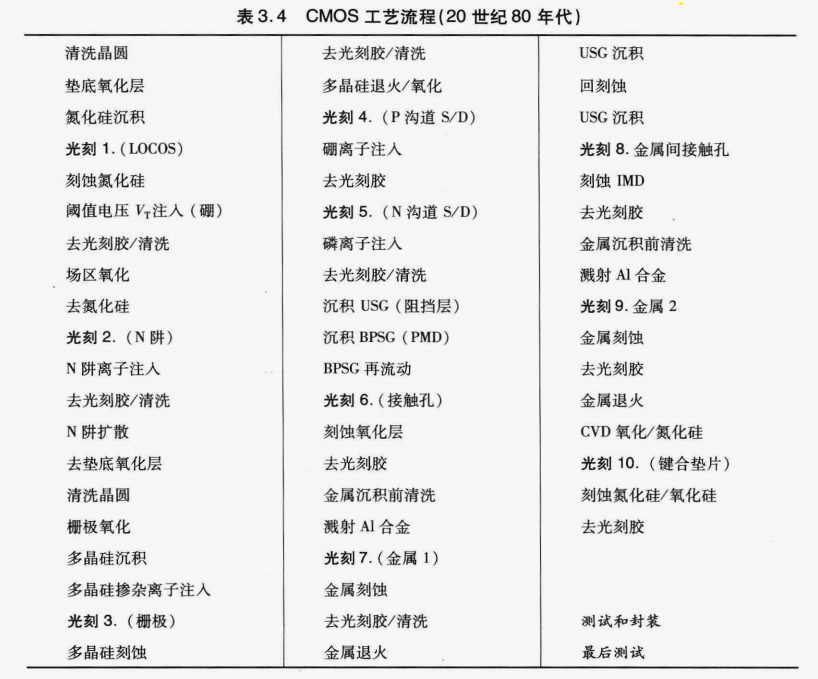

CMOS工藝(20世紀80年代):

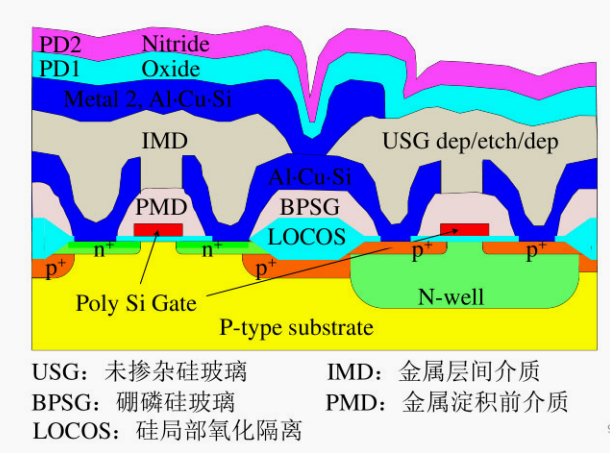

上圖顯示了20世紀80年代的CMOS工藝過程,晶體管之間的隔離用硅局部氧化(LOCOS)取代整面全區覆蓋式氧化。

硼磷硅玻璃(BPSG)用于作為金屬沉積前的電介質層(PMD)或中間隔離層(ILD0),以降低所需的再流動溫度。

尺寸的縮減使大多數圖形化刻蝕采用等離子體刻蝕(干法刻蝕)取代濕法刻蝕,單層金屬線已不足以將IC芯片上所有的元器件按照所需的電導率連接,所以必須使用第二金屬層。

20世紀80年代~90年代,金屬線之間的介質沉積和平坦化是一大技術挑戰,即金屬層間電介質層(IMD,Inter Metal Dielectric)。20世紀80年代,最小的圖形尺寸從3μm縮小到0.8μm。

CMOS的基本工藝步驟包括晶圓預處理、阱區形成、隔離區形成、晶體管制造、導線連接和鈍化作用。

晶圓預處理包含外延硅沉積、晶圓清洗、對準記號刻蝕。阱區形成為NMOS和PMOS晶體管定義出器件區。阱區形成按技術發展程度的不同分為單一阱區、自對準雙阱區(也稱單一光刻雙阱區)和雙光刻雙阱區。隔離技術以建立電氣隔離區的方式隔絕鄰近的晶體管。20世紀80年代,硅局部氧化取代了整面全區覆蓋式氧化成為隔離技術的主流。晶體管制造則涉及了柵極氧化層的生長、多晶硅沉積、光刻技術、多晶硅刻蝕、離子注入以及加熱處理,這些都是IC工藝中最重要的工藝步驟。導線連接技術結合了沉積、光刻和刻蝕技術定義金屬線,以便連接建造在硅表面上的數百萬個晶體管。最后通過鈍化電介質的沉積、光刻和刻蝕技術將IC芯片密封起來與外界隔離,只保留鍵合墊區的開口以供測試和焊接用。

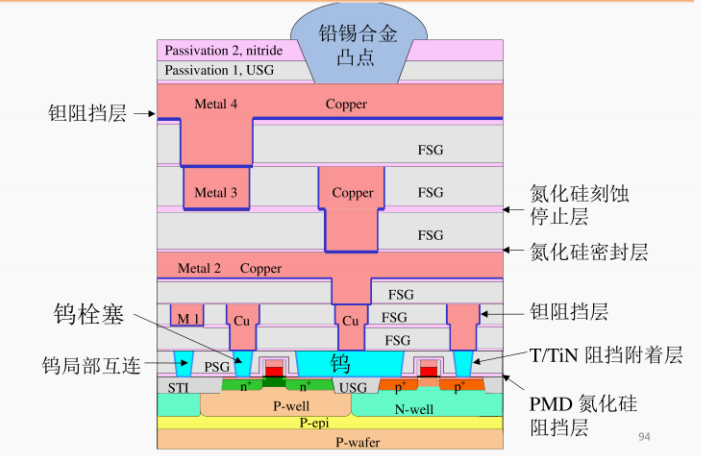

CMOS工藝(20世紀90年代):

從20世紀90年代開始,IC芯片的圖形尺寸持續地從0.8μm縮減到0.18um以下,同時IC制造業也采用了一些新的技術。

當圖形尺寸小于0.35um時,隔離區形成就采用淺溝槽隔離(STI)取代硅的局部氧化技術。金屬硅化物廣泛用于形成柵極和局部連線,鎢被廣泛用做不同金屬層間的金屬連線,即所謂的栓塞(“Plug”)。越來越多的生產線使用化學機械研磨(CMP)技術形成STI、鎢栓塞和平坦化的層間電介質(ILD)。高密度等離子體刻蝕和化學氣相沉積(CVD)更受歡迎,銅金屬化已開始在生產線上嶄露頭角。下圖為一個具有四層銅金屬互連和一個Al/Cu合金焊盤層的CMOSIC橫截面。

2000年后半導體工藝發展趨勢

光學光刻波長:193nm

浸入式光刻技術、雙重圖形技術

自對準材料:鎳硅化取代鈷硅化物

低K層間介質

高K-金屬柵

應變硅技術

FinFET

……

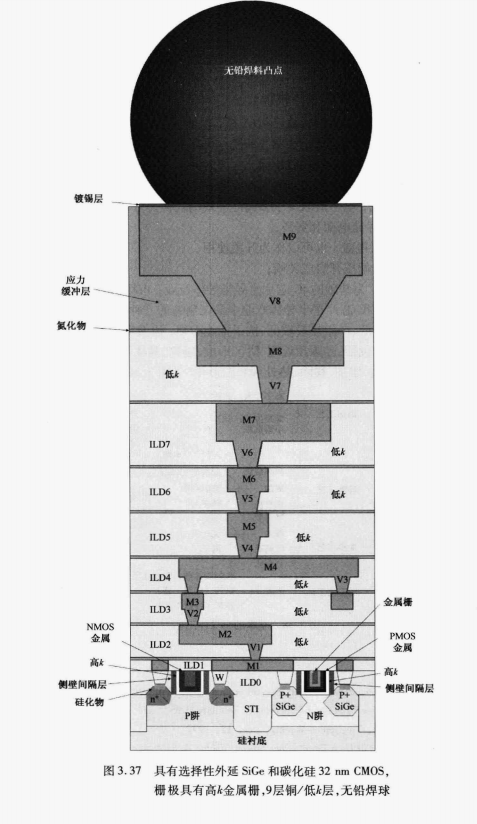

21世紀初,CMOS集成電路技術進人納米技術節點。該技術節點從130nm縮小到32nm。193 nm波長的光成為占主導地位的光學光刻波長。浸入式光刻技術利用水在物鏡和晶圓光刻膠之間作為媒介,以進一步改善圖形精度,這種技術已經成為廣泛使用在45nm節點及以后的IC制造中。45nm技術節點后,雙重圖形技術已被用于IC制造。浸入式光刻和雙重圖形相結合,可以幫助IC制造商進一步縮小圖形尺寸。從65nm節點開始,鎳硅化物取代鈷硅化物作為自對準硅化物材料的選擇。高k和金屬柵極開始取代二氧化硅和多晶硅作為柵介質和柵電極材料。廣泛應用的諸如應變硅襯底工程,通過提高載流子遷移率提高器件的性能。如雙應力和選擇性外延硅鍺(eSiGe)技術使MOSFET溝道硅層應變增加載流子遷移率和器件速度。下圖顯示了一個具有選擇性外延SiGe和碳化硅的32nm CMOS截面圖,柵具有高k金屬,9層銅互連,而且無鉛焊球。

-

CMOS

+關注

關注

58文章

5710瀏覽量

235407 -

反相器

+關注

關注

6文章

311瀏覽量

43289 -

半導體芯片

+關注

關注

60文章

917瀏覽量

70611

原文標題:半導體芯片的制造工藝流程

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

半導體芯片的制造工藝流程

半導體芯片的制造工藝流程

評論