1、滯回比較器

當 VIN(+) > VIN(-),輸出高電平;VIN(+) < VIN(-),則輸出低電平,這就是單限比較器的功能。但當兩個輸入端信號極為接近時,由于輸入電壓的毛刺或者電壓波動,就會導致輸出產生高低電平連續跳變。滯回比較器可以很好解決這個問題,具有很強的抗干擾能力。

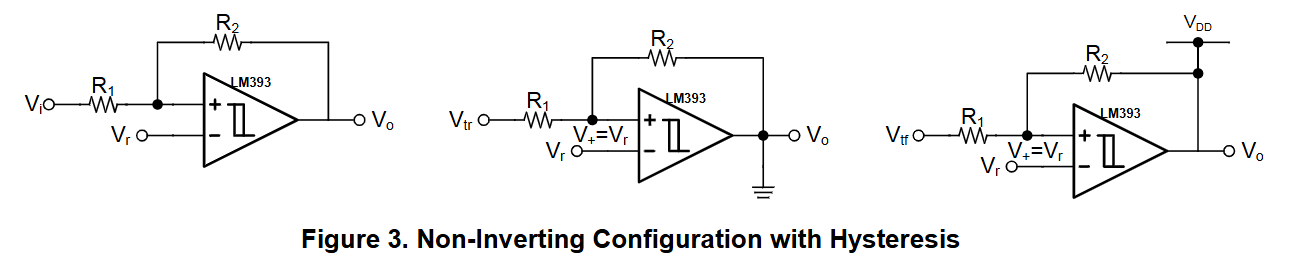

滯回比較器可分為上行滯回比較器(同相輸入)和下行滯回比較器(反相輸入)。

2、上行滯回比較器(同相輸入)

上行滯回比較器(同相輸入),輸入信號Vi接在同相端(比較器輸入的正端),參考信號Vr接在反向端(比較器輸入的負端)。

輸入信號Vi為low時,輸出信號Vo也為low。

輸入信號Vi上升到電壓Vtr后,輸出信號Vo變為high。

輸入信號Vi為high時,輸出信號Vo也為high。

輸入信號Vi由high下降到Vtf后,輸出信號Vo變為low。

當輸入信號Vi上升到Vtr時,輸出信號Vo還是為零。(如下圖中的第二圖所示)

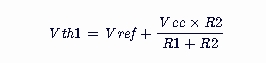

利用運放的“虛短”和“虛斷”原理計算:

Vr=R2/(R1+R2)*Vtr

Vtr=(R1+R2)/R2*Vr

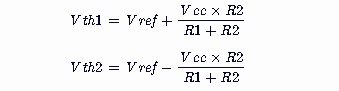

當輸入信號Vi下降到Vtf時,輸出信號Vo還是為high,即電壓VDD。(如下圖中的第三圖所示)

利用運放的“虛短”和“虛斷”原理計算:

Vr=[(VDD-Vtf)*R1]/(R1+R2)+Vtf

Vtf=(R1+R2)/R2*Vr-R1/R2*VDD

Vhyst=Vtr-Vtf=R1/R2*VDD

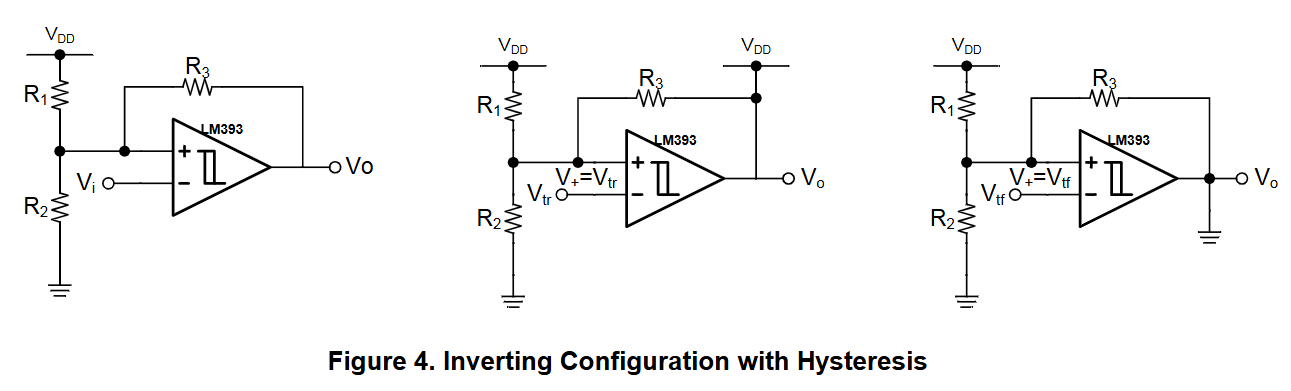

3、下行滯回比較器(反相輸入)

下行滯回比較器(反相輸入),輸入信號Vi接在反相端(比較器輸入的負端),參考信號Vr接在正相端(比較器輸入的正端)。

輸入信號Vi為low時,輸出信號Vo為high。

輸入信號Vi上升到電壓Vtr后,輸出信號Vo變為low。

輸入信號Vi為high時,輸出信號Vo為low。

輸入信號Vi由high下降到Vtf后,輸出信號Vo變為high。

當輸入信號Vi上升到Vtr時,輸出信號Vo還是為high,即電壓為VDD。(如下圖中的第二圖所示)

利用運放的“虛短”和“虛斷”原理計算:

Vtr=R2/(R1||R3+R2)*VDD

當輸入信號Vi下降到Vtf時,輸出信號Vo為零。(如下圖中的第三圖所示)

利用運放的“虛短”和“虛斷”原理計算:

Vtf=(R2||R3)/(R2||R3+R1)*VDD

Vhyst=Vtr-Vtf=(R1||R2)/(R1||R2+R3)*VDD

4、小結

1、滯回比較器上的反饋電阻越大,輸出的響應時間就越慢。

2、上行滯回比較器,當Vi增大到Vtr時,輸出由low跳變到high;當Vi減小到Vtf時,輸出由high跳變到low。

3、下行滯回比較器,當Vi增大到Vtr時,輸出由high跳變到low;當Vi減小到Vtf時,輸出由low跳變到high。

4、Vtr和Vtf分別為上下電壓門限,也就是滯回比較器閾值,Vtr-Vtf為回差或門限寬度。

5、計算上下電壓門限值時,是瞬態的方法,即輸出為零或高來計算的。

——END——

叢林社會,從來不相信眼淚;再多的抱怨也沒有用,不會有人可憐的

推薦閱讀

PWM調節DCDC參數計算原理

深度解析:RTC電路上的32.768KHz時鐘的頻偏及測試

PCB Layout設計中的3W原則、20H原則和五五原則詳解

各種協議標準免費下載

審核編輯 黃宇

-

運放

+關注

關注

47文章

1163瀏覽量

53062 -

比較器

+關注

關注

14文章

1650瀏覽量

107185

發布評論請先 登錄

相關推薦

滯回比較器的閾值電壓如何確定?

什么是滯回比較器,及滯回閾值參數計算

什么是滯回比較器,及滯回閾值參數計算

評論