在數據中心和通信應用中,48伏特的配電系統相當普遍,許多方案用于將48V降至中間電壓軌道。最簡單的方法是使用降壓拓撲,它可以提供高性能,但往往在功率密度方面表現不足。升級多相降壓轉換器并采用耦合電感器,能夠顯著提高功率密度,使其與最先進的替代品相媲美,同時保持巨大的性能優勢。

多相耦合電感器在繞組之間具有反向耦合,能夠在每個相的電流中實現電流紋波的消除。這一優勢可以用于提高效率,或者在減小尺寸和提高功率密度之間進行權衡。

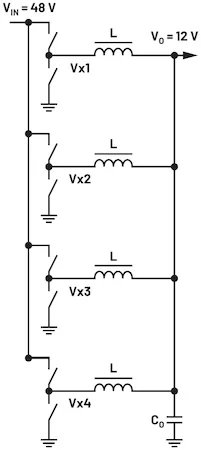

48V配電軌通常會降至某個中間電壓,通常為12V或更低。然后,不同的本地負載調節器直接向不同的負載提供不同的電壓。將48V降至12V的降壓電壓調節器的首選方案之一是多相降壓轉換器(見圖1)。該方案具有穩定的輸出電壓和快速的瞬態響應,簡單且成本低廉。對于幾百瓦到超過1千瓦的功率范圍,可以考慮采用四個并行相。然而,由于高效率通常是優先考慮的因素,因此48V轉換器的開關頻率往往相對較低,以降低開關損耗,相比于輸入電壓為12V甚至5V的低壓應用。這對磁性元件造成了雙重影響,因為已經顯著的電壓也在相對較長的時間內施加。因此,48V的磁性元件通常較為龐大,采用多圈繞組以承受相比于低壓應用顯著增加的電壓×時間。48V降壓轉換器仍然可以實現高效率,但通常整體尺寸較大,電感器占據了大部分體積。

基礎的48V至12V約1kW的降壓轉換器具有四個6.8μH的離散電感器,并以200kHz的頻率開關。這四個電感器是最大的組件,占據了解決方案的大部分體積。

圖1

圖1

電流紋波

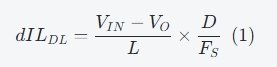

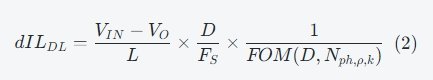

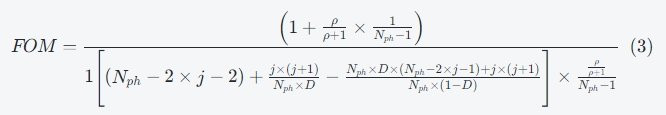

傳統降壓轉換器每個相的電流紋波可通過方程1計算,其中占空比D = VO/VIN,VO為輸出電壓,VIN為輸入電壓,L為電感值,Fs為開關頻率。

將離散電感器(DL)替換為具有漏電感Lk和互感Lm的耦合電感器1–7,耦合電感器的電流紋波可以表示為方程2。FOM(性能指標)如方程3所示,其中Nph為耦合相數,ρ為耦合系數(方程4),j為運行索引,僅定義了占空比的適用區間(方程5)。

耦合電感器考慮事項

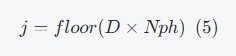

改進的第一步是繪制Nph = 4的FOM圖,針對多個實際合理的耦合系數Lm/Lk值(見圖2)。紅色曲線Lm/Lk = 0代表離散電感器的FOM = 1基線。研究表明,具有非常低漏電的凹槽CL(NCL)結構一般可以實現非常高的Lm/Lk,從而獲得高值的FOM。然而,盡管理想情況下感興趣的占空比恰好在第一個凹槽D = 12V/48V=0.25,但有必要考慮VIN和VO的一些范圍。有時,標稱VIN可以是48V或54V加上某些公差,VO可以調節遠離12V等。為了在占空比在D = 0.25的某個范圍內變化時保持電流紋波在可控范圍內,選擇了具有顯著漏電的典型CL設計,而不是NCL,仍保持顯著的FOM值。假設Lm/Lk > 4,可以考慮從圖2中的FOM獲得約6倍的收益,以減少CL中的電感值,相較于DL基線。減少儲能應直接影響所需的磁性體積。因此,將DL = 6.8μH的值降低到CL = 1.1μH將對尺寸減小有所裨益。

圖2

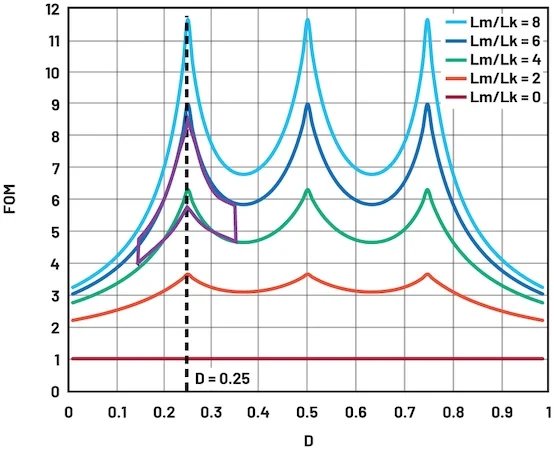

圖2相應的電流紋波繪制在圖3中,比較了基線設計DL = 6.8μH與提議的4相CL = 4 × 1.1μH(Lm = 4.9μH)在VIN = 48V和Fs = 200kHz條件下的表現。在感興趣的區域,CL的電流紋波與DL的相似或更小。這表明所有電路波形的均方根值相似,因此導通損耗也是如此。在相同Fs下的相同紋波也意味著相同的開關損耗、柵驅動損耗等,這意味著兩個方案之間的效率應該非常相似(假設DL和CL的電感損耗貢獻相似,作為唯一差異)。

圖3

圖3設計的CL = 4 × 1.1μH如圖4所示,替代了四個DL = 6.8μH電感器。假設四個DL之間間隔0.5mm,每個DL的尺寸為28mm × 28mm × 16mm:4相CL的尺寸為56.5mm × 18mm × 12.6mm,實現了磁性元件體積的4倍減小。

圖4

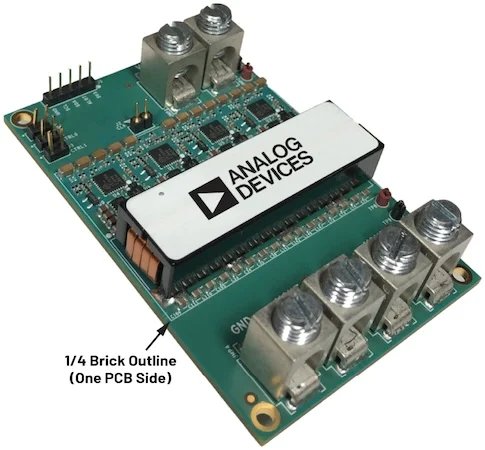

圖4完整的1.2kW 48V至12V調節解決方案如圖5所示。CL的尺寸和外形設計旨在適應兩個CL零件放入行業標準的四分之一磚形尺寸內。將所有約1mm的組件(FET、控制IC、陶瓷電容等)放置在PCB的底面,使得1.2kW解決方案的尺寸為1/8磚形。

圖5

圖5性能提升

當將DL = 6.8μH電感器更換為CL = 4 × 1.1μH時,電感器中的電流斜率限制也提高了6倍,這對瞬態響應總是有幫助。除此之外,即使總的磁性體積減少了4倍,電感器的飽和額定值在100°C時也提高了約2倍。

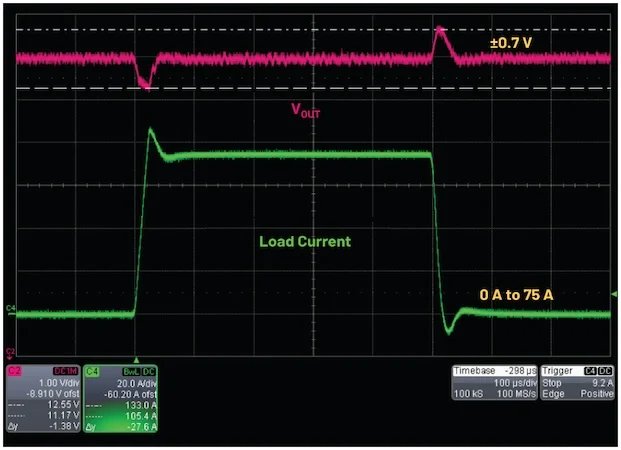

所提議的VIN = 48V、VO = 12V輸出的瞬態性能如圖6所示。正如預期的那樣,反饋將輸出電壓調節至預設值,以應對負載電流的變化,補償輸入電壓的任何變化。

圖6

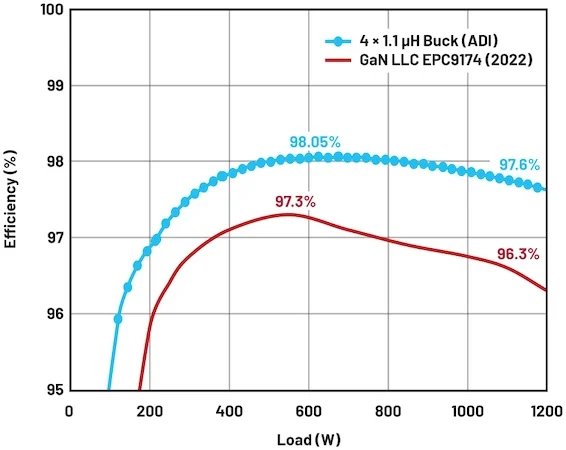

圖6也許最重要的性能參數是實現的效率,如圖7所示。它與行業最新的解決方案進行了比較:48V至12V(固定4:1降壓)LLC,使用矩陣變壓器和GaN FETs,分別在主側和副側。比較實現的滿載效率為97.6%,而基準值為96.3%。這意味著在滿功率下,損耗減少了16.6W,達到了提議解決方案的1.6倍改善。當效率已經很高時,這種損耗減少通常是很難實現的。

圖7

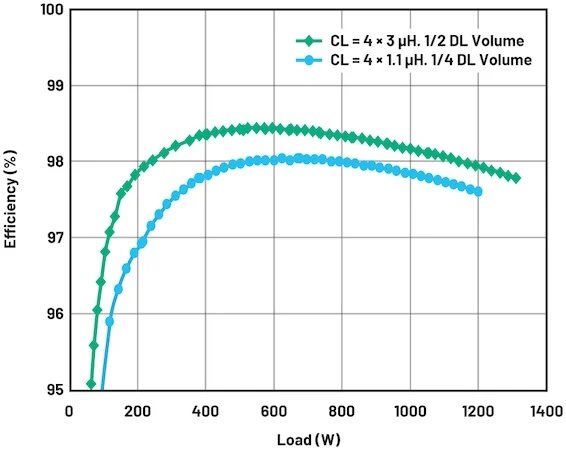

圖7在大小和效率之間的權衡顯然是可能的。圖8比較了CL = 4 × 1.1μH(相比于DL減少4倍的磁性體積)與更大CL = 4 × 3μH(僅減少2倍的電感體積)的效率。物理上更大的CL = 4 × 3μH的漏電感Lk為3μH,互感Lm為10μH。這使得Fs可以適度降低到110kHz,使效率在整個負載范圍內顯著提高。

圖8

圖8總結

利用耦合電感器的優勢,48V到12V的解決方案將總磁性體積從基本的離散電感器減少了4倍,達到了行業標準的1/8磚形體積。這一4倍的磁性體積減小是在保持出色的效率性能的同時實現的,瞬態電感電流斜率提高了6倍,電感器的Isat額定值提高了2倍。

與同等體積的行業先進48V到12V解決方案相比,在滿功率下實現了約1.6倍的損耗減少。如果可接受較小的磁性體積減少,效率進一步提高。

同時,所提議的解決方案是完全調節的,并直接放置在客戶的主板上。它還利用標準的硅FET進一步優化成本。這與未調節的4:1 LLC相比,后者的所有GaNFET都作為一個單獨模塊制造,配備專門的多層PCB,布局敏感且嵌入矩陣變壓器。整體性能提升展示了ADI在直流-直流應用中耦合電感器專利技術的優勢。

-

電感器

+關注

關注

20文章

2334瀏覽量

70618 -

DCDC

+關注

關注

29文章

822瀏覽量

71380 -

功率密度

+關注

關注

0文章

90瀏覽量

16901 -

耦合電感器

+關注

關注

0文章

14瀏覽量

5480 -

GaN FET

+關注

關注

0文章

8瀏覽量

3759

發布評論請先 登錄

相關推薦

如何使用耦合電感器提高DC-DC應用中的功率密度?

如何使用耦合電感器提高DC-DC應用中的功率密度?

評論