引言

隨著人工智能(AI)和高性能計算(HPC)應(yīng)用的快速發(fā)展,半導(dǎo)體產(chǎn)業(yè)正面臨挑戰(zhàn)與機遇。計算能力、內(nèi)存帶寬和能源效率需求的持續(xù)提升,使得半導(dǎo)體制程不斷挑戰(zhàn)性能極限。在這個背景下,先進封裝技術(shù)已經(jīng)發(fā)展成為延續(xù)摩爾定律、推動半導(dǎo)體產(chǎn)業(yè)創(chuàng)新的核心策略。這項技術(shù)不僅能夠提升芯片性能,還能實現(xiàn)更低的功耗和更小的外形尺寸,為AI和HPC應(yīng)用提供了強有力的技術(shù)支持[1]。

市場分析與發(fā)展趨勢

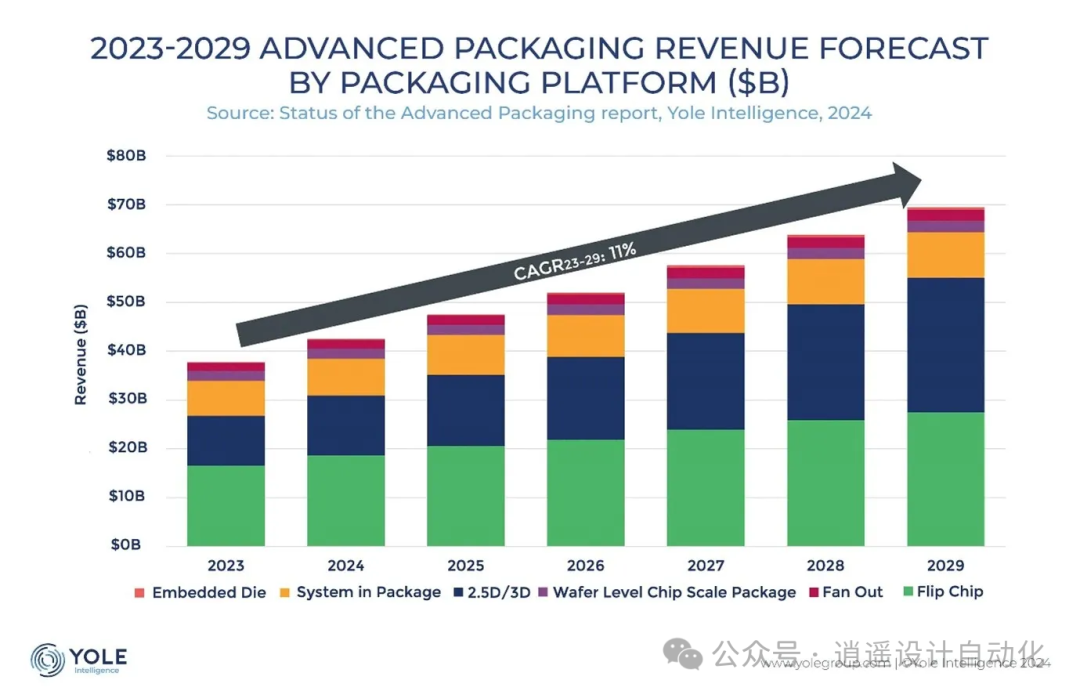

根據(jù)Yole Group的最新市場調(diào)查報告,2023年全球先進封裝市場規(guī)模達到392億美元,預(yù)計到2029年將大幅增長至811億美元,年復(fù)合增長率(CAGR)高達12.9%。在整體IC封裝市場中,先進封裝已占據(jù)44%的份額,其中AI和HPC應(yīng)用的比重正在穩(wěn)步提升。這一快速增長主要得益于數(shù)據(jù)中心、邊緣計算、自動駕駛等新興應(yīng)用領(lǐng)域?qū)Ω咝阅苄酒耐⑿枨蟆L貏e是在生成式AI的推動下,對高性能計算和大規(guī)模并行處理能力的需求進一步提升,加速了先進封裝技術(shù)的發(fā)展。

圖1:先進封裝市場增長趨勢(source: Yole Group)

2023年,全球半導(dǎo)體領(lǐng)域的先進封裝資本支出約為99億美元。英特爾與臺積電并列投資第一,各約投入32億美元,占總投資的31%。三星緊隨其后,投資約18億美元,占比20%。隨著市場需求的持續(xù)增長,2024年的投資規(guī)模預(yù)計將增加20%,達到119億美元。這些投資主要用于擴充產(chǎn)能和技術(shù)研發(fā),以滿足市場對先進封裝產(chǎn)品日益增長的需求。

先進封裝技術(shù)體系

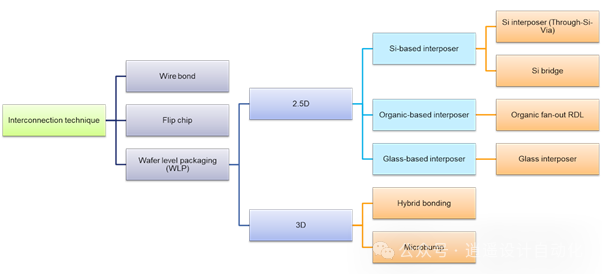

傳統(tǒng)的QFP、QFN等封裝技術(shù)在滿足基礎(chǔ)電子產(chǎn)品需求方面發(fā)揮著重要作用,但隨著AI和HPC應(yīng)用的發(fā)展,其性能限制日益顯現(xiàn)。先進封裝技術(shù)通過創(chuàng)新的設(shè)計和工藝,實現(xiàn)了更高的集成度、更短的互連距離,從而帶來顯著的性能提升和功耗優(yōu)化。目前,WLCSP(晶圓級芯片尺寸封裝)技術(shù)通過扇出型封裝(FOWLP)實現(xiàn)了更靈活的設(shè)計方案。其重分布層(RDL)技術(shù)允許芯片具有更多的輸入輸出選項,同時保持較小的封裝尺寸。

圖2:主要先進封裝技術(shù)(source: IDTechEx)

2.5D堆疊技術(shù)采用創(chuàng)新的中介層設(shè)計,實現(xiàn)了芯片間的高效互連。該技術(shù)主要通過硅中介層、硅橋接和RDL三種方式實現(xiàn)。其中硅中介層采用TSV技術(shù)實現(xiàn)電氣連接,代表產(chǎn)品如臺積電的CoWoS-S;硅橋接技術(shù)使用更少的硅材料,具有更薄、功耗更低的特點,如英特爾的EMIB和臺積電的CoWoS-L;而RDL則通過微影制程提升速度和散熱效果,適用于CoWoS-R等產(chǎn)品。

3D堆疊技術(shù)則通過垂直方向的創(chuàng)新設(shè)計,實現(xiàn)了計算單元與內(nèi)存之間的最短互連距離。該技術(shù)主要包括使用微凸塊的TSV技術(shù)和無凸塊的混合鍵合技術(shù)。TSV技術(shù)通過硅通孔實現(xiàn)垂直互連,顯著提升了數(shù)據(jù)傳輸效率;而混合鍵合技術(shù)則通過結(jié)合介電材料和嵌入金屬,進一步優(yōu)化了互連性能。同時,光電共封裝(CPO)技術(shù)作為新一代封裝解決方案,在傳輸損耗、抗干擾能力、帶寬容量和能效比方面都展現(xiàn)出顯著優(yōu)勢。

主要廠商技術(shù)布局

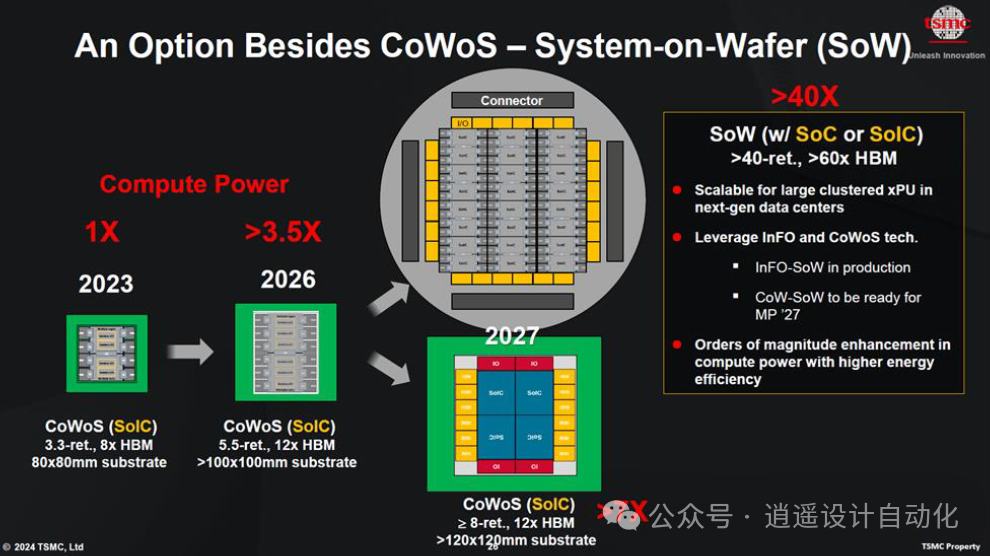

臺積電在先進封裝領(lǐng)域構(gòu)建了完整的技術(shù)體系,其3DFabric平臺包括前端3D芯片堆疊SoIC技術(shù)和后端CoWoS系列解決方案及InFO封裝技術(shù)。通過CoWoS-S實現(xiàn)量產(chǎn)后,公司計劃在2027年推出更先進的12個HBM堆疊的CoWoS解決方案。同時,臺積電正在全球范圍內(nèi)擴建先進封裝產(chǎn)能,包括在臺灣建設(shè)新的先進封裝廠,以及與Amkor合作在美國亞利桑那州提供先進封裝服務(wù)。

圖3:臺積電SoW封裝技術(shù)(source: 臺積電)

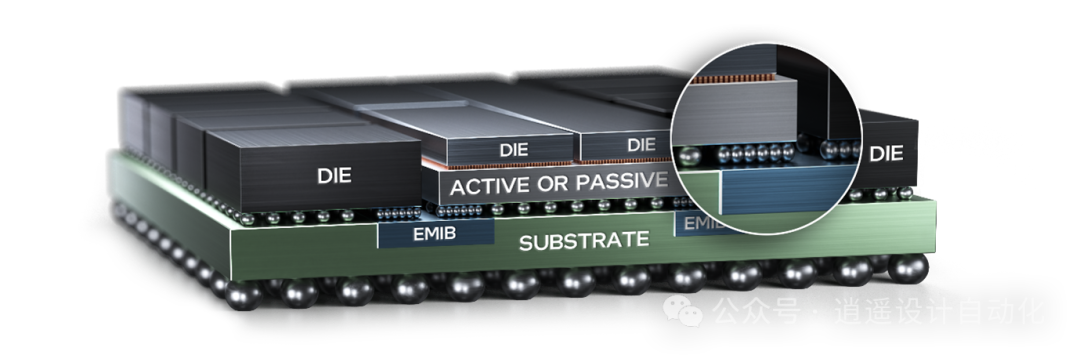

英特爾在先進封裝領(lǐng)域投入巨大,開發(fā)了EMIB、Foveros等創(chuàng)新技術(shù)。EMIB技術(shù)通過直接在有機基板中插入硅橋,避免了使用硅中介層與TSV的需求,有效減少了封裝尺寸和信號失真。Foveros技術(shù)則支持2.5D與3D堆疊,采用TSV與硅中介層,特別適用于客戶端與邊緣應(yīng)用場景。在新材料應(yīng)用方面,英特爾正在推進玻璃基板技術(shù)的研發(fā),這項技術(shù)可以提供更高的互連密度,將頻寬從224G提升至448G。公司計劃在2030年前實現(xiàn)玻璃基板的量產(chǎn),這將為封裝技術(shù)帶來革命性的突破。

圖4:英特爾EMIB技術(shù)(source: 英特爾)

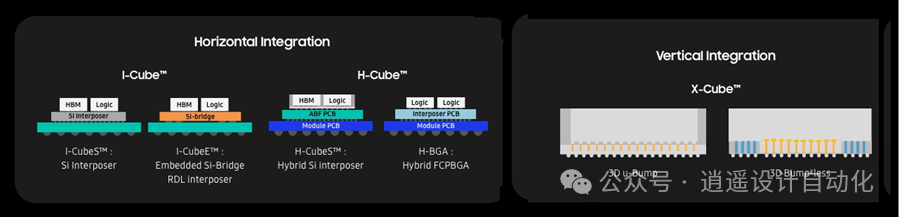

三星則充分利用其在存儲器、邏輯芯片和晶圓代工領(lǐng)域的優(yōu)勢,開發(fā)了全面的先進封裝解決方案。其I-Cube平臺基于TSV和后段制程技術(shù),支持2.5D和3D封裝,實現(xiàn)了異質(zhì)芯片的高效整合。H-Cube方案專門針對HBM集成設(shè)計,采用混合基板技術(shù),確保了供電穩(wěn)定性。而采用7納米制程的X-Cube技術(shù),通過TSV堆疊SRAM和邏輯芯片,顯著提升了數(shù)據(jù)傳輸速度。

圖5:三星先進封裝技術(shù)(source: 三星)

技術(shù)趨勢與未來展望

邊緣AI的發(fā)展正在成為推動半導(dǎo)體產(chǎn)業(yè)增長的新動力。通過將Chiplet技術(shù)與邊緣計算相結(jié)合,在采用2.5D堆疊靠近計算單元的同時,使用50~12納米的成熟制程并結(jié)合混合鍵合封裝技術(shù),實現(xiàn)了性能優(yōu)化和成本控制的平衡。這種方案不僅降低了制造成本,還優(yōu)化了能源效率,同時提高了產(chǎn)品良率。

半導(dǎo)體產(chǎn)業(yè)各環(huán)節(jié)之間的協(xié)作也日益緊密。芯片整合商與材料供應(yīng)商的深度合作,工具供應(yīng)商提供的專業(yè)解決方案,以及HBM/基板產(chǎn)業(yè)的協(xié)同發(fā)展,共同推動著3D IC技術(shù)的進步。這種全產(chǎn)業(yè)鏈的協(xié)作不僅加快了新工藝和新材料的應(yīng)用,也促進了產(chǎn)業(yè)標(biāo)準(zhǔn)的制定。

結(jié)論

隨著摩爾定律面臨物理極限,先進封裝技術(shù)已經(jīng)成為推動半導(dǎo)體產(chǎn)業(yè)創(chuàng)新的核心力量。在全球科技企業(yè)的持續(xù)投入下,創(chuàng)新的封裝技術(shù)不斷突破技術(shù)邊界,為AI與HPC等高性能應(yīng)用提供了強大的硬件支持。這種創(chuàng)新不僅推動了半導(dǎo)體產(chǎn)業(yè)的發(fā)展,也為數(shù)字技術(shù)的未來進步提供了新的可能。通過產(chǎn)業(yè)鏈各環(huán)節(jié)的緊密協(xié)作,先進封裝技術(shù)將繼續(xù)引領(lǐng)半導(dǎo)體產(chǎn)業(yè)的創(chuàng)新發(fā)展,推動全球數(shù)字化轉(zhuǎn)型進程。

參考來源

[1] S. Hong, "AI時代關(guān)鍵推手——先進封裝開啟摩爾定律新篇章," EE Times Taiwan, Nov. 25, 2024. [Online]. Available: https://www.eettaiwan.com/magazine/202411/ (accessed Dec. 7, 2024).

END

軟件申請我們歡迎化合物/硅基光電子芯片的研究人員和工程師申請體驗免費版PIC Studio軟件。無論是研究還是商業(yè)應(yīng)用,PIC Studio都可提升您的工作效能。

-

AI

+關(guān)注

關(guān)注

87文章

30805瀏覽量

268942 -

先進封裝

+關(guān)注

關(guān)注

2文章

403瀏覽量

245

原文標(biāo)題:先進封裝,AI時代的核心技術(shù)發(fā)展與創(chuàng)新

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

直流高壓電源技術(shù)發(fā)展淺析

人工智能半導(dǎo)體及先進封裝技術(shù)發(fā)展趨勢

節(jié)能回饋式負(fù)載技術(shù)創(chuàng)新與發(fā)展

《AI for Science:人工智能驅(qū)動科學(xué)創(chuàng)新》第二章AI for Science的技術(shù)支撐學(xué)習(xí)心得

《AI for Science:人工智能驅(qū)動科學(xué)創(chuàng)新》第一章人工智能驅(qū)動的科學(xué)創(chuàng)新學(xué)習(xí)心得

AI網(wǎng)絡(luò)物理層底座: 大算力芯片先進封裝技術(shù)

開啟全新AI時代 智能嵌入式系統(tǒng)快速發(fā)展——“第六屆國產(chǎn)嵌入式操作系統(tǒng)技術(shù)與產(chǎn)業(yè)發(fā)展論壇”圓滿結(jié)束

AI網(wǎng)絡(luò)發(fā)展的四大核心技術(shù)支柱

平衡創(chuàng)新與倫理:AI時代的隱私保護和算法公平

半導(dǎo)體先進封裝技術(shù)

邊緣AI核心技術(shù)和產(chǎn)業(yè)鏈!技術(shù)持續(xù)進步,應(yīng)用不斷拓展!

先進封裝成為AI時代的核心技術(shù)發(fā)展與創(chuàng)新

先進封裝成為AI時代的核心技術(shù)發(fā)展與創(chuàng)新

評論