在當今科技迅猛發展的時代,半導體芯片的創新已成為推動各行各業,尤其是汽車行業進步的關鍵力量。隨著智能駕駛技術的興起,對高性能芯片的需求正迅速增長。

7月27日,蔚來汽車公司在NIO IN創新科技日上宣布了一項重大突破:他們成功流片了全球首顆5納米工藝的車規級智能駕駛芯片——“神璣NX9031”。這一成就不僅標志著蔚來在芯片設計領域的突破,也預示著即將到來的測試和驗證階段。一旦性能和質量達到設計要求,這款芯片將進入大規模量產,并最終實現商用,為蔚來汽車的智能駕駛技術提供強大動力。

“神璣NX9031”芯片的成功流片,不僅展現了蔚來在自主研發和技術創新方面的強大實力,而且推動了汽車芯片國產化的進程,為全球汽車產業的發展貢獻了中國智慧和中國力量。預計在2025年第一季度,這款芯片將首次搭載在蔚來的旗艦轎車ET9上,為智能駕駛技術的發展開啟新的篇章。

芯片流片(Tape Out)技術是半導體制造中的核心環節,將設計圖案精確轉移至硅片上,是設計與生產的關鍵橋梁。本文全面探討了芯片流片技術,從設計、流片準備到技術實施、設備與材料應用,分析了流片過程中的關鍵環節與挑戰。研究發現,芯片流片的成功直接影響芯片設計的可制造性和市場競爭力,設計復雜度和成本控制是主要挑戰。為應對這些挑戰,建議采用高效設計工具、優化工藝參數和材料選擇等策略。

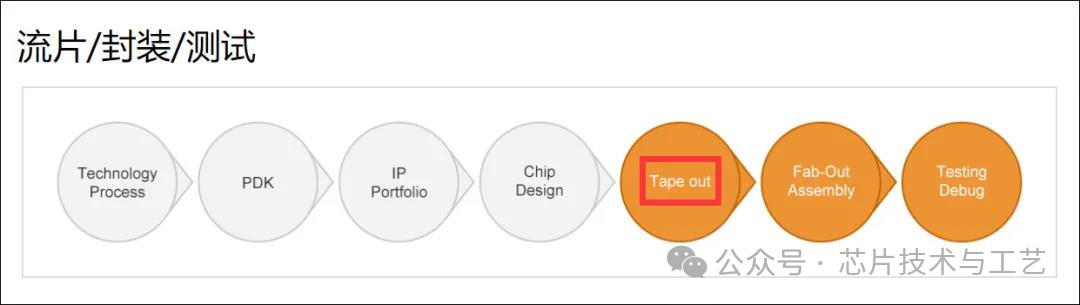

| 階段 | 詳細解釋 |

|

Technology Process (技術工藝) |

選擇和定義芯片制造所需的工藝技術。工藝技術包括晶體管的尺寸、材料的選擇以及制造流程的詳細規范。不同的工藝技術適用于不同類型的芯片,如高性能處理器、低功耗設備等。 |

|

PDK (Process Design Kit,工藝設計套件) |

為芯片設計人員提供的一組工具和文件,包含工藝技術的詳細信息、設計規則和驗證方法。設計人員使用PDK來確保他們的設計符合制造工藝的要求,保證芯片能夠正確制造。 |

|

IP Portfolio (知識產權庫) |

包括預先設計和驗證的功能模塊(如處理器核心、存儲器模塊、接口電路等)。設計人員可以使用這些模塊來加速芯片設計過程,并減少設計中的風險和錯誤。 |

|

Chip Design (芯片設計) |

根據需求和PDK中的規范進行芯片的詳細設計。設計包括邏輯設計、物理設計和電路布局等。設計完成后,需要進行仿真和驗證,以確保芯片功能和性能符合要求。 |

|

Tape Out (流片) |

將最終設計的芯片版圖數據提交給制造廠商進行生產。這是芯片制造流程中的重要里程碑,意味著設計階段的結束和制造階段的開始。 |

|

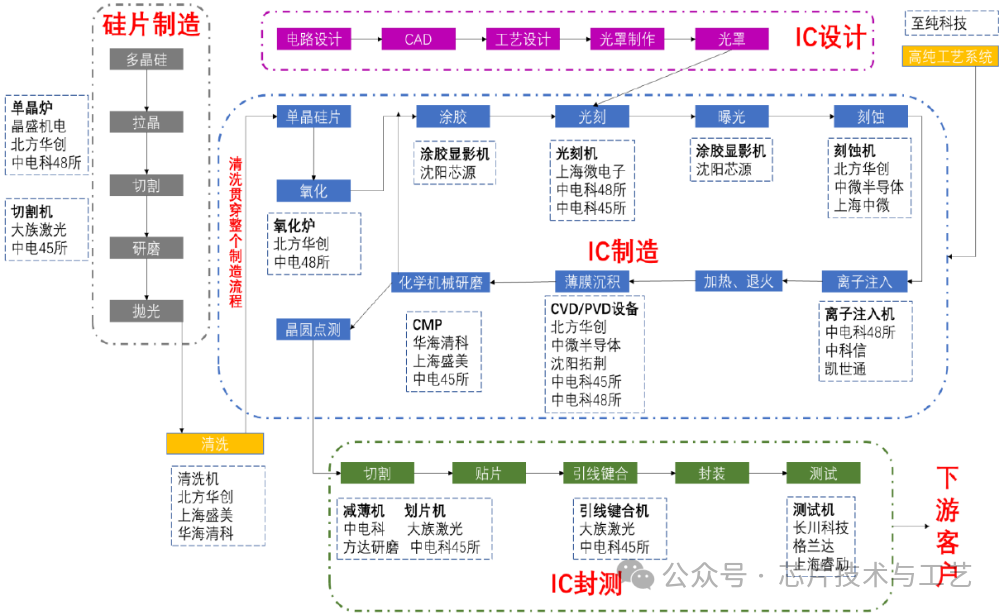

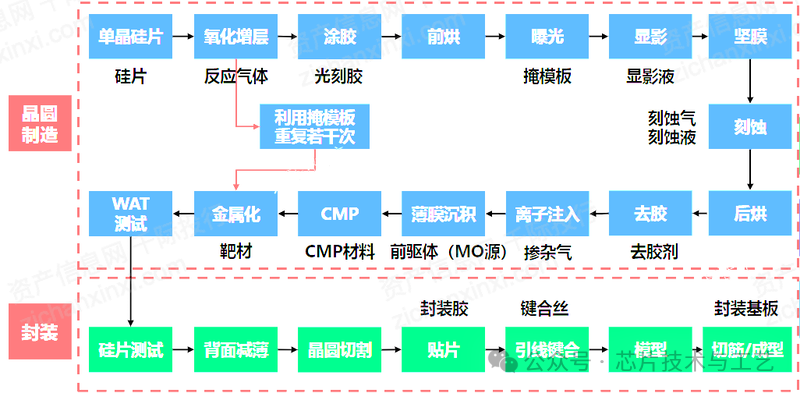

Fab-Out Assembly (晶圓制造和封裝) |

包括晶圓制造和芯片封裝。晶圓制造過程涉及一系列復雜的工藝步驟,如光刻、刻蝕、離子注入等。制造完成后,晶圓被切割成單個芯片,然后進行封裝,以保護芯片并提供電氣連接。 |

|

Testing Debug (測試和調試) |

制造和封裝完成后,芯片進入測試和調試階段。測試包括功能測試、性能測試和可靠性測試,確保芯片在各種條件下都能正常工作。如果發現問題,需要進行調試和修復。 |

此外,文章展望了芯片流片技術的市場應用與未來趨勢,指出其在消費電子、通信、汽車和醫療等領域的廣泛應用前景,以及技術進步帶來的高精度、低成本流片需求的持續增長。

#01

引 言

1.1 芯片流片的定義

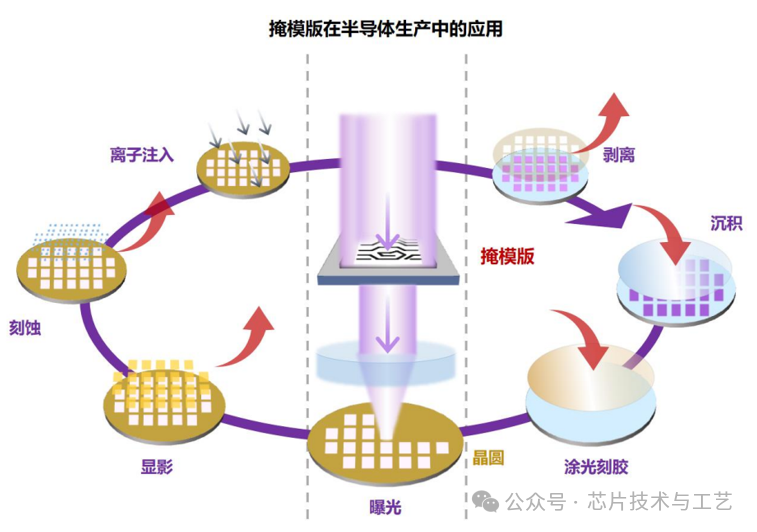

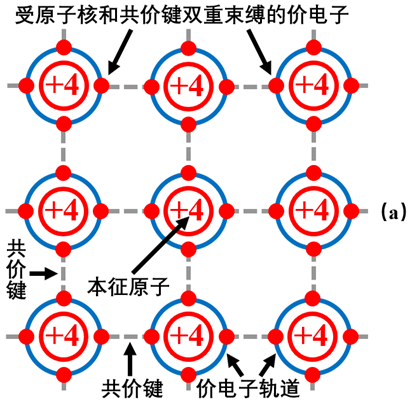

芯片流片是半導體制造中的關鍵環節,指將設計好的芯片圖案從計算機數據轉化為實際硅片上的物理結構的過程。這個過程包含光刻、刻蝕、離子注入、金屬沉積等精密工藝,確保在硅片上精確構建設計的集成電路。

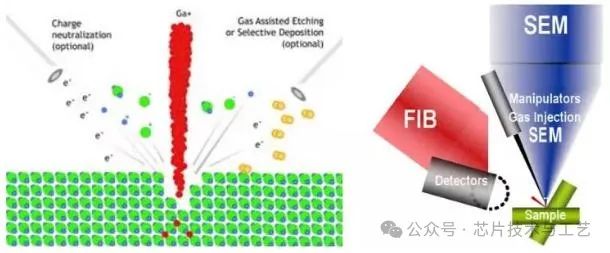

芯片流片不僅是連接設計與生產的橋梁,還需要嚴格的質量控制,以保證最終產品的性能和可靠性。任何工藝失誤可能導致芯片失效,因此對工藝精度和操作環境的要求極高。有時需要通過聚焦離子束(FIB)編輯技術對芯片進行物理修改,以糾正設計錯誤或滿足客戶需求,從而減少研發成本和時間。

*聚焦離子束(Focused Ion Beam, FIB)技術是一種利用高能離子束進行微觀加工和分析的技術。

| 項目 | 詳細解釋 |

| 技術原理 | 聚焦離子束技術使用高能離子束(通常是Ga+離子)聚焦在樣品表面,通過離子的物理撞擊和濺射作用,對樣品進行納米級的加工和分析。 |

| 主要組成部分 |

1. 離子源:產生高能離子束,常用的是液態金屬離子源(LMIS)。 2. 聚焦系統:使用電場和磁場將離子束聚焦到樣品表面。 3. 樣品臺:用于固定和移動樣品,實現對特定區域的加工和分析。 |

| 應用領域 |

1. 半導體制造:用于電路修復、故障分析和截面制作。 2. 材料科學:用于納米級加工、材料表面改性和截面分析。 3. 生命科學:用于生物樣品的精細加工和分析。 |

| 主要功能 |

1. 納米加工:通過精確控制離子束,可以在樣品表面進行納米級的雕刻和切割。 2. 截面制備:用于制作樣品的精細截面,方便后續的顯微分析。 3. 元素分析:結合能量色散X射線光譜(EDX),可進行元素成分分析。 |

| 優勢 |

1. 高精度:能夠進行納米級的加工和分析。 2. 多功能:集成了加工、分析和成像功能。 3. 非接觸:離子束與樣品無直接接觸,避免了機械損傷。 |

| 局限性 |

1. 損傷效應:高能離子束可能會對樣品產生損傷和污染。 2. 材料選擇:某些材料對離子束的響應不佳,可能影響加工效果。 3. 成本高:設備和操作成本較高。 |

| 最新進展 | 近年來,聚焦離子束技術在高分辨率加工和無損分析方面取得了顯著進展。新的離子源材料和聚焦系統的改進,使得FIB的應用范圍不斷擴大,特別是在納米科技和生物醫學領域。 |

隨著半導體技術的進步,芯片流片工藝不斷創新。例如,微型立銑刀技術簡化了微通道芯片的制造流程,降低了生產成本。芯片流片的成功依賴多方面的技術合作,如中芯國際與燦芯半導體合作實現了40納米低漏電工藝的ARM Cortex-A9雙核測試芯片流片,展示了設計、制造與測試環節的緊密協作。

全球范圍內,芯片流片技術的應用案例層出不窮,如中國成功流片的首個自主研發5G微基站射頻芯片,體現了國內半導體制造技術的突破,并支持了5G通信技術的發展。

芯片流片技術在半導體制造中的重要性不可忽視。它不僅是實現芯片設計轉化為實際產品的關鍵環節,也是推動半導體行業技術創新和產業發展的核心動力。隨著技術的進步和市場需求的增長,芯片流片技術將繼續發揮其不可或缺的作用。

1.2 芯片流片的重要性

芯片流片在半導體制造中占據著重要地位,不僅是將芯片設計轉化為實際產品的關鍵環節,也是連接設計與生產的橋梁。以下是其重要性的幾個方面:

實現芯片設計落地:流片過程是將設計好的芯片圖案通過一系列精密制造步驟轉移到硅片上,形成具有特定功能的集成電路。流片的成功意味著設計的芯片可以順利轉化為市場上的實體產品,直接影響芯片產品的問世和市場競爭力。

工藝優化和成本控制:流片過程中的工藝優化和成本控制對芯片的市場競爭力至關重要。隨著半導體技術的發展,芯片制造的復雜性和成本也在上升。通過工藝優化可以降低生產成本,提高生產效率,從而使芯片產品更具市場競爭力。同時,嚴格的成本控制確保了芯片產品的盈利能力。

推動技術進步:流片技術的不斷進步為半導體行業的發展提供了有力支撐。隨著摩爾定律的推進,集成電路的集成度提高,對流片技術提出了更高的要求。采用更先進的制程技術、引入新材料和工藝,這些技術進步不僅提升了芯片產品的性能,還拓展了半導體行業的應用領域和市場空間。

總之,芯片流片不僅是實現芯片設計向產品轉化的關鍵環節,更是影響芯片市場競爭力和推動半導體行業持續發展的核心因素。提升流片技術水平和成功率,對促進半導體產業的繁榮和創新具有重要意義。

#02

芯片設計與流片準備

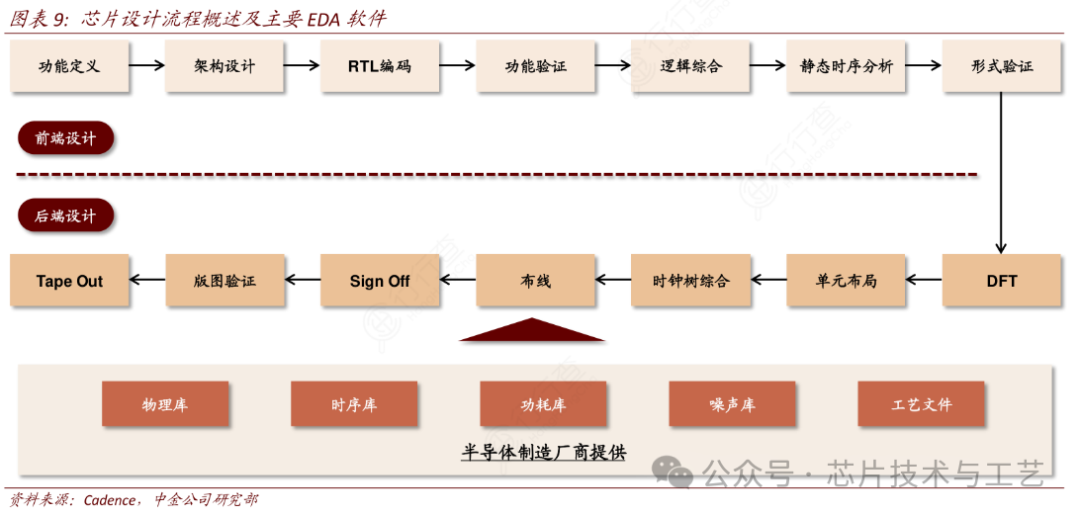

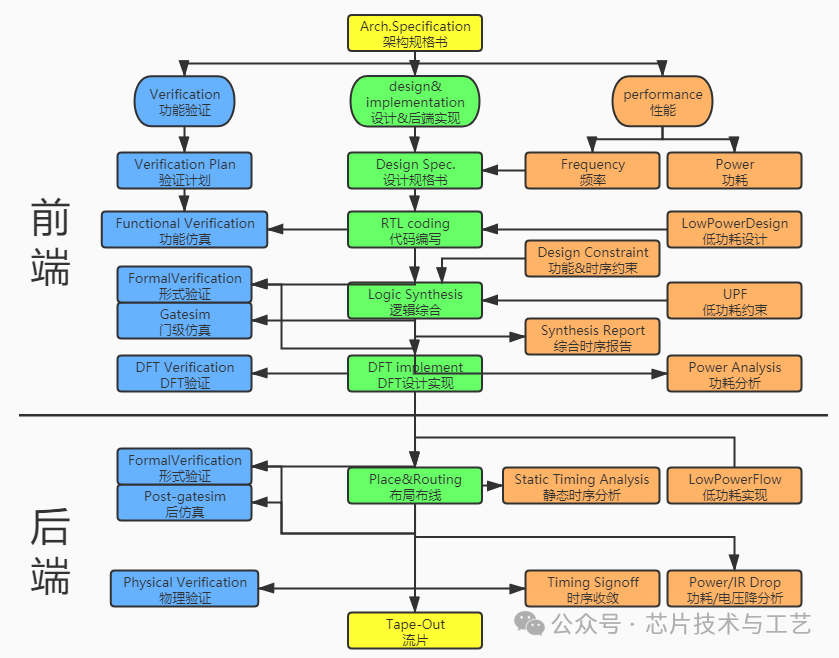

2.1 芯片設計流程

芯片設計流程是一個復雜且精細的過程,涵蓋從功能定義到物理版圖生成的多個環節,通常分為前端設計和后端設計兩大階段。

a.RTL設計,即寄存器傳輸級(Register Transfer Level)設計,是數字電路設計中的一個關鍵階段。在這個階段,設計師使用硬件描述語言(HDL),如Verilog或VHDL,來描述數字電路的行為和結構。

b.DFT(Design for Testability),即“可測試性設計”,是集成電路設計中的一個重要概念,旨在提高芯片的測試效率和準確性。

前端設計(Front End,也稱邏輯設計)是芯片設計的起始點,主要目標是定義芯片的功能和架構。在這一階段,設計團隊進行詳盡的需求分析,明確芯片需要實現的具體功能,并編寫RTL(寄存器傳輸級)代碼。RTL代碼描述了芯片內部的邏輯結構,包括數據通路和控制通路,以及各個組件之間的交互方式。為了確保設計的正確性,前端設計階段還會進行仿真驗證,通過模擬芯片在實際工作環境中的行為來檢查是否滿足設計要求。

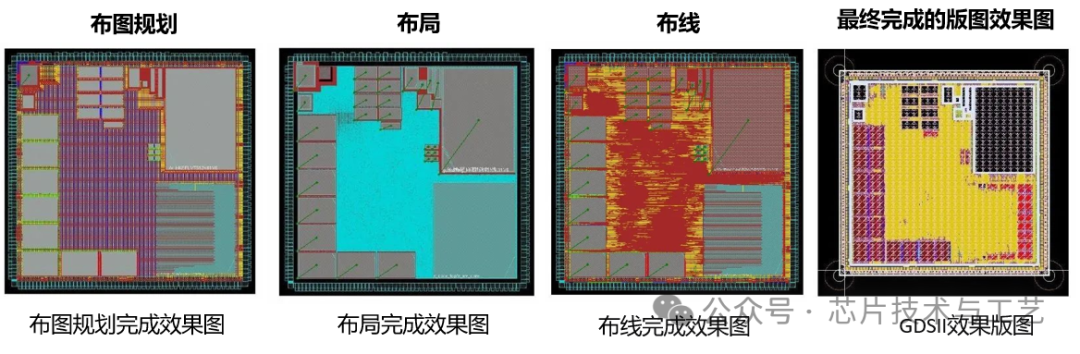

后端設計(Backend,也稱物理設計)在前端設計完成后展開,主要任務是將邏輯描述轉換為實際的物理版圖。后端設計人員進行布局規劃,確定各功能模塊在芯片上的位置,以優化性能和減少功耗。接著進入布線階段,確保信號能夠準確無誤地在各模塊之間傳遞。時序分析和信號完整性分析也是關鍵環節,確保芯片在各種工作條件下保持穩定性能。經過這些步驟,后端設計最終生成完整的物理版圖,為芯片制造奠定基礎。

前后端設計的緊密協作是確保芯片設計準確性和可靠性的關鍵。前端設計人員提供清晰、準確的邏輯描述,而后端設計人員將其轉換為高效的物理實現。整個設計流程中不斷的迭代和優化是必不可少的,以確保最終芯片產品滿足市場需求和性能指標。

總結而言,芯片設計流程通過前后端設計的緊密合作和不斷優化,實現從功能定義到物理版圖生成的轉化,確保最終芯片產品的性能和可靠性。

2.2 流片前準備

在芯片設計完成后,即進入緊張的流片前準備階段。這一階段的工作至關重要,因為它直接關系到芯片流片的成功與否。

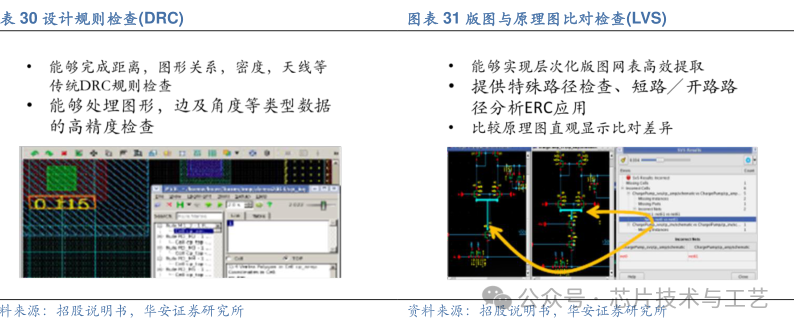

設計規則檢查(DRC):這是首要環節,目的是驗證設計是否滿足制造工藝的要求。例如,在布局布線過程中,必須確保所有設計元素符合制造廠規定的尺寸和間距規則,以避免潛在的制造問題。

版圖驗證(LVS):這一步驟通過對比設計版圖和原理圖來確保兩者一致,防止設計上的失誤或偏差。

寄生參數提取:由于導線電阻、電容等寄生參數的存在,芯片的實際性能可能會與設計預期產生偏差。因此,這一階段需要精確提取這些寄生參數,并在設計中進行相應的補償,以確保流片后的芯片性能符合預期。

與流片廠商的溝通:確定具體的工藝參數,如摻雜濃度、氧化層厚度等,這些都是影響芯片性能的關鍵因素。材料選擇也至關重要,不同材料的物理和化學特性直接影響芯片的性能和可靠性。

測試方案制定:決定如何對流片后的芯片進行全面的性能和可靠性測試,以確保芯片滿足設計要求。

| 類別 | 子類別 | 描述 |

|

前端設計 (Front-End Design) |

HDL編碼/原理圖設計 |

Verilog/HDL RTL Coding(Digital):使用硬件描述語言編寫寄存器傳輸級代碼。 Schematic input(Analog):使用原理圖輸入工具繪制電路圖。 |

| 前仿真驗證 | 使用仿真工具驗證RTL代碼或原理圖功能,確保設計滿足規格要求。 | |

| 邏輯綜合/靜態時序分析/形式驗證 |

邏輯綜合:HDL代碼轉門級網表。 靜態時序分析:分析電路時序特性。 形式驗證:數學方法證明設計滿足規范。 |

|

|

后端物理設計 (Back-End Design) |

物理布局布線 | 使用工具將門級網表轉物理布局并完成布線。 |

| 物理版圖驗證 | 檢查物理版圖是否符合設計規則和版圖與原理圖一致性。 | |

| 寄生參數提取 | 從物理版圖中提取寄生參數,影響電路性能。 | |

| 后仿真 | 考慮寄生參數,仿真設計性能。 | |

|

生產測試 (Manufacturing and Test) |

流片(tapeout) | 設計版圖送晶圓代工廠生產。 |

| 生產(Production) | 完成圓片生產后的切割、測試和分類。 | |

|

芯片封裝與測試 (Packaging and Testing) |

芯片封裝并進行功能和性能測試,確保質量標準。 |

流片前的準備工作涉及多個方面,需要設計團隊與制造廠商的緊密合作,確保每個環節都得到充分的驗證和優化。雖然這階段工作繁瑣且耗時,但它是確保芯片流片成功的關鍵所在。任何疏忽都可能導致流片失敗,進而造成巨大的經濟損失和時間浪費。因此,設計團隊必須高度重視這一階段的工作,確保每一項準備都細致入微,為后續的流片過程奠定堅實基礎。

#03

芯片流片技術詳解

3.1 設計檢查與版圖驗證

在進行芯片流片之前,設計檢查與版圖驗證是不可或缺的環節,這兩個步驟對于確保流片的成功至關重要。

設計規則檢查(DRC):這一過程的主要目的是對芯片版圖進行細致審查,確認其是否嚴格遵循制造工藝規則。這涵蓋了線寬、間距、層疊等關鍵參數的檢查。通過高精度的軟件工具,版圖可以自動掃描,識別任何可能違反制造工藝規則的設計元素。一旦發現違規行為,設計團隊會立即收到反饋并進行調整。預防性檢查機制顯著提高了芯片制造的良率,降低了因設計錯誤導致的生產風險。

版圖驗證(LVS):這一步驟確保芯片版圖與原始電路設計之間高度一致。驗證工具對照電路圖和版圖,逐一比對每個元件和連接關系,確保版圖精確反映電路設計的意圖,保證功能實現和性能表現達到預期標準。

設計檢查與版圖驗證并非一次性任務。在設計和流片過程中,這兩個步驟可能多次迭代進行,以確保設計的不斷完善和優化,每次修改都能通過嚴格的驗證流程。迭代式驗證方法提高了設計的可靠性,為后續的芯片測試和量產奠定堅實基礎。

隨著半導體技術進步,設計檢查與版圖驗證面臨的挑戰也在增加。芯片集成度提高,版圖中元件數量和復雜度增加,要求驗證工具具備更高處理能力和精度。同時,新材料的引入和工藝的創新對驗證流程提出新的要求。業界不斷投入研發力量,以開發更高效和精準的驗證工具和方法。

設計檢查與版圖驗證在芯片流片過程中占據舉足輕重的地位。它們不僅是確保芯片設計正確性和可制造性的關鍵步驟,也是推動半導體行業持續發展和技術創新的重要基石。通過不斷優化和完善這兩個驗證環節,可以為市場提供高性能、高可靠性的芯片產品,推動整個行業進步和發展。

3.2 版圖布線與光罩(掩模版)制作

版圖布線作為芯片設計的核心環節,其復雜性不言而喻。在這一過程中,設計者需要精心規劃每一條線路,確保其既能滿足功能需求,又能達到最佳的性能指標。

信號完整性:布線過程中必須考慮的重要因素之一,關系到芯片在實際運行中能否穩定、準確地傳輸信號。

時序問題:合理的時序設計能夠確保芯片在高速運行時不會出現時序混亂或信號延遲等問題。

功耗控制:現代芯片設計中越來越受關注的方面,有效的功耗管理不僅可以提高芯片的能效比,還能延長其使用壽命。

| 圖名 | 內容 | 備注 |

| 布圖規劃完成效果圖 |

最外一圈為I0PAD,是芯片與外界連接的接口。 圖中灰色和綠色的大模塊是主要IP。 圖中紅色和藍色的線是power stripe,用于連接整個芯片各個位置元件和模塊的電源信號和地信號,一般比較寬。 |

布圖規劃是整個后端流程中作重要的一步,但也是彈性最大的一步。因為沒有標準的最佳方案,但又有很多細節需要考量。 布局布線的目標:優化芯片的面積,時序收斂,穩定,方便走線。 |

| 布局完成效果圖 |

圖中灰色和綠色部分為主要IP。 其余藍色部分為standard cell(標準單元),通過軟件自動布局填充出來的效果。 其中軟件會自動留有合適的空間用于下一步的布線。 |

布局即擺放標準單元,I/O pad,宏單元來實現個電路邏輯。 布局目標:利用率越高越好,總線長越短越好,時序越快越好。 但利用率越高,布線就越困難;總線長越長,時序就越慢。因此要做到以上三個參數的最佳平衡。 |

| 布線完成效果圖 | 紅色和黃色的金屬線由軟件自動布在standard cell上。 | 布線是指在滿足工藝規則和布線層數限制、線寬、線間距限制和各線網可靠絕緣的電性能約束條件下,根據電路的連接關系,將各單元和I/O pad用互連線連接起來。 |

| GDSII效果版圖 |

與之前相比主要是為了完成時序要求和DRC、LVS要求,重新進行了部分區域的布局布線。" "加入了filler,即填充物以滿足設計規則中關于金屬層密度的要求。" |

Clock Tree Synthesis,時鐘樹綜合,簡單點說就是時鐘的布線。 由于時鐘信號在數字芯片的全局指揮作用,它的分布應該是對稱式的連到各個寄存器單元,從而使時鐘從同一個時鐘源到達各個寄存器時,時鐘延遲差異最小。這也是為什么時鐘信號需要單獨布線的原因。 LVS(Layout Vs Schematic)驗證:簡單說,就是版圖與邏輯綜合后的門級電路圖的對比驗證; DRC(Design Rule Checking):設計規則檢查,檢查連線間距,連線寬度等是否滿足工藝要求; ERC(Electrical Rule Checking):電氣規則檢查,檢查短路和開路等電氣規則違例; 實際的后端流程還包括電路功耗分析,以及隨著制造工藝不斷進步產生的DFM(可制造性設計)問題等。 物理版圖以GDSII的文件格式交給芯片代工廠(稱為Foundry)在晶圓硅片上做出實際的電路。 |

*來源:干貨 | 一顆芯片的從無到有-電子工程專輯 (eet-china.com)

在完成版圖布線后,接下來的光罩制作環節同樣至關重要。

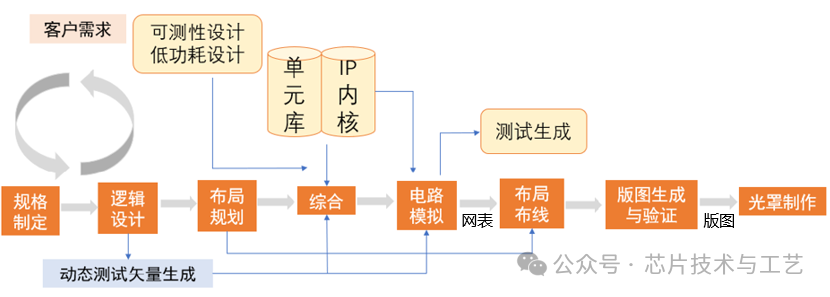

| 名詞 | 作用 |

| 客戶需求(Customer Requirements) | 定義芯片的功能、性能、接口、電源需求等詳細規格,為后續的設計工作提供指導。 |

| 可測性設計(Design for Testability, DFT) | 在設計階段就考慮電路的可測試性,以便在制造后能夠有效地檢測和診斷缺陷。 |

| 低功耗設計(Design for Low Power, DLP) | 在設計階段采用特定的技術來降低芯片的功耗,以滿足節能或電池壽命的要求。 |

| 動態測試矢量生成(Dynamic Test Vector Generation) | 在芯片制造后,生成用于測試芯片的動態測試矢量,這些矢量會在芯片的實際測試階段使用。 |

| 規格制定(Specification) | 定義芯片的功能、性能、接口、電源需求等詳細規格,為后續的設計工作提供指導。 |

| 單元庫和IP內核(Cell Library & IP Cores) | 提供了設計芯片所需的基本構建塊和預先設計好的、可重用的設計組件。 |

| 邏輯設計(Logic Design) | 使用硬件描述語言(HDL)編寫代碼,實現芯片的功能邏輯。 |

| 布局規劃(Floorplanning) | 確定芯片上各個模塊的位置和大小,以及它們之間的連接方式,為布局布線打下基礎。 |

| 綜合(Synthesis) | 將HDL代碼轉換成門級網表,這是將抽象的硬件描述轉換成具體電路表示的過程。門級網表(Gate-Level Netlist)詳細描述電路中的邏輯門及其連接方式,為物理設計和時序分析提供輸入。 |

| 電路模擬(Circuit Simulation) | 使用仿真工具對設計進行模擬,以驗證電路的功能和性能是否符合預期。 |

| 物理布局布線(Layout & Routing) | 將門級網表轉換成實際的物理布局,并完成布線,確保信號在芯片上的正確連接。 |

| 版圖生成與驗證(Mask Generation & Verification) | 生成用于制造芯片的光罩(掩模)圖案,并進行驗證,確保版圖與設計規格一致。 |

| 光罩制作(Mask Making) | 根據驗證后的版圖制作光罩,這些光罩將在后續的芯片制造過程中用于圖案轉移。 |

光罩(掩模版),作為將設計圖案從虛擬世界轉移到現實硅片的橋梁,其制作精度直接關系到芯片的最終質量。

| 下游應用市場 | 產品類型 | 產品應用領域 | 下游應用代表廠商 | 市場占比 |

| 半導體掩模版 | 邏輯電路制造、模擬電路制造、功率器件制造、MEMS傳感器制造、IC封裝等 | 半導體制造行業 | 臺積電、英特爾、中芯國際、華虹半導體、華潤微、中芯集成、士蘭微、積塔半導體、比亞迪半導體、立昂微、燕東微、高德紅外、長電科技等 | 60% |

| 平板顯示掩模版 | LCD顯示屏制造、OLED顯示屏制造等 | 顯示技術行業 | 京東方、天馬微電子、華星光電、中電熊貓、惠科等 | 28% |

| 電路板(PCB、FPC)制造、觸控屏(TP)制造、光學器件制造等 | 電路板制造、觸控屏制造、光學器件制造等 | 電子制造行業 | 藍思科技、紫翔電子等 | 12% |

注:掩模版下游應用市場占比數據來源于SEMI、Omdia。其中,半導體掩模板數據統計的為獨立第三方半導體掩模版市場規模,不包括晶圓廠自行配套的掩模版市場規模。

*來源:什么是掩模版?掩模版(光罩MASK)—半導體芯片的母板設計-電子發燒友網 (elecfans.com)

光刻技術在這一環節中發揮著關鍵作用,它利用光的衍射和干涉原理,將版圖上的精細圖案精確地投影到硅片上。隨后,通過蝕刻等工藝步驟,將這些圖案轉化為實際的物理結構,從而完成芯片的制作。

隨著半導體技術的不斷發展,版圖布線和光罩制作所面臨的挑戰也在日益加劇。

布線密度和復雜度增加:隨著芯片集成度的不斷提高,給設計者帶來了巨大的挑戰。

光罩制作的精度和效率要求提高:隨著市場對芯片性能要求的不斷提升,光罩制作面臨著更高的要求。

因此,不斷探索和創新成為了推動這兩個環節技術進步的關鍵動力。

總的來說,版圖布線和光罩制作是芯片流片過程中不可或缺的環節,它們的技術水平和實施效果直接關系到芯片的最終性能和質量。因此,在半導體制造領域,對這兩個環節的研究和優化一直是一個熱點和難點問題。未來,隨著新技術的不斷涌現和應用,我們有理由相信,這兩個環節將會迎來更多的突破和創新,為半導體行業的發展注入新的活力。

#04

設備與材料

4.1 關鍵設備

在芯片流片過程中,關鍵設備扮演著至關重要的角色。這些設備不僅保證了流片過程的順利進行,還直接影響著芯片的質量和性能。

光刻機:作為流片過程中的核心設備,其精度和穩定性對芯片圖形的轉移質量有著決定性的影響。現代光刻機采用先進的光學系統和精密的機械結構,能夠將版圖圖案以極高的分辨率投影到硅片上,從而實現微細圖形的精確刻畫。光刻機還配備先進的對準系統,確保每一次曝光都能準確無誤地與硅片上的已有圖形對齊,保證芯片結構的準確性和一致性。

蝕刻設備:在流片過程中,蝕刻設備通過化學或物理方法去除硅片表面的特定材料,形成所需的溝槽、孔洞或微細結構。蝕刻設備的性能直接影響芯片的尺寸精度和表面粗糙度,進而影響芯片的電學性能和可靠性。在選擇蝕刻設備時,需要充分考慮其蝕刻速率、選擇性、均勻性以及對硅片表面的損傷程度等因素。

沉積設備:用于在硅片表面沉積各種薄膜材料的關鍵設備。這些薄膜材料包括金屬、氧化物、氮化物等,它們在構建芯片的內部結構和實現特定功能方面發揮著重要作用。沉積設備的性能直接影響薄膜材料的成分、結構、厚度以及均勻性,從而影響芯片的性能和穩定性。在選擇沉積設備時,需要考慮其沉積速率、成分控制、厚度均勻性以及工藝穩定性等因素。

除了上述關鍵設備外,芯片流片過程中還涉及到許多其他輔助設備和工藝步驟,如清洗設備、檢測設備等。這些設備和工藝步驟共同構成了一個完整的流片生產線,確保了芯片從設計到實際產品的順利轉化。

總的來說,關鍵設備在芯片流片過程中發揮著舉足輕重的作用。它們的性能和穩定性不僅影響著流片過程的順利進行,還直接決定著芯片的質量和性能。因此,在半導體制造行業中,對關鍵設備的研發和優化一直是一個重要的研究方向。通過不斷提升設備的性能和穩定性,可以進一步提高芯片流片的成功率和產品良率,從而推動整個半導體行業的持續發展和創新。

4.2 材料使用

在芯片流片過程中,材料的選擇和使用是至關重要的環節。不同的材料具有不同的物理和化學性質,這些性質直接影響著芯片的性能和可靠性。因此,對材料的精心挑選和嚴謹使用是確保芯片流片成功的關鍵。

光刻膠:作為芯片制造中的核心材料之一,其性能直接關系到圖形轉移的精度和分辨率。優質的光刻膠應具有良好的光敏性、粘附性和耐腐蝕性,以確保在光刻過程中能夠精確地形成所需的圖形掩膜。同時,光刻膠的去除也需要精確控制,以避免對硅片表面造成損傷或殘留。

蝕刻氣體:在芯片流片中發揮著去除多余材料、形成精細結構的關鍵作用。不同的蝕刻氣體對不同的材料具有選擇性,因此需要根據實際需求選擇合適的蝕刻氣體。此外,蝕刻過程中的溫度、壓力和時間等參數也需要精確控制,以確保蝕刻的均勻性和準確性。

薄膜材料:在芯片內部電路和互連結構的構建中扮演著重要角色。金屬、氧化物等薄膜材料的沉積需要精確控制厚度、均勻性和純度等參數,以確保芯片內部的電路連接和信號傳輸的穩定性。同時,薄膜材料的性質和穩定性也直接影響著芯片的可靠性和壽命。

|

半導 體材料 |

細分材料 | 主要用途 | 主要應用環節 | 發展趨勢 |

| 制造材料 | 硅片 | 全球95%以上的半導體芯片和器件是用硅片作為基底 | 貫穿制造環節 | 硅片各技術的發展方 |

| 光刻膠及配套試劑 | 用于顯影,刻蝕等工藝,將微細圖形從掩模板轉移到待加工基襯底 | 顯影、刻蝕 | 光刻分辨率提高,KrF、ArF、EUV占據主流。 | |

| 電子氣體 | 薄膜、刻蝕、摻雜、氣相沉積、擴散等 | 薄膜、刻蝕、摻雜、氣相沉積、擴散 | 電路線寬不斷縮短,對電子氣體的純度要求不斷提高。 | |

| 濺射靶材 | 半導體濺射薄膜沉積 | 薄膜沉積 | 銅、鉭靶材由于12寸晶圓比重上升,逐步替代鋁、鈦靶材。 | |

| 高純試劑 | 芯片的清洗、刻蝕 | 清洗、刻蝕 | 等級要求從G3、G4上升到G4、G5。 | |

| CMP | IC硅片拋光 | 化學機械拋光 | CMP拋光步驟隨芯片尺寸的減小而不斷增加。 | |

| 光掩膜版 | "底片"轉移用的高精密工具 | 光刻 | 掩模板精細化、大型化。 | |

| 封裝材料 | 封裝基板 | 主要對芯片起到固定、支撐、散熱以及連接下層電路板的作用 | 貼片、重組晶圓、切筋/成型 |

先進封裝占比將逐步超越傳統封裝,先進封裝材料成為主流。 封裝基板已經逐漸取代傳統引線框架成為主流封裝。 封裝基板正朝著高密度化方向發展。 |

| 引線框架 | 承托芯片和外引管腳,連接芯片焊點和引線框架或基板 | 裝片、引線鍵合 | ||

| 鍵合絲 | 鏈接芯片焊點和引線框架或基板,以實現芯片和外電路的電氣連接 | 引線鍵合 | ||

| 塑封材料 | 對芯片和引線框架起到密封和保護的作用 | 塑封 | ||

| 芯片粘結材料 | 將芯片與承載體連接的材料,以起到固定芯片的作用 | 貼片、塑封 |

*資料來源:千際投行,資產信息網,中國產業信息網

材料使用在芯片流片過程中具有舉足輕重的地位。光刻膠、蝕刻氣體和薄膜材料等關鍵材料的選擇和使用都需要經過嚴格的篩選和測試,以確保芯片的性能和可靠性達到設計要求。同時,隨著半導體技術的不斷發展,新型材料的研發和應用也將為芯片流片技術帶來更多的可能性和挑戰。

#05

流片的挑戰與解決方案

5.1 設計與成本挑戰

在芯片的設計與流片過程中,設計與成本的挑戰日益凸顯,成為制約行業發展的重要因素。

設計復雜性:隨著摩爾定律的延續,芯片上的晶體管數量不斷增加,導致電路規模的擴大。這不僅增加了版圖驗證和布線優化的工作量和技術難度,還要求性能的提升和功耗控制的更高標準。互連線的長度和密度的上升,也使得設計和驗證變得更加復雜。

工藝技術進步:高精度要求推動了從深亞微米到納米級工藝的技術跨越。這對設備精度和材料性能提出了更高要求,導致設備成本上升和材料研發、采購的難度增加。同時,高精度工藝需要更為嚴格的質量控制,以確保每一個生產環節的穩定性和可靠性,進一步增加了流片的整體成本。

應對策略:

設計環節:通過引入更高效的設計工具和方法,如高級綜合、自動布線等,提高設計效率并降低人為錯誤。采用層次化設計、模塊化設計等思想,將復雜系統分解為更易于管理的子模塊,從而降低設計的復雜性。

成本控制:優化工藝參數和材料選擇是關鍵。深入研究工藝原理和材料性能,找到性價比更高的工藝方案和材料組合。提高設備利用率、降低廢品率等方式也是降低成本的有效途徑。加強與供應鏈合作伙伴的溝通與協作,確保材料供應的穩定性和價格合理性。

設計與成本的挑戰是芯片流片過程中不可回避的問題。通過不斷創新和優化設計與流片流程中的各個環節,可以有效應對這些挑戰并推動半導體行業的持續發展。

5.2 流片失敗的應對措施

在半導體制造領域,流片失敗可能帶來嚴重的后果,包括資金損失、時間延誤,甚至可能影響整個項目的成敗。因此,采取有效的應對措施至關重要。

加強設計驗證和測試:在設計階段進行詳盡和嚴謹的仿真測試,以及在實際流片前進行嚴格的版圖驗證和時序分析,可以盡可能在設計階段發現并修正潛在問題,從而顯著提高流片的成功率。

與流片廠商的緊密溝通:流片過程中可能遇到各種工藝和設備問題,建立與流片廠商的定期溝通機制,及時反饋和解決問題,對于確保流片的順利進行至關重要。

建立完善的失敗分析和改進機制:即使做了充分的預防和準備工作,流片失敗的可能性仍然存在。通過對失敗原因的深入剖析,可以找出問題的根源,并據此優化設計和流片流程,從而避免類似問題的再次發生。

降低流片失敗的風險需要從多個方面入手,包括加強設計驗證和測試、與流片廠商的緊密溝通,以及建立完善的失敗分析和改進機制。這些措施的實施,不僅可以提高流片的成功率,還可以為半導體制造行業的持續發展和技術創新提供有力保障。

#06

市場應用與趨勢

6.1 應用領域

芯片技術的不斷進步使得流片工藝在多個領域內得到了廣泛應用,為智能設備的高性能、低功耗和小型化提供了有力支持。以下是幾個主要應用領域:

智能設備:智能手機、平板電腦、智能家居等設備中的處理器、存儲器和傳感器都依賴于先進的芯片流片技術。這些技術確保了設備的高性能和低功耗,同時實現了更小的物理尺寸。

通信領域:隨著5G和6G等新一代通信技術的快速發展,對芯片的性能和可靠性提出了更高要求。流片技術的創新為通信基站、網絡設備和移動終端提供了高性能的芯片解決方案,推動了通信行業的迅猛發展。

汽車領域:汽車行業正經歷電動化、智能化和網聯化的變革。芯片作為汽車電子系統的核心部件,其重要性日益增加。流片技術的進步使車載芯片具備更高的集成度、更強的處理能力和更佳的安全性能,助力汽車產業向智能化和綠色化方向發展。

醫療領域:芯片流片技術在醫療設備中的應用廣泛,從控制系統到生物傳感器的微型化,再到遠程醫療和可穿戴設備的普及,芯片技術提供了強大的支持。流片工藝的進步為醫療行業的創新發展提供了技術保障。

總的來說,芯片流片技術已經滲透到現代社會的各個領域,成為推動科技進步和產業升級的關鍵力量。隨著技術的不斷發展和市場需求的持續增長,芯片流片技術將迎來更加廣闊的發展空間和應用前景。

6.2 市場現狀與趨勢

全球流片市場目前正處于快速發展和持續變革的階段。隨著科技的飛速進步,尤其是5G、物聯網和人工智能等新興技術的崛起,對高性能、低功耗芯片的需求不斷增加,推動了流片市場的蓬勃發展。

1. 市場現狀

主要需求地區:北美、歐洲和亞洲。這些地區的半導體產業發達,擁有眾多知名的芯片設計公司和先進的制造工廠。

亞洲的崛起:隨著全球電子產業的持續遷移,尤其是中國,正在逐漸成為全球流片服務的重要市場和供應基地。

2. 未來發展趨勢

技術升級:隨著芯片設計復雜性和集成度的提高,流片技術將朝著更高精度和更高效能方向發展。這要求流片服務商不斷升級其工藝和設備,以滿足日益嚴格的技術要求。

綠色流片:環保和可持續發展理念的深入將推動綠色流片技術的發展,包括采用更環保的材料和優化工藝流程以減少能源消耗和廢棄物排放。

全球協作:全球半導體產業鏈的深度融合和協同發展將成為流片市場的重要特征。跨國合作和資源共享將有助于降低生產成本、提高生產效率,并推動全球流片市場的持續繁榮。

全球流片市場正面臨著前所未有的發展機遇和挑戰。服務商需要不斷創新,緊跟技術潮流,并滿足客戶需求,才能在競爭激烈的市場中脫穎而出。

6.3 服務提供商與機遇

在中國,隨著半導體產業的快速發展,芯片流片服務提供商的數量和技術水平都顯著提升。這些服務提供商包括傳統國有大型企業和眾多新興民營科技企業,共同推動了國內芯片設計、制造和封裝測試等環節的協同發展。

1. 主要流片服務提供商

中芯國際:作為中國大陸最大的芯片代工廠商,中芯國際在技術實力和生產規模上位居國內前列。

華虹半導體:專注于CMOS影像傳感器的研發與生產,擁有多項核心專利技術。

長鑫存儲:主要研發和生產DRAM內存芯片,致力于打破國外技術壟斷,提升國產芯片的市場競爭力。

2. 發展機遇

國家政策扶持:國家出臺了一系列鼓勵半導體產業發展的政策措施,包括設立專項基金、建設產業園區、推動產學研合作等,為芯片流片行業提供了良好的發展環境和資金支持。

市場需求旺盛:隨著5G、物聯網、人工智能等新興技術的快速發展,對高性能、低功耗芯片的需求日益增加,為芯片流片行業帶來了廣闊的市場空間。

全球產業格局變化:隨著全球半導體產業鏈的重構和轉移,越來越多的國際芯片設計公司將目光投向中國市場,尋求與國內流片服務提供商的合作。這為國內企業提供了與國際先進水平接軌的機會,提升技術實力和國際競爭力。

中國芯片流片行業在服務提供商的共同努力下,正迎來前所未有的發展機遇。未來,隨著技術的不斷進步和市場的持續擴大,國內流片企業有望在國際半導體舞臺上扮演更加重要的角色。

6.4 挑戰與政策支持

中國芯片流片行業近年來取得了顯著發展,但仍面臨著一系列挑戰,這些挑戰主要來自技術、資金、人才和國際市場環境等多個方面。

1. 技術挑戰

盡管中國的芯片設計能力在逐步提升,但與國際先進水平相比仍存在一定差距,尤其是在高端芯片領域,如處理器和存儲器等關鍵技術上。流片技術的復雜性和高精度要求使得技術突破成為一項長期而艱巨的任務。

2. 資金挑戰

芯片流片需要大量資金投入,包括研發經費、設備購置和維護費用等。然而,中國芯片產業整體上尚未形成穩定的盈利模式,許多企業在資金籌措上面臨困難。

| 工藝類型 | 流片一次的花費(網傳) |

| 40nm工藝 | 80萬美元 |

| 28nm工藝 | 200萬美元 |

| 14nm工藝 | 500萬美元 |

| 7nm工藝 | 1500萬美元 |

| 5nm工藝 | 4725萬美元 |

*來源:摩爾精英

3. 人才挑戰

中國雖然擁有龐大的勞動力市場,但具備專業芯片設計和流片技術的人才相對匱乏,這在一定程度上限制了芯片產業的發展速度和質量。

4. 政府支持措施

為應對這些挑戰,中國政府采取了一系列政策措施支持芯片流片產業的發展,包括:

財政補貼和稅收優惠:降低企業運營成本,提高市場競爭力。

人才培養和引進:通過與高校和研究機構合作,培養更多專業技能人才。

產學研用深度融合:鼓勵企業加強與國際先進企業的合作和交流,引進先進技術和管理經驗。

這些措施旨在提升中國芯片流片產業的技術水平和創新能力,推動整個產業鏈的完善和升級。

5. 未來展望

中國芯片流片行業在政府政策支持和產業界共同努力下,有望實現更大突破和發展。通過加強自主研發、優化產業鏈結構、拓寬融資渠道、加強人才培養和引進等措施,中國芯片流片產業將迎來更加廣闊的發展空間和市場機遇。

#06

結 論

本文全面探討了芯片流片技術及其在半導體制造中的重要性。通過詳細討論芯片設計與流片準備、流片技術的具體細節、設備與材料的使用,以及流片過程中的挑戰與解決方案,揭示了流片技術的復雜性和關鍵性。同時,市場應用與趨勢的分析展示了芯片流片技術在全球范圍內的廣泛應用和持續發展。

在分析中國芯片流片的現狀與未來時,本文介紹了主要流片服務提供商及行業面臨的機遇,討論了挑戰以及政府的政策支持。通過成功和失敗案例的對比分析,總結了流片過程中的經驗教訓,為未來項目提供了寶貴參考。

總體而言,芯片流片技術是半導體制造中的核心技術,其發展不僅影響芯片設計的實現,也直接關系到半導體產業的競爭力和市場格局。隨著技術進步和市場需求增長,芯片流片技術將在未來發揮更加重要的作用,推動半導體行業的持續創新和發展。

參考:

[1] CredenceSystemsCorporation 初次流片芯片的FIB編輯 半導體技術 2005

[2] 晶圓廠,測試芯片,流片 中芯國際與燦芯半導體40納米低漏電工藝ARM Cortex-A9雙核測試芯片成功流片

[3] Kenichi IWATSUKA;K Iwatsuka 3273 Study on micro-groove milling of a microchannel die : Selection guidelines for cutting conditions with micro end mills Proceedings of International Conference on Leading Edge Manufacturing in 21st century : LEM21 2011 10.1299/jsmelem.2011.6.3273-1

[4] 顯示芯片 韓國無晶圓廠半導體公司TLi采用Arasan的IP產品實現成功流片 電源技術應用 2015

[5] None 中國首個自主研發5G微基站射頻芯片流片成功 半導體信息 2020

[6] 虹識技術 虹識技術成功流片乾芯ASIC芯片QX8001 中國集成電路 2018

[7] 景行 FPGA中多協議I/O接口電路的設計與測試

[8] Shari L. Murray de Diaz Evaluating the impacts of reticle requirements in semiconductor wafer fabrication IEEE Transactions on Semiconductor Manufacturing 2005 10.1109/TSM.2005.858502

[9] 尚鵬 多協議的半導體照明網絡VLSI芯片設計 2015

[10] 黃龍 單芯片集成USM驅動電路的關鍵技術研究與實現 2019

[11] 無 Cadence解決方案助力創意電子20nm SoC測試芯片成功流片 2022

[12] 彭進 28nm SoC芯片設計方法及流程實現 集成電路應用 2016 10.19339/j.issn.1674-2583.2016.05.005

[13] 高勇 新型全數字三相SPWM信號產生芯片的設計與實現 半導體學報 2006

[14] 寧剛玲 以GPU為例的芯片設計制造模式和流程的研究 中國新通信 2023

[15] 李亞會 一款低EMI降壓型DC/DC芯片的設計 2014 10.7666/d.D728458

[16] 宋怡曈 基于buffer刪除算法的MCU芯片時序優化與修復研究 2022

[17] 李靈 硅基毫米波低噪聲放大器研究與設計 2022

[18] O'Neal, Chad Barrett.;CB O'Neal MEMS-based nanomechanical machining system-on-a-chip: Design, fabrication, and functional testing for feasibility. 2004

-

芯片

+關注

關注

455文章

50756瀏覽量

423340 -

半導體

+關注

關注

334文章

27320瀏覽量

218292 -

流片

+關注

關注

0文章

28瀏覽量

9760

原文標題:一萬五千字詳解什么是芯片流片

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

全新的半導體基礎知識

芯片流片的基礎知識

芯片流片的基礎知識

評論