先進(jìn)封裝技術(shù)(Semiconductor Advanced Packaging) - 1 混合鍵合技術(shù)(上)

先進(jìn)封裝技術(shù)(Semiconductor Advanced Packaging) - 2 混合鍵合技術(shù)(下)

先進(jìn)封裝技術(shù)(Semiconductor Advanced Packaging) - 3 Chiplet 異構(gòu)集成(上)

先進(jìn)封裝技術(shù)(Semiconductor Advanced Packaging) - 4 Chiplet 異構(gòu)集成(下)

先進(jìn)封裝技術(shù)(Semiconductor Advanced Packaging) - 5 TSV 異構(gòu)集成與等效熱仿真

先進(jìn)封裝技術(shù)(Semiconductor Advanced Packaging) - 6 扇出型晶圓級封裝(FOWLP)

先進(jìn)封裝技術(shù)(Semiconductor Advanced Packaging) - 7 扇出型板級封裝(FOPLP)

先進(jìn)封裝技術(shù)(Semiconductor Advanced Packaging) - 8 3D封裝與TSV技術(shù)

先進(jìn)封裝技術(shù)(Semiconductor Advanced Packaging) - 9 堆疊封裝(PoP)技術(shù)

先進(jìn)封裝技術(shù)(Semiconductor Advanced Packaging) - 10 2.5D封裝與異構(gòu)集成技術(shù)

先進(jìn)封裝技術(shù)(Semiconductor Advanced Packaging) - 11 SiP 系統(tǒng)級封裝

先進(jìn)封裝技術(shù)(Semiconductor Advanced Packaging) - 12 表面貼裝技術(shù) SMT

先進(jìn)封裝技術(shù)(Semiconductor Advanced Packaging) - 13 倒裝封裝 Flip Chip

先進(jìn)封裝技術(shù)(Semiconductor Advanced Packaging) - 14 光電共封技術(shù)(CPO) (上)

先進(jìn)封裝技術(shù)(Semiconductor Advanced Packaging) - 15 光電共封技術(shù)(CPO) (下)

先進(jìn)封裝技術(shù)(Semiconductor Advanced Packaging) - 16 硅橋技術(shù)(Si Bridge)(上)

(繼續(xù)上文~)基于扇出型封裝的硅橋互連

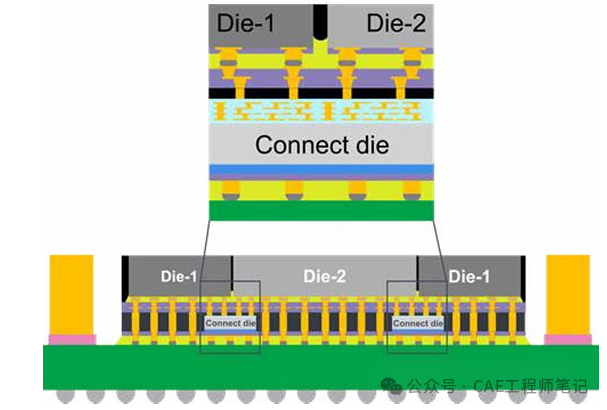

基于扇出型封裝的硅橋互連技術(shù)思路是將硅橋芯片埋置在環(huán)氧樹脂料中,通過再布線完成與芯片的互連。根據(jù)硅橋芯片與再布線層制作順序的不同可以進(jìn)一步區(qū)分為硅橋芯片后置型和先置型技術(shù)。硅橋芯片后置型技術(shù)中 RDL 層可以優(yōu)先制作,隨后與 RDL 層完成倒裝焊接。

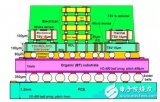

安靠提出的芯粒異構(gòu)集成封裝技術(shù)為埋置扇出型中介層技術(shù) (S-Connect),該項(xiàng)技術(shù)中內(nèi)置的橋芯片不僅可以是硅橋,也可以是樹脂橋。封裝測試樣件結(jié)構(gòu)如下圖所示,包含一顆邏輯芯片和兩顆存儲芯片,功能芯片與內(nèi)嵌橋芯片的扇出型轉(zhuǎn)接板進(jìn)行組裝。

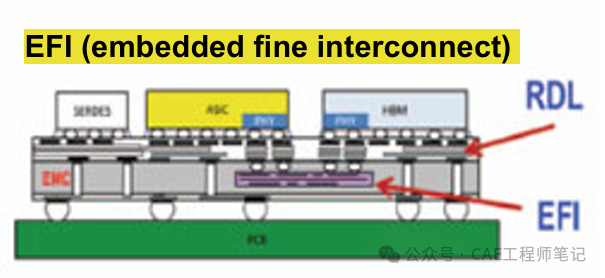

IME 研究所提出基于硅橋芯片的高密度異構(gòu)集成先進(jìn)封裝解決方案為內(nèi)嵌精細(xì)互連技術(shù)(EFI)。通過嵌入式轉(zhuǎn)接板實(shí)現(xiàn) ASIC 芯片和存儲芯片的異構(gòu)芯粒的集成。其中 EFI 芯片也就是硅橋芯片,布線層數(shù)為 2 層,布線精度為 5μm,信號通過銅柱凸點(diǎn)(Cu/SnAg)引出。

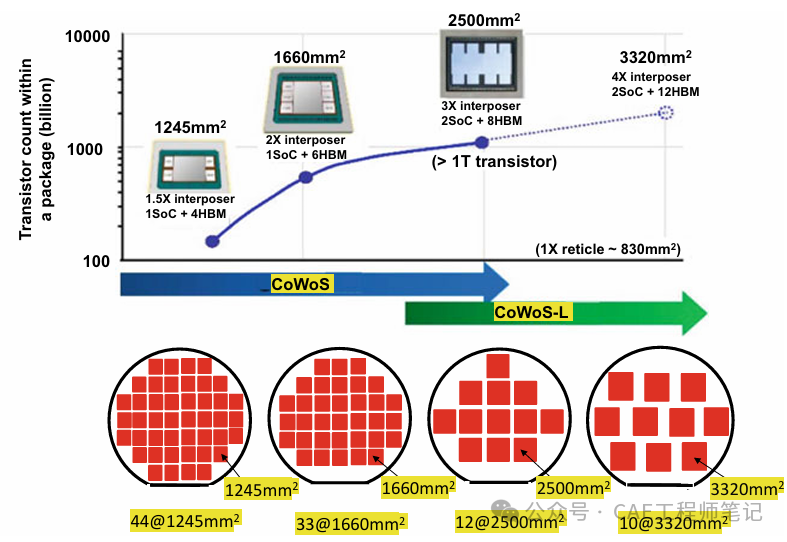

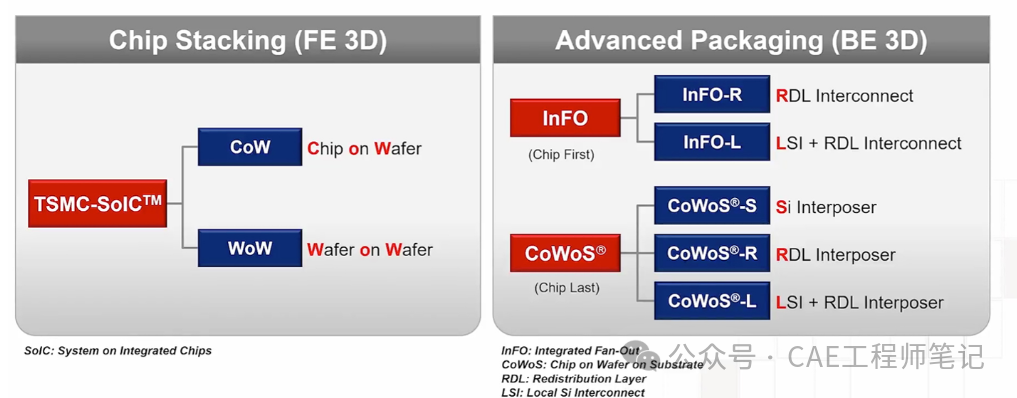

臺積電在晶圓制造和封測方面一直處于業(yè)內(nèi)領(lǐng)頭羊地位。其在先進(jìn)封裝技術(shù)領(lǐng)域提出的 InFO 和 CoWoS 兩項(xiàng)王牌先進(jìn)封裝技術(shù)已在大量集成電路產(chǎn)品中制造應(yīng)用。

臺積電為了進(jìn)一步優(yōu)化和發(fā)展在 2.5D 以及 3D 先進(jìn)封裝集成技術(shù),滿足未來芯粒和異構(gòu)集成的需求,細(xì)化了 InFO 和 CoWoS 兩項(xiàng)技術(shù)的發(fā)展方向。

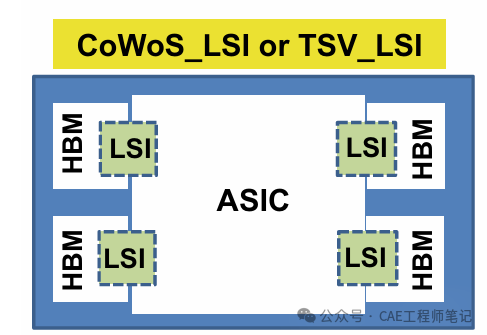

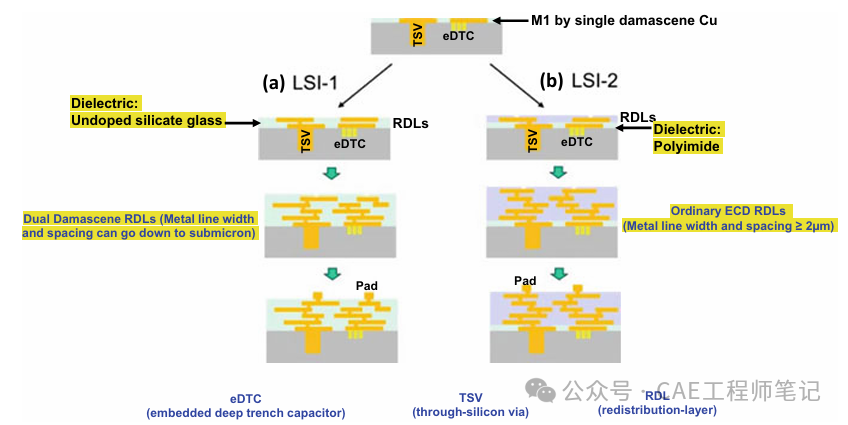

InFO 技術(shù)進(jìn)一步細(xì)化為 RDL 集成扇出 (InFO-R) 和硅橋內(nèi)嵌 RDL 集成扇出(InFO-L)。CoWoS 技術(shù)進(jìn)一步細(xì)化為硅中介層技術(shù)(CoWoS-S)、RDL中介層技術(shù) (CoWoS-R) 和硅橋內(nèi)嵌 RDL 中介層技術(shù)(CoWoS-L)。InFO-L 和 CoWoS-L 中的 L 代表 LSI,也就是局域硅橋互連。

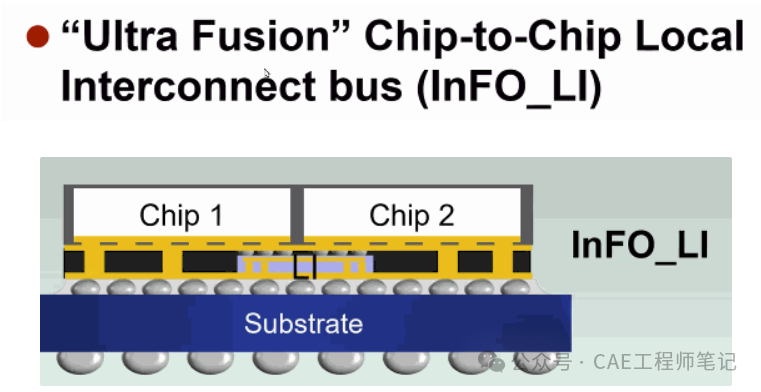

InFO-L 技術(shù)是臺積電在 InFO 的基礎(chǔ)上通過扇出實(shí)現(xiàn)硅橋芯片內(nèi)嵌的技術(shù),先將裸芯片通過重構(gòu)扇出工藝完成再布線層,硅橋芯片內(nèi)嵌在芯片的再布線層中。CoWoS-L 技術(shù)是臺積電基于 CoWoS 硅基轉(zhuǎn)接板的思路,通過制備有機(jī)轉(zhuǎn)接板來替代硅轉(zhuǎn)接,其中有機(jī)轉(zhuǎn)接板通過再布線工藝實(shí)現(xiàn),制備過程中內(nèi)嵌了硅橋芯片。

InFO-L 技術(shù)是在芯粒的重構(gòu)圓片上完成再布線層的制備,CoWoS-L 技術(shù)在臨時(shí)載板上單獨(dú)完成再布線層的制備,隨后與硅橋芯片完成集成,因此屬于硅橋芯片后置型技術(shù)。

硅橋芯片先置型技術(shù)中優(yōu)先完成硅橋芯片與塑封料的結(jié)合,硅橋芯片采用正裝裝片(區(qū)別于后置型技術(shù)中硅橋芯片的倒裝焊接),在此基礎(chǔ)上進(jìn)行再布線層制作和芯片組裝。

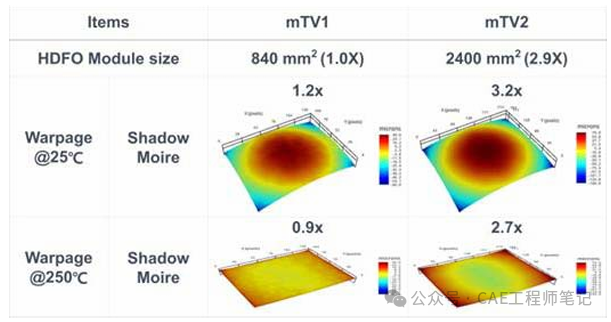

日月光在面向高性能計(jì)算的芯粒集成需求時(shí),提出了高密度扇出型封裝技術(shù)系列方案,分別命名為芯片后置型扇出 (FOCoS-CL)、芯片先置型扇出 (FOCoS-CF) 以及扇出堆疊技術(shù) (sFOCoS)。三種技術(shù)都是基于晶圓級扇出型封裝,將不同設(shè)計(jì)和工藝節(jié)點(diǎn)的芯粒形成單個(gè)封裝體。日月光強(qiáng)調(diào)晶圓級翹曲控制對于整個(gè)芯粒集成至關(guān)重要,并指出塑封料和底部填充材料的選擇對于改善扇出封裝圓片的翹曲有巨大影響。

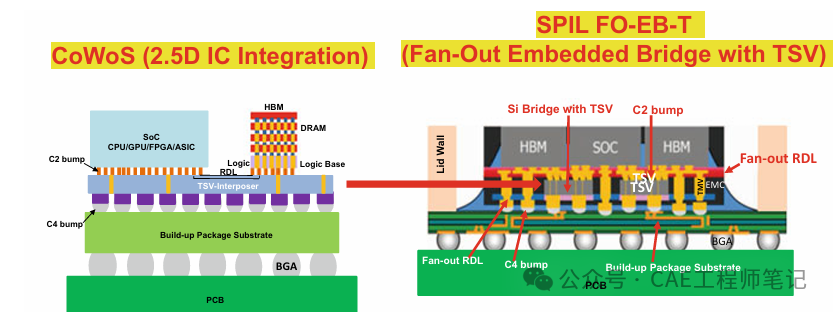

在IEEE/ECTC 2023,SPIL 提出了基于扇出型封裝提出了硅橋埋置扇出技術(shù) FOEB 和 FOEB-T 技術(shù)。FOEB 工藝流程基本和日月光的 sFOCoS 一致,F(xiàn)OEB-T 與 FOEB 的區(qū)別是將內(nèi)嵌的硅橋芯片采用 TSV 芯片的設(shè)計(jì),進(jìn)一步減少長距離的傳輸損耗。

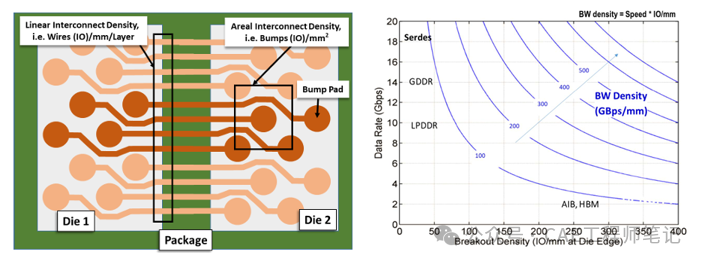

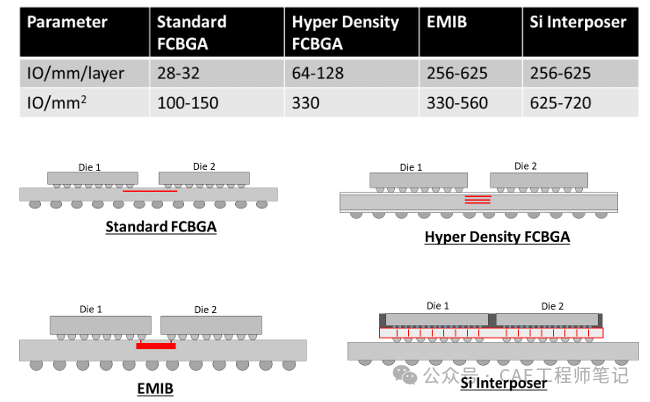

硅橋封裝面臨的挑戰(zhàn)在基于硅橋技術(shù)的集成封裝中,封裝體各部分的材料、結(jié)構(gòu)、工藝參數(shù)及流片過程的差異較大,這些差異導(dǎo)致微結(jié)構(gòu)互連界面上的電、熱、力等性能均面臨較大的挑戰(zhàn),這對整個(gè)集成封裝體的協(xié)同設(shè)計(jì)及制造能力提出了極高的要求。

由于硅橋需要被嵌入到基板中,這會導(dǎo)致有機(jī)基板制備工藝復(fù)雜性提高,在精度要求上遠(yuǎn)高于現(xiàn)有的有機(jī)基板布線,因此需要針對該結(jié)構(gòu)進(jìn)行相應(yīng)的材料和工藝開發(fā)。為了滿足高密度布線和高頻傳輸?shù)囊螅珹BF 膜的硅粉填料占比不斷提高,其 CTE 和介電損耗不斷降低,同時(shí)還要確保材料對曝光光線的高敏感度。基板上的金屬線路大多是通過半加成工藝制備的,該工藝對介質(zhì)層與基底上金屬種子層結(jié)合力的要求較高。若結(jié)合力較差,在濕制程腐蝕過程中容易出現(xiàn)側(cè)刻或分層的現(xiàn)象,導(dǎo)致線路與基底分離,不利于精細(xì)線路的制備。由于對表面平整度的要求高,在層壓介質(zhì)層的過程中必須實(shí)現(xiàn)高度平坦化,以提高Chiplet 與硅橋的鍵合平整度。由于整個(gè)封裝體工藝集成度高,從設(shè)計(jì)到加工必須實(shí)現(xiàn)協(xié)同性制造。

隨著布線寬度的減小,線電阻會急劇增加,線間的電容也會改變,這些變化給信號的完整性增加了挑戰(zhàn)。在進(jìn)行硅橋走線設(shè)計(jì)時(shí),不僅要考慮介質(zhì)層材料的介電常數(shù)和高頻損耗對整體性能的影響,還要進(jìn)行非常詳細(xì)的架構(gòu)設(shè)計(jì)和模擬工作來保證最終的產(chǎn)品性能。

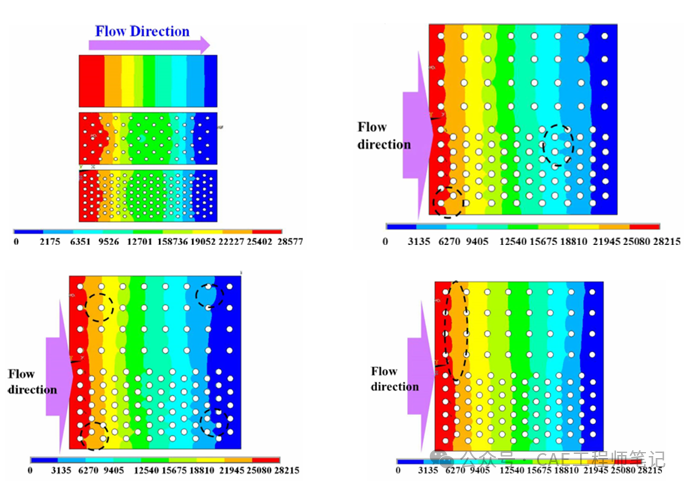

底部填充料被用于填充芯片與基板、硅橋與基板之間的空隙,以降低焊點(diǎn)因熱應(yīng)力導(dǎo)致的斷裂失效風(fēng)險(xiǎn)。在各種底部填充材料中,環(huán)氧樹脂基底部填充膠不僅應(yīng)用最為廣泛,也是商業(yè)化程度較高的產(chǎn)品。然而,隨著芯片尺寸的日益增大,芯片與硅橋上的微凸點(diǎn)數(shù)量越來越多,填充膠的填充速度大大降低,進(jìn)而延長了填充工藝的時(shí)間。同時(shí),由于填充膠的流動性無法滿足微凸點(diǎn)結(jié)構(gòu)的特定需求,使得部分微凸點(diǎn)周圍出現(xiàn)空洞。空洞的存在會嚴(yán)重影響倒裝芯片的封裝可靠性。此外,毛細(xì)管環(huán)氧基底部填充膠的導(dǎo)熱系數(shù)較低,難以滿足下一代先進(jìn)封裝芯片在功率密度方面日益增長的散熱需求,亟待開發(fā)出低成本、高可靠的底部填充材料。

-

芯片

+關(guān)注

關(guān)注

455文章

50756瀏覽量

423343 -

先進(jìn)封裝

+關(guān)注

關(guān)注

2文章

403瀏覽量

246

原文標(biāo)題:先進(jìn)封裝技術(shù)(Semiconductor Advanced Packaging) - 17 硅橋技術(shù)(Si Bridge)(下)

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

硅通孔封裝工藝流程與技術(shù)

多芯片整合封測技術(shù)--種用先進(jìn)封裝技術(shù)讓系統(tǒng)芯片與內(nèi)存達(dá)到高速傳輸

怎樣衡量一個(gè)芯片封裝技術(shù)是否先進(jìn)?

先進(jìn)封裝技術(shù)的發(fā)展趨勢

詳解TSV(硅通孔技術(shù))封裝技術(shù)

先進(jìn)封裝技術(shù)的發(fā)展與機(jī)遇

什么是先進(jìn)封裝技術(shù)的核心

淺析先進(jìn)封裝的四大核心技術(shù)

什么是先進(jìn)封裝?先進(jìn)封裝技術(shù)包括哪些技術(shù)

先進(jìn)封裝技術(shù)- 6扇出型晶圓級封裝(FOWLP)

先進(jìn)封裝技術(shù)-7扇出型板級封裝(FOPLP)

CoWoS先進(jìn)封裝技術(shù)介紹

先進(jìn)封裝中的TSV/硅通孔技術(shù)介紹

先進(jìn)封裝的核心概念、技術(shù)和發(fā)展趨勢

先進(jìn)封裝技術(shù)-16硅橋技術(shù)(上)

先進(jìn)封裝技術(shù)-17硅橋技術(shù)(下)

先進(jìn)封裝技術(shù)-17硅橋技術(shù)(下)

評論