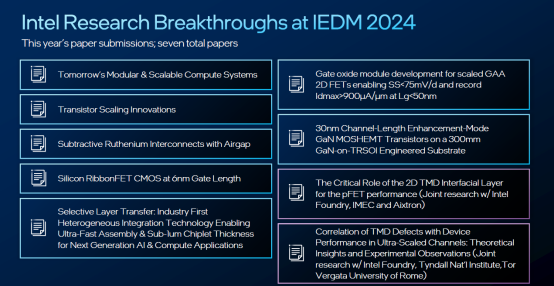

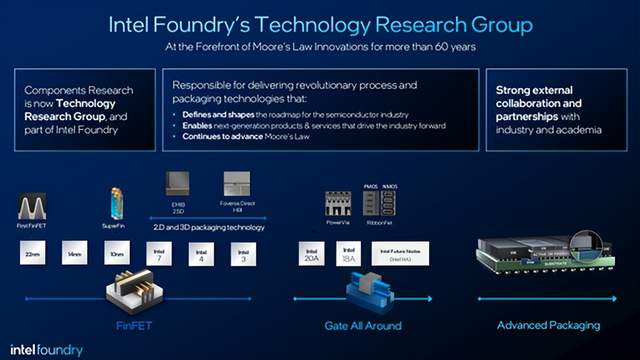

芯東西12月16日報道,在IEDM 2024(2024年IEEE國際電子器件會議)上,英特爾代工展示了包括先進封裝、晶體管微縮、互連縮放等在內的多項技術突破,以助力推動半導體行業在下一個十年及更長遠的發展。

英特爾通過改進封裝技術將芯片封裝中的吞吐量提升高達100倍,探索解決采用銅材料的晶體管在開發未來制程節點時可預見的互連微縮限制,并繼續為先進的全環繞柵極(GAA)晶體管及其它相關技術定義和規劃晶體管路線圖。

這些技術進展來自負責研發突破性制程和封裝技術的英特爾代工技術研究團隊。在IEDM 2024上發表的部分論文由英特爾代工與其他團隊共同完成。

隨著行業朝著到2030年在單個芯片上實現一萬億個晶體管的目標前進,先進封裝、晶體管微縮、互連微縮等技術突破對于未來滿足更高性能、更高能效、更高成本效益的計算應用需求至關重要。

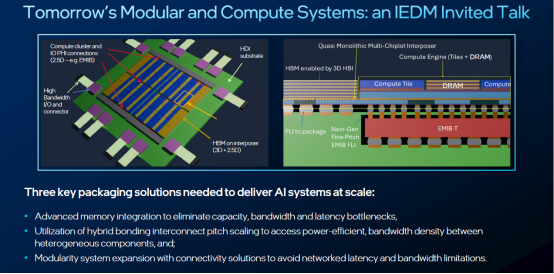

一、先進封裝:異構集成新方案,將吞吐量提升多達100倍

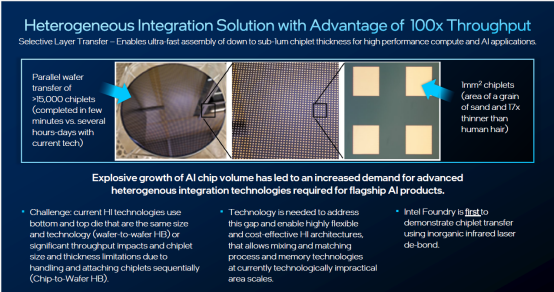

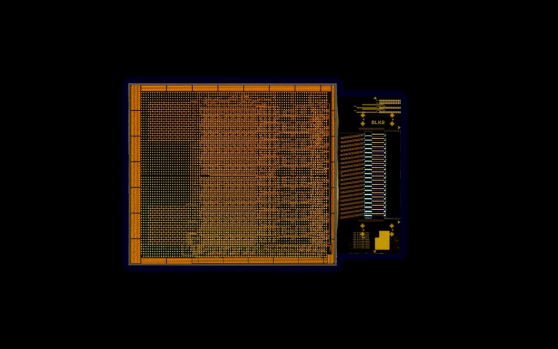

英特爾代工匯報了一種用于先進封裝的異構集成解決方案——選擇性層轉移(Selective Layer Transfer, SLT),可以在芯片封裝中將吞吐量提升高達100倍,實現超快速的芯片間封裝(chip-to-chip assembly)。

與傳統的芯片到晶圓鍵合(chip-to-wafer bonding)技術相比,選擇性層轉移能夠讓芯片的尺寸變得更小,縱橫比變得更高。

該解決方案的基本思路是以晶圓到晶圓連接的吞吐量,實現芯片到晶圓連接的靈活性和能力,能夠以更高的靈活性集成超薄芯粒,還帶來了更高的功能密度,并可以結合混合鍵合(hybrid bonding)或融合鍵合(fusion bonding)工藝,提供更靈活且成本效益更高的解決方案,封裝來自不同晶圓的芯粒。

這為AI應用提供了一種更高效、更靈活的架構。

相應的技術論文名為《選擇性層轉移:業界領先的異構集成技術》,作者包括Adel Elsherbini、Tushar Talukdar、Thomas Sounart等人。

二、晶體管微縮:持續縮短柵極長度,探索用新材料替代硅

晶體管技術進步一直是英特爾的主業之一。

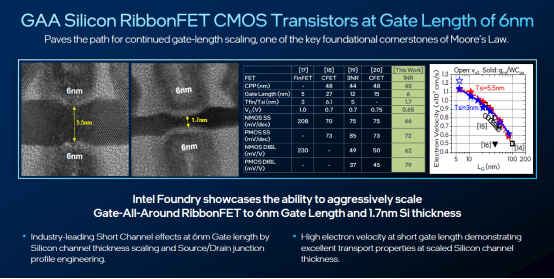

在最先進的全環繞柵極(GAA)晶體管方面,英特爾代工展示了硅基RibbionFET CMOS (互補金屬氧化物半導體)技術,以及用于微縮的2D場效應晶體管(2D FETs)的柵氧化層(gate oxide)模塊,以提高設備性能。

為了將RibbonFET GAA晶體管的微縮推向更高水平,英特爾代工展示了柵極長度為6nm、硅層厚度僅為1.7nm的硅基RibbonFET CMOS晶體管,在大幅縮短柵極長度和減少溝道厚度的同時,在對短溝道效應的抑制和性能上達到了業界領先水平。

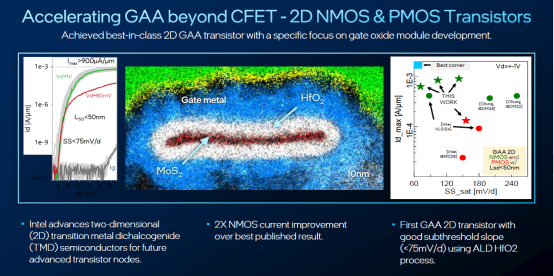

英特爾代工正在研究一個漸進式的發展步驟,將溝道材料由傳統材料替換為其它材料,比如2D材料。他們判斷一旦將基于硅的溝道性能推至極限,采用2D材料的GAA晶體管很有可能會成為下一步發展的合理方向。

為了在CFET(互補場效應晶體管)之外進一步加速GAA技術創新,英特爾代工展示了其在2D GAA NMOS(N型金屬氧化物半導體)和PMOS(P型金屬氧化物半導體)晶體管制造方面的研究,側重于柵氧化層模塊的研發,將晶體管的柵極長度微縮到了30nm。該研究還報告了行業在2D TMD(過渡金屬二硫化物)半導體領域的研究進展,此類材料未來有望在先進晶體管工藝中成為硅的替代品。

GaN是一種新興的用于功率器件和射頻(RF)器件的材料,相較于硅,它的性能更強,也能承受更高的電壓和溫度。英特爾代工團隊發現在數據中心領域,硅材料在電力傳輸方面快達到極限,而以300毫米GaN(氮化鎵)為代表的其他材料體系是頗具吸引力的替代選擇。

在300毫米GaN-on-TRSOI(富陷阱絕緣體上硅)襯底(substrate)上,英特爾代工制造了業界領先的高性能微縮增強型GaN MOSHEMT(金屬氧化物半導體高電子遷移率晶體管)。GaN-on-TRSOI等工藝上較為先進的襯底,可以通過減少信號損失,提高信號線性度和基于襯底背部處理的先進集成方案,為功率器件和射頻器件等應用帶來更強的性能。

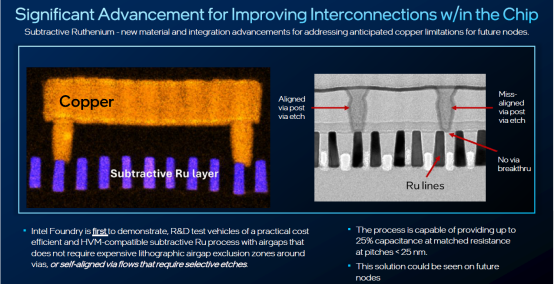

三、互連縮放:改善芯片內互連,最高將線間電容降低25%

銅互連的時代即將走向尾聲。隨著線寬不斷縮小,銅線的電阻率呈指數級上升,以至到難以接受的程度。當晶體管尺寸不斷縮小,使其越來越密集、功能越來越強大時,卻沒有能將所有這些晶體管連接在一起所需的布線。

取得突破的一個方法是減成法釕互連技術(subtractive Ruthenium)。

在間距小于或等于25nm時,采用減成法釕互連技術實現的空氣間隙最高可將線間電容降低25%,有助于改善芯片內互連,提升芯片性能。

具體而言,減成法釕互連技術通過采用釕這一新型、關鍵、替代性的金屬化材料,利用薄膜電阻率(thin film resistivity)和空氣間隙(airgap),實現了在互連微縮方面的重大進步。

英特爾代工率先在研發測試設備上展示了一種可行、可量產、具有成本效益的減成法釕互連技術,該工藝引入空氣間隙,無需通孔周圍昂貴的光刻空氣間隙區域(lithographic airgap exclusion zone),也不需要使用選擇性蝕刻的自對準通孔(self-aligned via)。這表明該技術作為一種金屬化方案,在緊密間距層中替代銅鑲嵌工藝的優勢。

這一解決方案有望在英特爾代工的未來制程節點中得以應用,或能探索出合理的下一代互連技術,使其與下一代晶體管及下一代封裝技術相適配。

相應技術論文名為《利用空氣間隙的減成法釕互連技術》,作者是Ananya Dutta、Askhit Peer、Christopher Jezewski。

結語:三大創新著力點,推動AI向能效更高發展

在IEDM 2024上,英特爾代工還分享了對先進封裝和晶體管微縮技術未來發展的愿景,以下三個關鍵的創新著力點將有助于AI在未來十年朝著能效更高的方向發展:

1、先進內存集成(memory integration),以消除容量、帶寬和延遲的瓶頸;2、用于優化互連帶寬的混合鍵合;3、模塊化系統(modular system)及相應的連接解決方案。

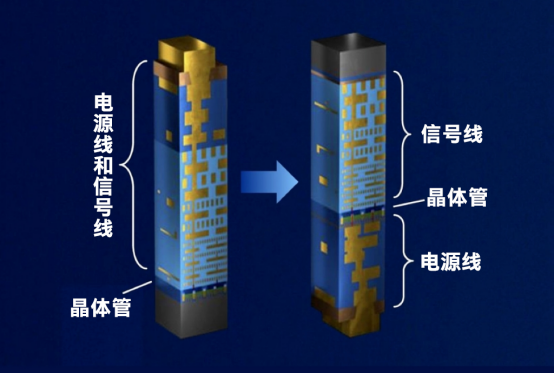

新型材料還有待進一步探索,來增強英特爾代工的PowerVia背面供電技術在緩解互連瓶頸、實現晶體管的進一步微縮中的作用。這對于持續推進摩爾定律、推動面向AI時代的半導體創新至關重要。

同時,英特爾代工發出行動號召,開發關鍵性和突破性的創新,持續推進晶體管微縮,推動實現“萬億晶體管時代”。

英特爾代工概述了對能夠在超低電壓(低于300毫伏)下運行的晶體管的研發,將如何有助于解決日益嚴重的熱瓶頸,并大幅改善功耗和散熱。

其團隊認為,應對能源挑戰的途徑之一,是采用極低供電電壓的高品質晶體管,不是僅在研究環境中制造出一個這樣的晶體管,而是要制造出數以萬億計的此類晶體管,使其具備足夠高的性能、穩定性、可重復性及可靠性,這樣才能用它們來制造產品。

審核編輯 黃宇

-

英特爾

+關注

關注

61文章

9960瀏覽量

171736 -

晶體管

+關注

關注

77文章

9688瀏覽量

138157 -

IEDM

+關注

關注

0文章

5瀏覽量

11312

發布評論請先 登錄

相關推薦

英特爾代工在IEDM 2024展示多項技術突破

IBM與Rapidus在多閾值電壓GAA晶體管技術的新突破

技術前沿:“環抱”晶體管與“三明治”布線

英特爾IEDM 2024大曬封裝、晶體管、互連等領域技術突破

英特爾IEDM 2024大曬封裝、晶體管、互連等領域技術突破

評論