以下文章來源于Keysight RF射頻測試資料分享,作者Keysight是德科技

如何解決信號完整性問題呢?是德科技在向您介紹信號完整性分析基礎知識的同時,我們還向您展示如何使用基本信號完整性(Signal Integrity - SI) 分析技術(例如眼圖、S參數、時域反射計(TDR) 和單脈沖響應)來解決信號完整性問題。

什么是信號完整性?

在時鐘頻率為 10 MHz 的美好時代,電路板或封裝的主要設計挑戰是如何在雙層電路板中路由所有信號以及如何獲得在組裝過程中不會破裂的封裝。互連的電氣特性并不重要,因為它們不會影響系統性能。從這個意義上說,我們說“互連對信號是透明的”。

例如,設備將輸出上升時間約為 10 納秒、時鐘頻率為 10 MHz 的信號,并且電路將與最粗糙的互連一起工作。用繞線板制造的原型與使用印刷電路板和工程變更線的最終產品一樣有效。

但時鐘頻率已經增加,信號的上升時間已經減少。對于大多數電子產品,信號完整性效應在時鐘頻率高于約 100 MHz 或上升時間短于約 1 納秒時開始變得重要。這有時被稱為高頻或高速狀態。這些術語指的是互連不再對信號透明的產品和系統,如果您不小心,就會出現一個或多個信號完整性問題。

信號完整性SI(Signal Integrity)從最廣泛的意義上講,是指高頻率高速度高精度數據傳輸中由于互連而出現的所有問題。它涉及互連的電氣特性如何與數字信號的電壓和電流波形相互作用來影響性能。

信號完整性包括由于互連、電源、器件等引起的所有信號質量及延時等問題。數字信號在傳輸的過程中,由于阻抗匹配、串擾等原因導致信號變差。數字信號完整性就是研究信號在傳輸過程中的保真度問題。

造成的常見的信號完整性問題的原因是什么?

1、阻抗不匹配

阻抗匹配指通過調整輸入阻抗和輸出阻抗來使得電子器件滿足一定條件,通常該條件是使得系統傳輸功率最大或者使得信號反射最小。例如,再無線傳輸系統中需要匹配射頻發射設備和接受天線的阻抗以此來實現傳輸功率最大化。

所以我們在做高速信號設計時會加上端接電阻只來減少反射。

“PCB設計過程中處處是陷阱。時間一久,設計人員逐漸總結了一些經驗法則!如何做50Ω阻抗匹配,如何接地等等。我們聽聽信號完整性專家是如何說的吧!"

PCB的設計問題:請問如何用矢量網絡分析儀來測量射頻輸出電路的阻抗,做阻抗分析,如何做阻抗匹配?謝謝!

答案:您可以通過測量該電路的反射S參數并通過史密斯原圖顯示其阻抗特性,設計阻抗匹配電路不是我們的專長。在您設計好阻抗匹配電路后,可以通過網絡分析儀里的Port Matching功能模擬加上阻抗匹配電路之后的結果。

2、信號串擾

什么是串擾?

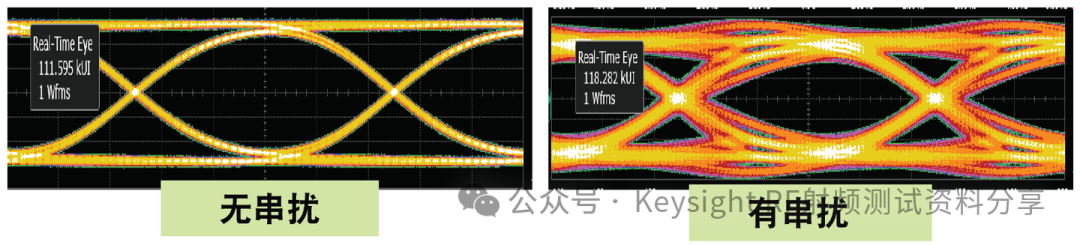

串擾是一種失真,主要來自與數據碼型無關的幅度干擾。由于耦合效應,一個干凈的信號(我們稱為“受擾信號”)可能受到“干擾”信號的串擾影響。干擾信號會使得受擾信號發生變形,并讓受擾信號的眼圖閉合。工程師希望信號是串擾極小或完全沒有串擾的干凈信號,如此才能獲得張開的眼圖,并進行準確無誤的數據傳輸。如果受擾信號中存在串擾,那么這種干擾會導致眼圖閉合,從而使得設計裕量變得很小甚至測量結果錯誤(如下圖)。串擾還會降低受擾信號的垂直幅度和水平抖動性能,導致通信鏈路中的互操作性問題愈發嚴重。

有串擾和沒有串擾的受擾信號眼圖。串擾會導致眼圖閉合,從而降低設計裕量并可能造成設計的性能達不到技術指標。

串擾是怎么產生的?

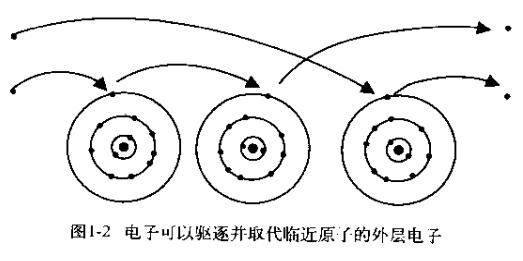

隨著技術的飛速發展,電子產品的而尺寸越來越小,數據的傳輸速度卻越來越高。普通消費類電子產品的PCB電路板很多至少是四層、六層甚至更多層。當信號沿傳輸線傳播時,信號路徑和返回路徑之間將產生電力線,圍繞在信號路徑周圍就會產生非常豐富的電磁場。這些延伸出去的場也稱為邊緣場,邊緣場將會通過互容與互感轉化為另一條傳輸線上的能量。而串擾的本質,其實就是傳輸線之間的互容與互感。

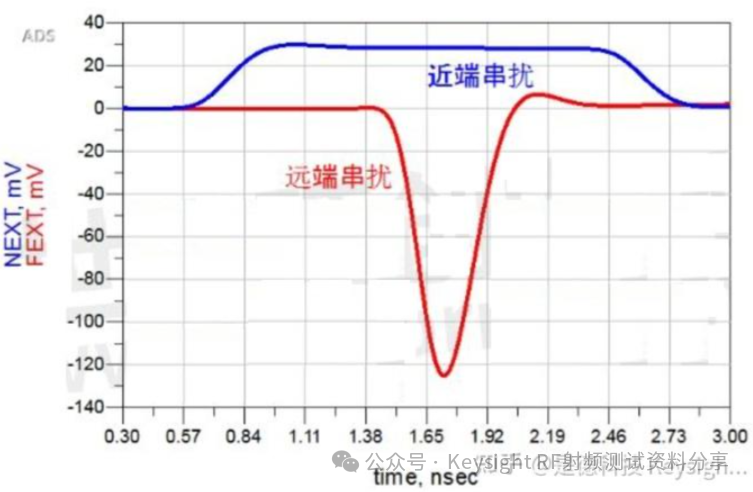

串擾可以分成兩部分,一部分與信號傳輸方向相同,傳至接收端方向,我們把它叫做遠端串擾或者前向串擾。另一部分與信號傳輸方向相反,傳至發送端方向,我們把它叫做近端串擾或者后向串擾。

近端串擾和遠端串擾是由傳輸線的物理結構而決定的,顯然在信號的傳遞過程中近端會首先受到干擾,并且持續的時間比較長,達到傳輸線的2倍;遠端串擾需要經過一段傳輸線的延時之后才會受到干擾。下圖是我們通過仿真獲得的近端串擾和遠端串擾的波形圖。

近端串擾和遠端串擾的波形圖

PCB板是什么意思?

“PCB is the abbreviation of "Printed Circuit Board", which means "printed circuit board" in Chinese. It is a base board that connects electronic components together through wires and connectors and provides electrical connections and support. Widely used in electronic products, it provides stable electrical connections so that electronic components can work reliably and communicate with other components. In addition, PCB boards can also provide mechanical support and protect electronic components, making them easier to install and maintain.”

“PCB是“Printed Circuit Board”的縮寫,中文意思為“印刷電路板”。它是一種通過導線和連接器將電子元器件連接在一起并提供電氣連接和支撐的基板。廣泛應用于電子產品中,提供穩定的電氣連接,使電子元器件能夠可靠地工作并與其他元器件進行通信。此外,PCB板還可以提供機械支撐和保護電子元器件,使其更易于安裝和維護。”

高速PCB板

高速PCB板是指在設計和制造過程中考慮了信號傳輸速度傳輸距離信號完整性等因素的印刷電路板。它通常用于高頻率高速度高精度數據傳輸的場合,如通信設備計算機硬件醫療器械等領域。

高速PCB板相比于普通PCB板具有以下顯著特點:

信號完整性 - 高速pcb板設計考慮了信號傳輸時的阻抗匹配信號耦合信號干擾等問題,確保信號傳輸的穩定性和可靠性。

電磁兼容性 - 高速PCB板采用屏蔽設計地線規劃等措施,降低電磁干擾,提高系統的抗干擾能力。

PCB板的材料選用 - 高速pcb板通常采用具有優良介電性能的材料,如PTFE、FR4等,以滿足高速信號傳輸的要求。

PCB板的布局優化 - 高速pcb板布局布線經過精心設計,減少信號路徑長度降低信號傳輸時間,提高系統的工作效率。

高速PCB板的主要應用領域包括通信,計算機硬件圖形處理和醫療影像設備生命監測儀器等醫療器械等。高速PCB板作為現代電子領域的重要組成部分,具有獨特的設計理念和應用優勢,為各種高速數據傳輸場景提供了可靠的技術支持。通過深入理解高速PCB板的定義特點和應用領域,可以更好地利用其優勢,提高系統性能和穩定性,推動科技發展與創新。

串擾與哪些因素有關?

影響串擾的設計因素主要有以下幾個方面:

線間距:信號路徑之間的距離越近,串擾越明顯,隨著線間距的增大,無論是近端還是遠端串擾都將減小,當線間距大于等于線寬的3倍時串擾已經很小。三倍線寬是工程師們信心的來源,在三倍線寬條件下,串擾基本可以忽略。

信號變化程度:信號瞬間變化會帶來明顯磁場效應。信號的上升沿/下降沿越陡峭,串擾越明顯。

介質層厚度:這里的介質厚度是指信號到參考層距離。介質層厚度的變化會導致串擾的變化。一般情況下,介質層厚度越小,串擾越小。

如何減小串擾?

從串擾的概念就可以看出,不管怎么樣,串擾是無法消除的。綜上所述,我們可以看到串擾不僅會引入噪聲,還會影響到信號時序。所以很多工程師在進行高速電路設計時,都會非常重視對串擾問題的處理。結合是德科技案例對比以及一些工程經驗,我們對于如何減少串擾可以給出一些基本結論:

? 盡量減短傳輸線之間的耦合長度,盡量保證在耦合飽和長度之內。

? 盡量增加傳輸線之間的耦合距離,能保證3H(H表示傳輸線到參考層的距離)的規則更好。

? 在滿足信號完整性的前提下,盡量使信號的邊沿時間不要過于陡峭,減緩上升的速度。

? 在PCB設計中,對于耦合長度比較長的高速傳輸線,盡量布到內層的帶狀線層,可以大大地減少遠端串擾。當耦合距離比較短時,可以布線到微帶線層,這樣可以減少過孔帶來的影響。

? 在滿足工藝要求的情況下,信號層盡量靠近參考層。

? 在PCB設計中,當相鄰層都是信號層時,布線盡量避免相鄰層平行布線。最好做到垂直布線,使串擾最小化。

? 盡量要滿足傳輸鏈路的阻抗匹配。

? 在空間足夠大的情況下,可以考慮給高速信號線加屏蔽地,屏蔽地上要有適當的地孔。

? 高速傳輸線盡量不要布到PCB板的邊緣,最好保證達到信號到參考層的距離的20H以上。

是德科技的PathWave ADS仿真軟件,可以輕松仿真PCB串擾,結合是德科技的網絡分析儀和PLTS軟件進行串擾的測試,可以完成從概念設計、仿真、原型機設計、驗證到生產制造和部署的全流程管理,從而加速產品開發流程。

3. 開關噪聲

隨著開關切換速度和信號斜率的升高以及器件上有源針腳數目的增加,電源中產生了更多的開關切換噪聲。同時,電路也變得越來越容易受到電源噪聲的影響。單位間隔的減小意味著時間裕量縮小。信號幅度的降低則導致噪聲裕量變小。面對所有工程設計問題,工程師們必須了解它們產生的原因并獲得精確的測量數據,才能分析和解決這些問題。

洞察電源的 “ 噪聲 ”- 電源中沒有任何噪聲是最理想的情況。

如何才能實現這一目標?除了不可避免的熱過程 ( 這通常不是主要的噪聲來源 ) 會產生簡單的高斯噪聲之外,電源上的幾 乎所有噪聲都來自兩個源頭中的一個。電源的開關切換會產生多余的噪聲,這種噪聲通常出現在開關切換頻率的諧波上或與開關切換 頻率一致。此外,當選通和輸出引腳驅動器進行切換時,這個動作將對電源產生瞬態電流需求。在大多數 數字電路中,這通常是最主要的噪聲來源。盡管這些開關切換動作是隨機發生的,但都趨向于 接近系統時鐘。如果我們把這些噪聲的影響視為疊加在電源輸出上的“信號”而不是當成“噪聲”,那么可以 大大簡化分析過程并實現更深入的分析。

4. EMI電磁干擾

在我們的日常環境中,充斥著各種頻率、強度的電磁波,當這些能量影響到電路上的敏感信號時,就產生了不良的電磁干擾影響。有許多形式的EMI電磁干擾會影響電路并阻止它們以預期的方式工作,這種EMI或射頻干擾,它還可以具有各種特性,這取決于其來源和引起干擾的機構的性質。

EMC是什么? - EMC指電磁兼容, 包含EMI和EMS

EMI是什么? - EMI指電磁干擾= 電子設備無意間泄露的電磁能量

EMI測試案例 -利用限制線快速判斷:EMI輻射是否超標

信號分析儀可提供多條限制線

超標的測量結果部分會用紅色標記出來

如何解決信號完整性問題?

我們將介紹如何解決信號完整性問題。我們將展示解決信號完整性問題的三個步驟,以及相關的基礎知識,并將這些技術應用到案例研究中。

讓我們想看一下信號完整性問題的三個步驟包括:

第一步:仿真通道

第二步:確定信號退化的根本原因

第三步:尋找信號完整性設計的解決方案

要完成這三個步驟,我們需要掌握信號完整性問題分析技術。

信號完整性和電源完整性

隨著數據傳輸速率的快速增加,從而使得以前微秒(us)量級的邊沿或保持時間減少到納秒(ns)甚至皮秒(ps)。如此高的帶寬需求使得傳統的設計解決方案已經很難滿足系統正常工作的需求。另外,隨著集成電路的工藝發展使得集成度越來越高,導致芯片上電流密度的急速增加使這個問題更加嚴重。因此非常有必要從整個系統設計開始就考慮信號完整性與電源完整性的問題。這就需要在設計前后把信號完整性和電源完整性仿真引入到設計流程中。

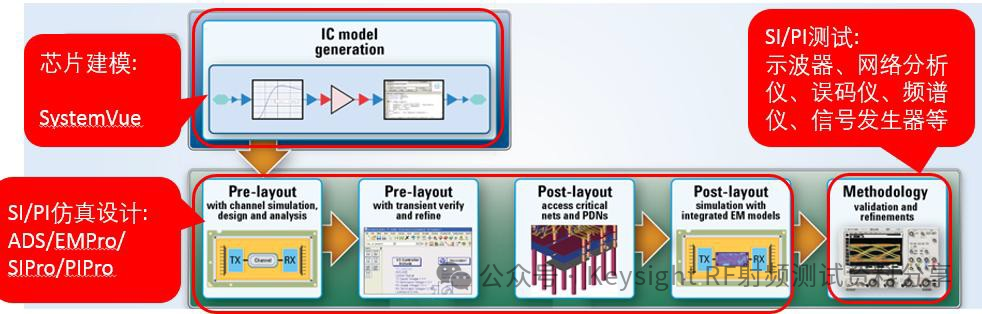

信號完整性和電源完整性產品設計的各個階段都需要考慮。

是德科技在信號完整性和電源完整性領域提供了一套整體的解決方案,包括芯片建模、板級仿真、系統仿真以及產品研發和生產的測試,如下圖1所示:

圖1 是德科技信號完整性和電源完整性流程

芯片的建模和系統級的仿真主要使用 SystemVue。在信號完整性和電源完整性方面,主要應用 ADS 和 EMPro。因為 ADS 中有豐富的模型、操作的靈活性以及對外部的模型也有非常好的兼容性,所以 ADS 應用于信號完整性和電源完整性前仿真和后仿真中。接下來,給大家介紹下 ADS 在信號完整性和電源完整性仿真方面的應用。

信號完整性和電源完整性有什么不同?

在信號完整性中,重點是確保傳輸的邏輯1在接收器中看起來就像 1(對0同樣如此)。在電源完整性中,重點是確保為驅動器和接收器提供足夠的電流以發送和接收1和0。因此,電源完整性可能會被認為是信號完整性的一個組成部分。實際上,它們都是關于數字電路正確模擬操作的分析。

電源完整性分析

分析電源完整性需要進行多項測量,例如配電網絡(PDN)阻抗、電源完整性、電源排序、電源抑制比(PSRR)和控制環路響應。器件設計人員面臨著一大挑戰――如何通過由無源元器件和互連組件構成的 PDN 為汽車、醫療設備和物聯網設備等用電設備提供清潔電力。良好設計的 PDN 可以在從直流到開關電流帶寬的范圍內保持穩定的電壓。它有助于降低功耗和開關噪聲,減少電源引起的抖動以及 EMI 問題。

設計工程師需要使用實時示波器和電源探頭來同時測量多個電源,并詳細觀察信號的交流偏置。高靈敏度電流探頭可以在高靈敏度和衰減模式之間切換,靈活地進行電池功耗分析,而軟件可以分析電源噪聲的來源和影響。在多種溫度條件下進行測量,有助于發現在極端溫度條件下的性能問題。

解決電源完整性挑戰,需要采用本底噪聲較低的測量解決方案,幫助您加速完成電子器件的調試和表征。是德科技電源完整性分析解決方案配備了精密型Keysight MXR 系列實時示波器*(本底噪聲較低,適合進行電源分析)、專用是德科技電源探頭、高靈敏度電流探頭和是德科技電源完整性分析軟件。我們的電源完整性分析解決方案可以幫助工程師驗證向器件和電路輸入的電力是否純凈,確保其產品不會遇到完整性問題。*

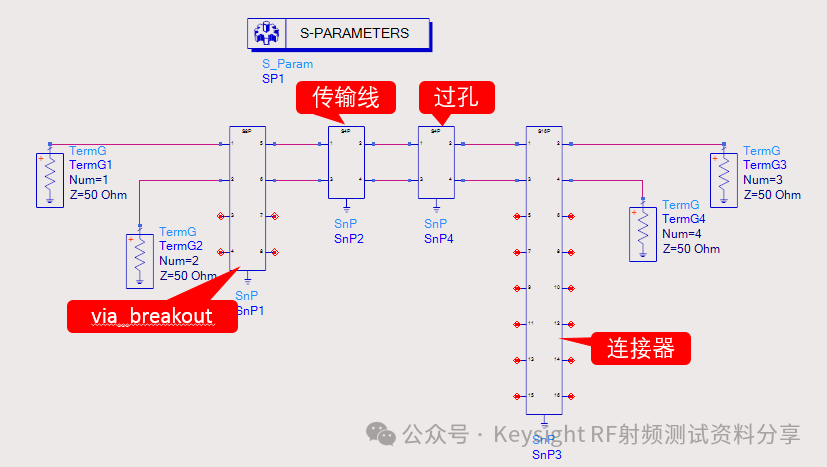

S參數仿真

不管是在信號完整性中,還是電源完整性中,對于很多器件,包括芯片的封裝、傳輸線、過孔、連接器、線纜、電容等無源器件都會應用 S參數來表征其特性,對于一個完整的通道就需要對很多個 S參數進行級聯,在 ADS 中可以非常方便的級聯各類 S參數,并非常靈活的進行 S參數仿真以及數據的處理,如下圖 2 是對多個 S參數的級聯仿真:

圖 2 S參數仿真拓撲結構

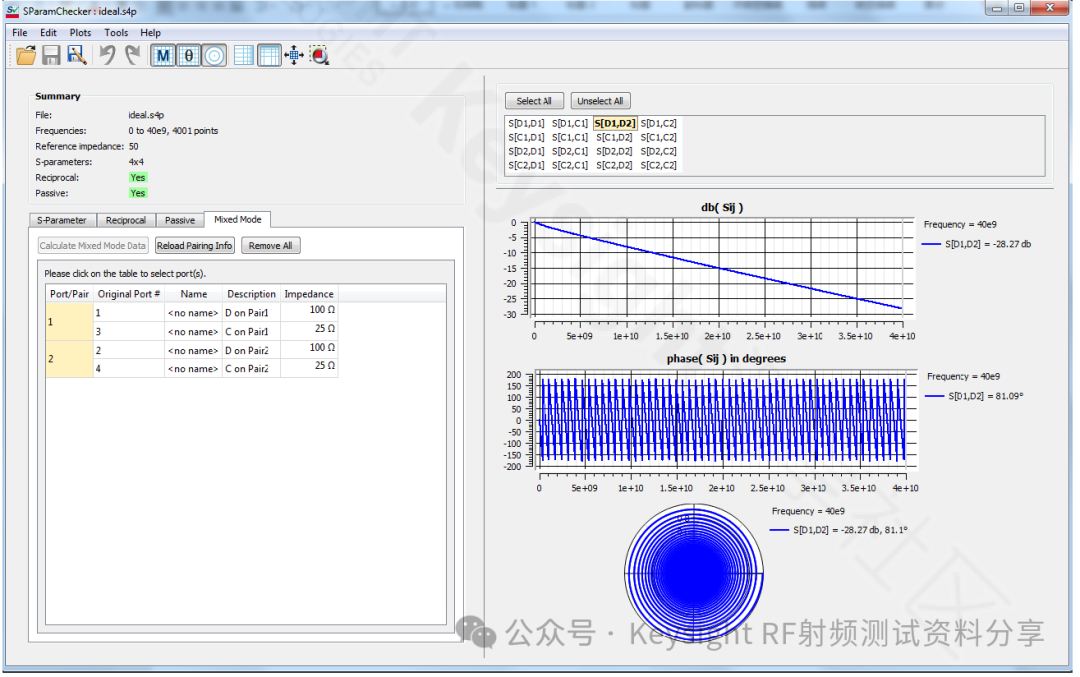

對于單一的 S參數,可以在 ADS 中直接通過 S參數查看器,檢查 S參數的單端和混合模式的結果,如下圖 3 所示,在 S參數查看器中,還可以檢查 S參數的無源性、互易性、相位以及 Smith圓圖。

圖 3 S 參數查看器

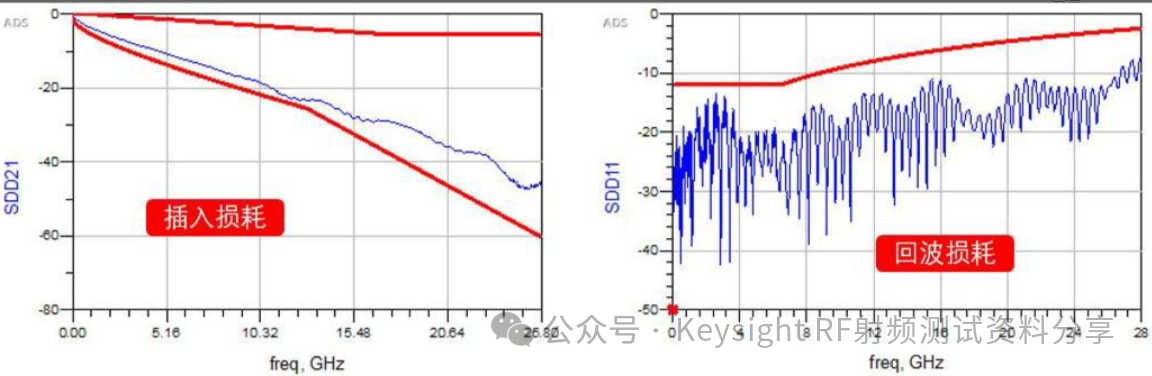

通過 S參數仿真之后,在數據顯示窗口,可以查看結果曲線,也可以進一步處理數據,加入規范模板等等。圖 4 是仿真完成后處理 S參數仿真結果:

圖 4 S參數仿真結果顯示

傳輸線阻抗計算

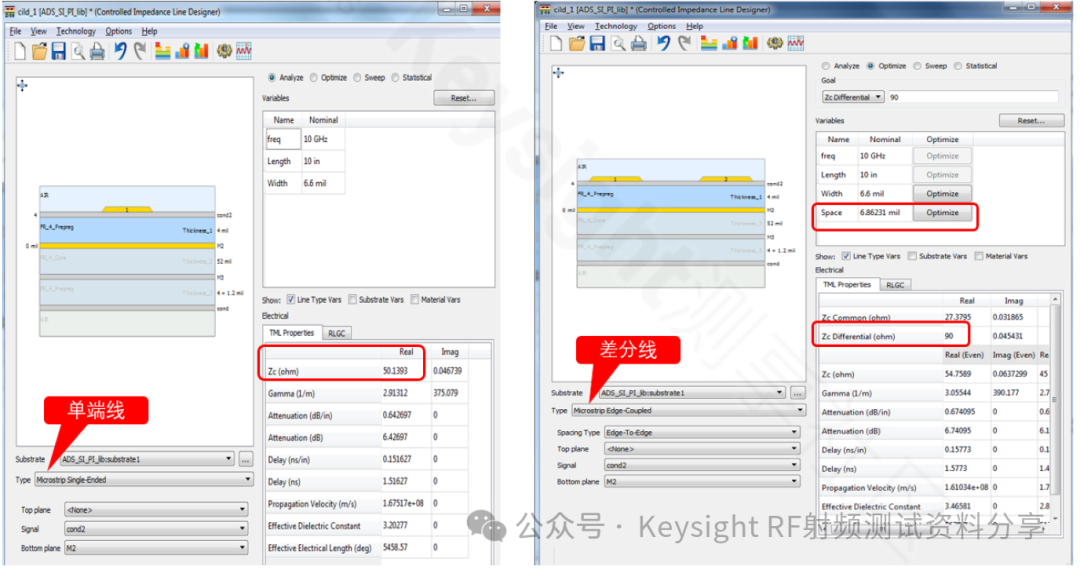

在高速電路中,阻抗匹配非常重要,阻抗不匹配會導致信號的反射、波形非單調、誤碼率增加等等,所以在進行高速電路設計之初,工程師都會考慮使用微帶線、帶狀線還是共面波導結構,并設計一些特定的阻抗類型的傳輸線,比如單端 50ohm、差分 85ohm 或者 100ohm 等等。

在 ADS中采用 CILD(Controlled Impedance Line Designer)可以快速的計算傳輸線的阻抗,并且可以對層疊結構、傳輸線參數、材料參數等掃描優化,獲得目標參數,如下圖 5 所示,左圖為計算 50ohm 的單端傳輸線,右圖為通過優化差分對的線間距,獲得 90ohm 差分線設計參數。

圖 5 傳輸線阻抗計算

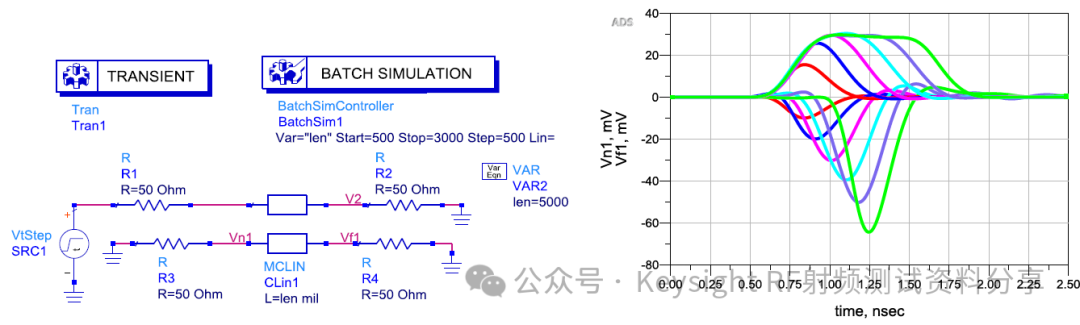

串擾仿真

在現代電子產品追求小而精的狀況下,串擾是每一位工程師必須面對的問題。如何設計可以使串擾最小且不增加成本,是工程師們的追求。在進行 PCB設計之前,都可以通過 ADS 進行串擾仿真,以獲得最優的設計,特別是在設計之初,可以對影響串擾的每一個參數進行掃描仿真,選擇最合適的設計值,如下圖 6 所示為對耦合長度進行掃描仿真的原理圖和仿真結果:

圖 6 串擾仿真

從上圖的結果中在 500mil~1500mil 之間,近端串擾隨著耦合長度的增加而增加, 在 1500mil 之后,近端串擾達到飽和值。這只是一個粗略值的仿真,如果需要獲得更精確的結果,可以進一步的減小仿真的范圍。工程師也可以在 ADS SIPro 中對完成的 PCB進行串擾的仿真,這樣可以更進一步的對設計進行評估。

過孔設計

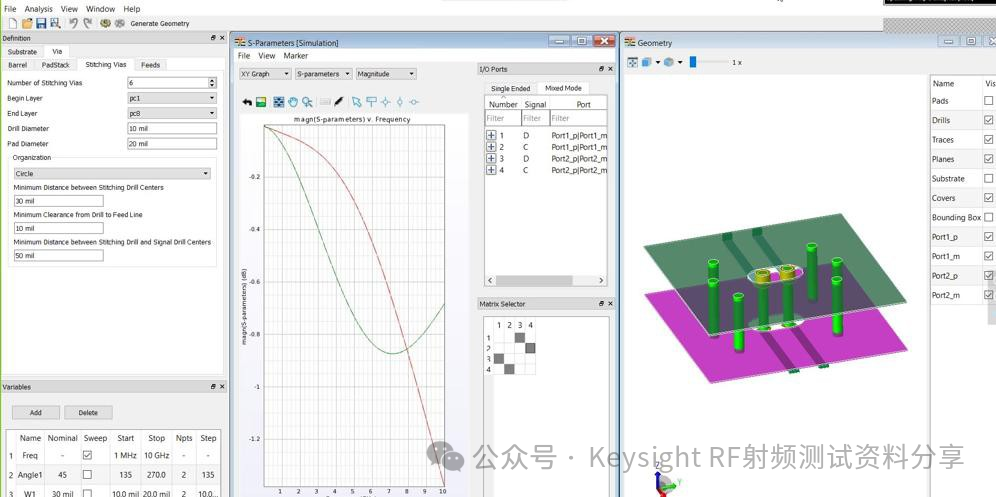

在高速串行信號鏈路中,基本上都會涉及到過孔的設計。過孔設計是高速串行鏈路設計的一個關鍵點,關系到高速串行鏈路設計的成敗。工程師可以通過 ADS Via Designer 工具對過孔進行優化設計,如下圖 7 所示:

圖 7 Via Designer

通過 Via Designer 仿真之后,可以查看過孔損耗和阻抗的特性,并輸出 S 參數模型以及 3D 結構模型,這些模型也可以直接應用在傳輸鏈路仿真中,如下圖 8 所示:

圖 8 過孔模型應用在串行通道仿真中

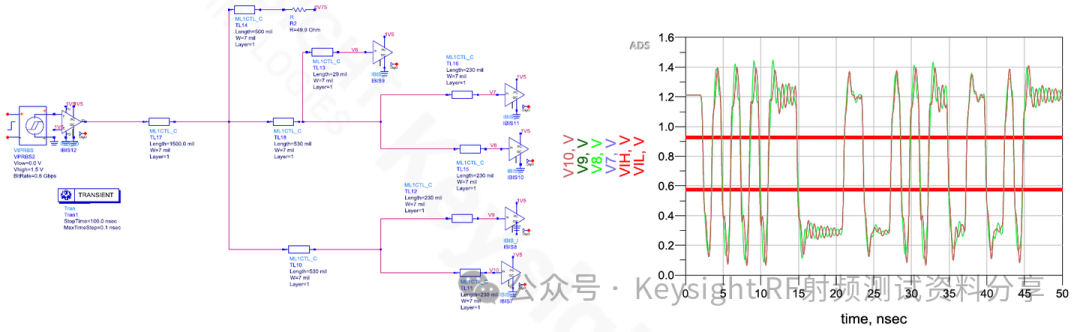

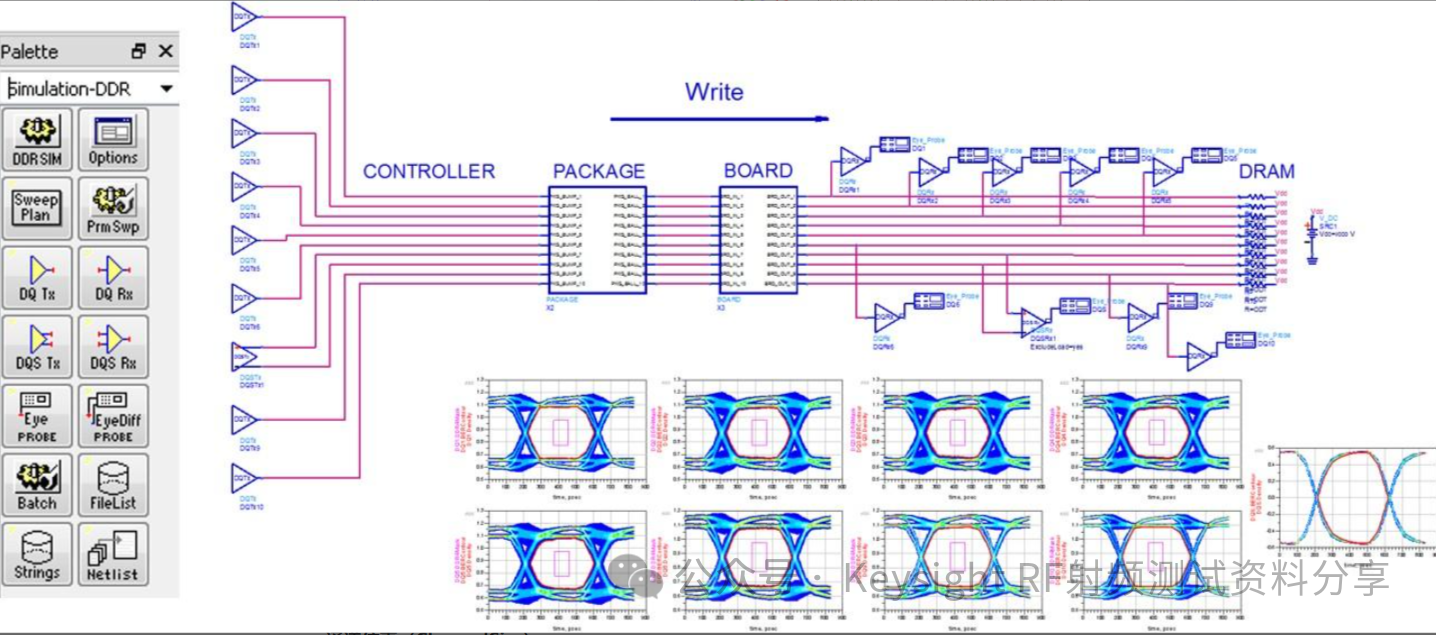

DDR仿真

不管是計算機系統還是嵌入式系統,目前都大規模的采用了 DDR3 或者 DDR4。不論是 DDR3 還是 DDR4,其信號的電源系統的設計都是一個難點,所以不管是前仿真還是后仿真,都需要進行詳細的仿真。在 ADS 中,工程師可以通過兩種方式進行 DDR3/4 總線的仿真,一種是瞬態仿真,如下圖 9 所示;一種是 DDR Bus 總線仿真,如下圖 10 所示。通過仿真,可以優化、確定 DDR總線的布線拓撲結構、端接電阻以及 ODT 的選擇等等。

圖 9 DDR3--瞬態仿真

圖 10 DDR4--DDR Bus 仿真

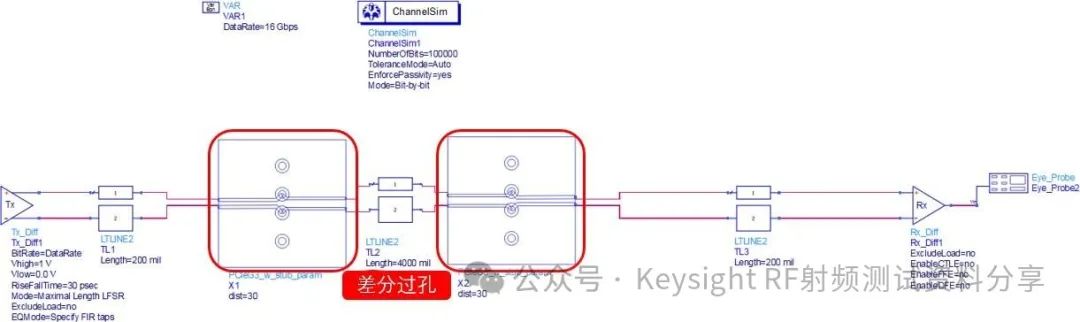

通道仿真(ChannelSim)

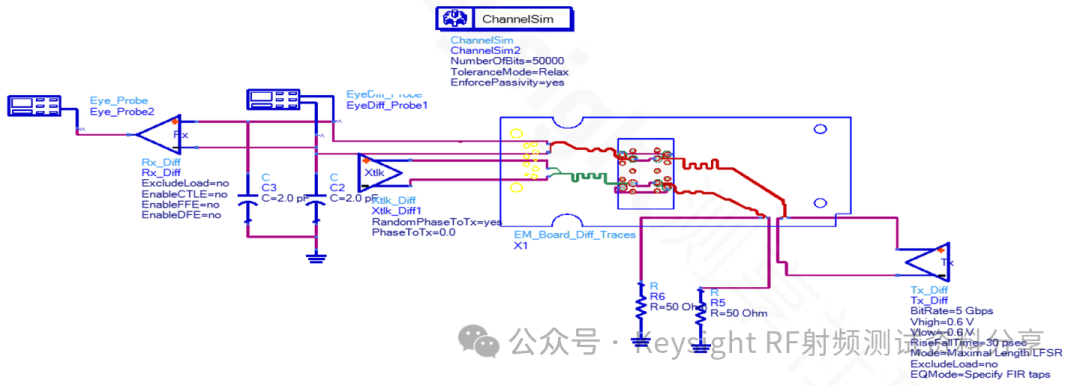

對于高速串行總線,通常對誤碼率有比較嚴苛的要求,要求誤碼率非常低,這才符合總線規范的要求,所以在不管是仿真還是測試,都需要有足夠多的采樣點數或者特殊的數學算法才能滿足分析誤碼率的要求。另外,隨著信號速率的不斷提高,單純的依靠芯片的簡單的驅動能力無法應對信號在傳遞過程中的衰減,所以在高速串行總線的芯片中就會增加加重和均衡的算法,對于仿真而言,也需要有新的分析方法,這就需要使用 ADS 中的通道仿真(ChannelSim),如下圖 11 所示為一個通道仿真的拓撲結構,其中包含了發送端和接收端的芯片模型、傳輸通道上的傳輸線以及連接器以及串擾通道和串擾源。芯片的模型采用的是 IBIS-AMI 模型。

圖 11 通道仿真拓撲結構

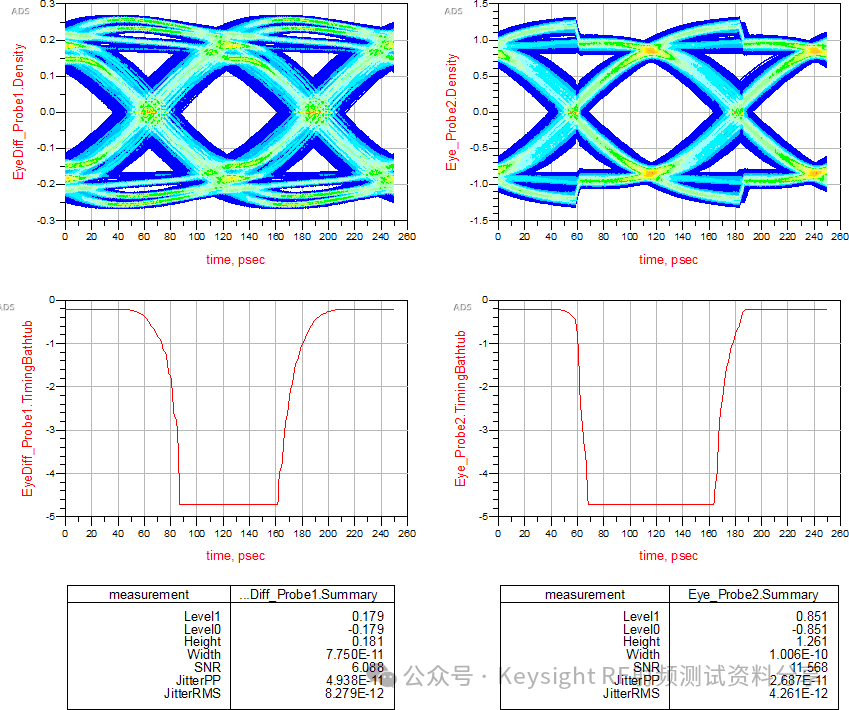

仿真完成之后,在數據顯示窗口上查看波形、浴盆曲線、眼圖等結果。如下圖 12 所示:

圖 12 通道仿真結果

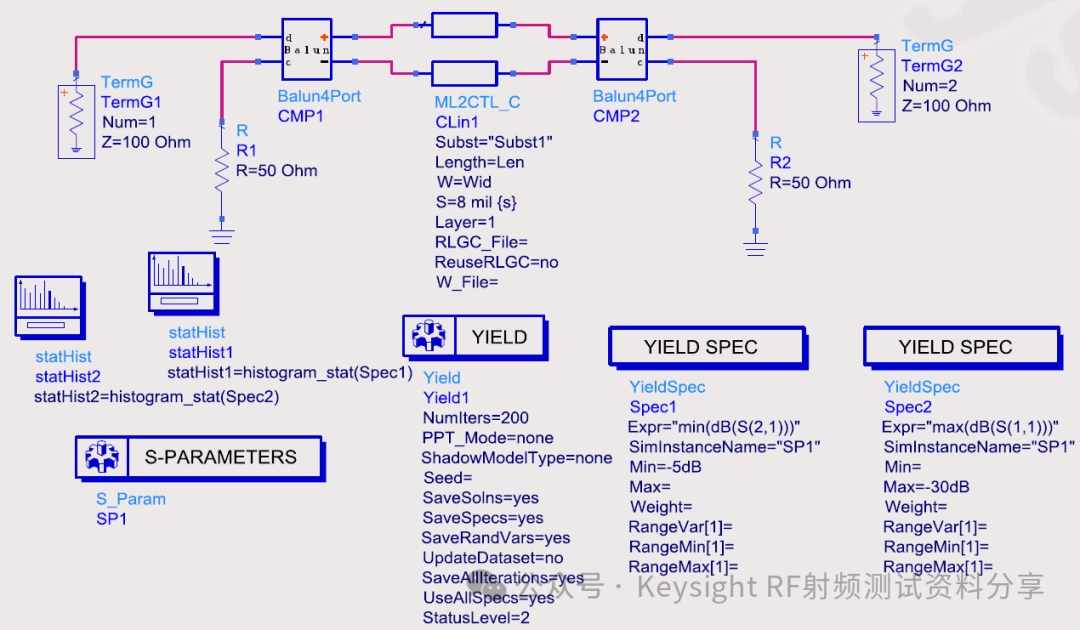

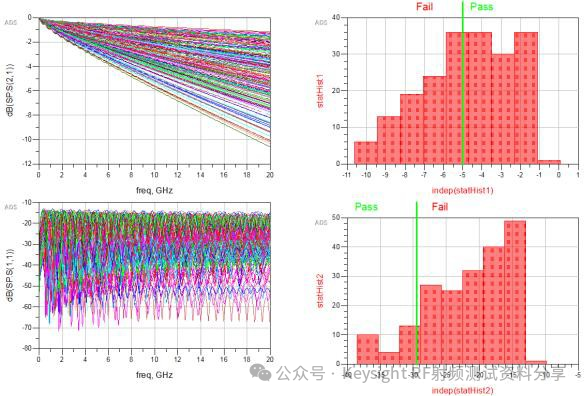

良率分析

在信號完整性前仿真中,工程師不僅僅可以分析既定的一些情況,還可以針對一些不確定的情況做一些統計分析、良率的分析,比如,分析傳輸線長度、線寬、介電常數、介質損耗角等參數對通道的插入損耗和回波損耗的影響。圖 13 為良率分析的拓撲結構和分析結果:

圖 13 良率分析

后仿真流程

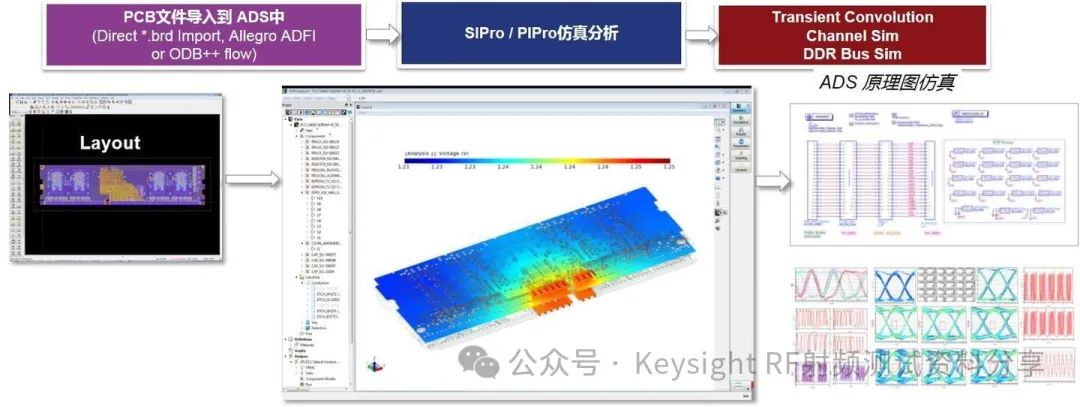

前面介紹了前仿真,主要是針對原理圖階段的仿真,目的是驗證原理圖設計以及給PCB設計提供約束規則。那么當 PCB設計完成之后,還需要進行后仿真,這時需要把設計好的 PCB文件導入到 ADS 中,然后再通過 SIPro 和 PIPro 進行信號完整性和電源完整性的后仿真,仿真完之后,獲得結果;也可以把仿真的結果或者提取的模型導出到 ADS原理圖頁面,做進一步的仿真。具體流程如下圖 14 所示:

圖 14 后仿真流程

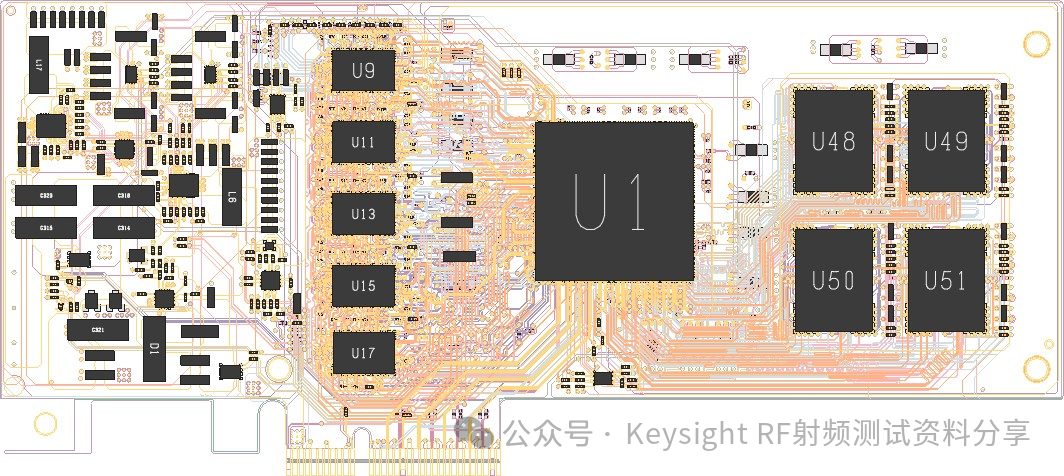

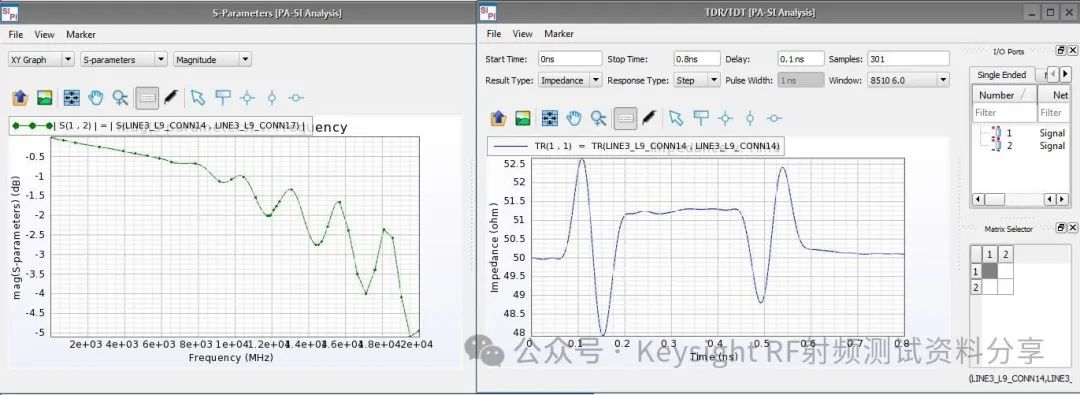

在 ADS SIPro 中進行信號完整性的后仿真可以獲得 S參數模型,同時可以查看信號網絡的阻抗,并能導出 S參數模型,如下圖 15 和圖 16 所示:

圖 15 SIPro 中PCB 仿真圖

圖 16 SIPro 仿真后的 S參數和阻抗曲線

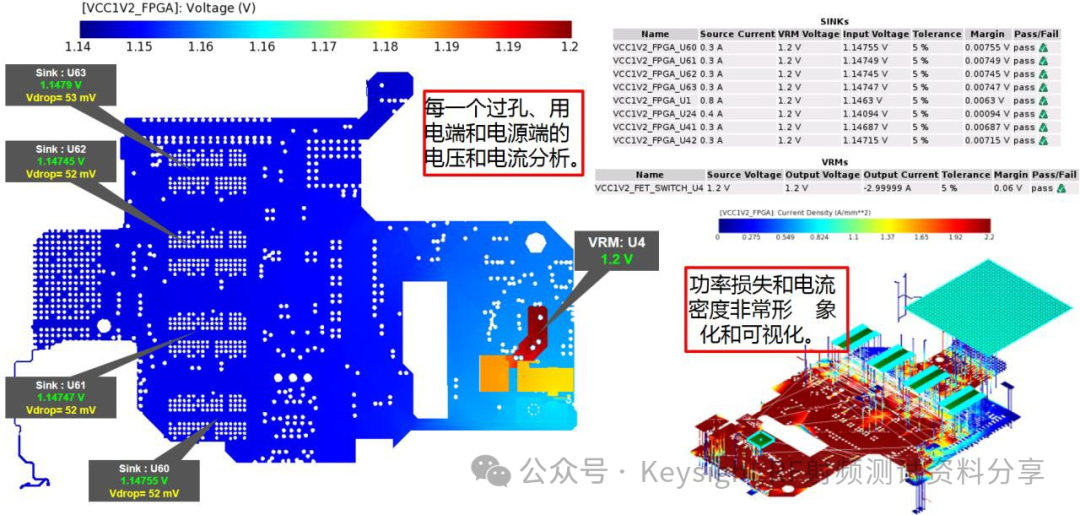

在 ADS PIPro 中可以進行電源完整性的直流壓降仿真(PI DC)、直流電熱聯合仿真(Electro-Thermal)、熱仿真(Thermal)、交流阻抗仿真(PI AC)和平面諧振仿真(Power Plan Resonance)。如下圖 17 為直流壓降仿真結果,圖 18 為交流阻抗仿真結果。

圖 17 直流壓降仿真結果

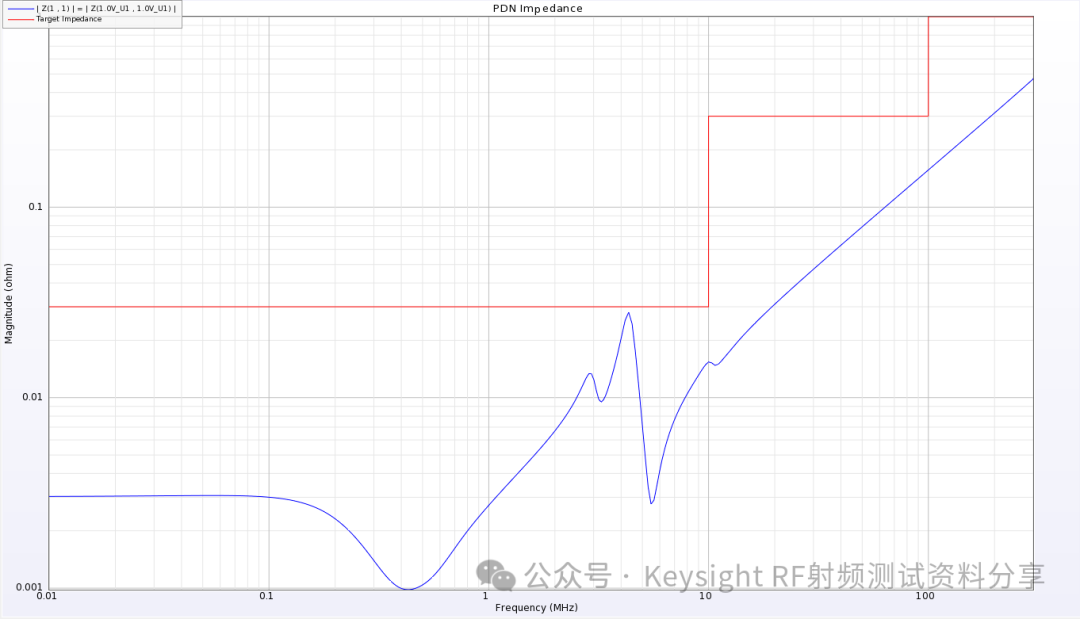

圖 18 PDN阻抗仿真結果

在 PIPro 中還可以對不滿足 PDN 阻抗要求的設計進行去耦電容自動優化,通過對不同的電容組合、電容種類進行自動分析,找到一種最合適的設計。也可以把 PDN 的 S參數提取之后導出到 ADS原理圖中,在原理圖中也可以進行優化仿真分析。

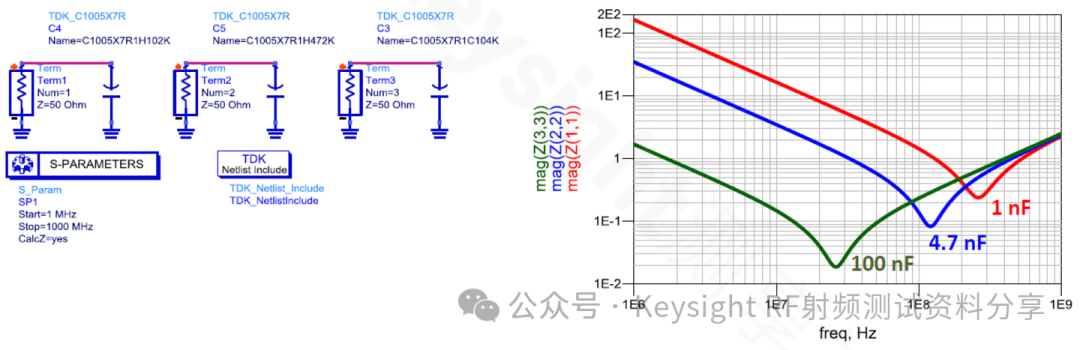

當然,也可以在前仿真中對電源完整性進行仿真,這樣可以對電容的組合進行優化。在 ADS原理圖中建立相應的拓撲結構,如下圖 19 所示:

圖 19 電容阻抗仿真

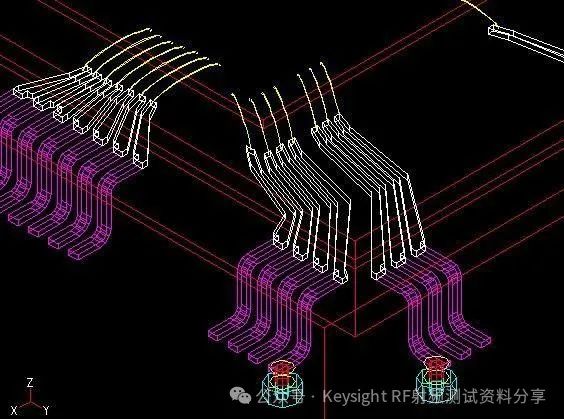

在信號完整性仿真階段,EMPro 也是不可或缺的工具,特別是對于一些比較復雜的結構,比如具有芯片封裝、連接器、線纜的互連通道,就需要使用 EMPro 進行電磁模型的提取。如下圖 20 所示 EMPro 中進行芯片封裝的仿真:

圖 20 芯片封裝仿真

隨著技術的發展,信號完整性和電源完整性設計和仿真也變得更加的復雜,這對工具的要求也越來越高。比如近幾年比較熱門的PAM4,雖然這個仿真依然使用的是通道仿真技術,但是其所需要的仿真激勵源已經變得更加的復雜。所幸的是,是德科技也持續的在研發新的技術,利用 ADS可以非常方便的對 PAM4 進行仿真。

總之,不管信號完整性和電源完整性的前仿真還是后仿真,或者,不管是板級仿真還是系統仿真,是德科技都能提供一套非常系統的解決方案。

-

信號完整性

+關注

關注

68文章

1408瀏覽量

95462 -

時鐘頻率

+關注

關注

0文章

50瀏覽量

20343 -

是德科技

+關注

關注

20文章

878瀏覽量

81782

原文標題:什么是信號完整性?如何三步解決信號完整性問題?

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

常見的信號完整性問題及解決方案

高速DSP 數據采集的信號完整性問題

數字電路設計的信號完整性問題探討

識別和修復pcb信號完整性問題

什么因素導致信號完整性問題?

PCB設計中的信號完整性問題

如何解決信號完整性問題

如何解決信號完整性問題

評論