導讀

隨著網絡需求增長,千兆以太網速率問題備受關注。本文針對其實際速率低的情況,詳細分析布線不佳等原因,并從等長走線、阻抗匹配等硬件方面及軟件調試角度,提供全面提升速率與穩定性的有效方法。

正常的千兆以太網理論速率可以達到1000Mbps,實際考慮到通信各個環節的損耗,也應在800Mbps以上。而實際上卻有很多板卡,按照參考電路設計的千兆以太網實測只卻只能跑到300/400Mbps,甚至更低。這種情況90%是由于以太網布線不佳導致的信號完整性問題。千兆以太網RGMII信號的速率高達125MHz,而且是雙邊沿觸發的,所以對信號完整性是有要求的。以下的RGMII信號完整性原則和方法,可以幫助優化和改善以太網的速率和穩定性。

1. 等長走線

RGMII在走線時必須要進行等長處理。等長即RGMII總線中的TX_CLK、TXD[0:3]、TX_EN這6個信號為一組,RX_CLK、RXD[0:3]、RX_EN這6個信號為一組,分別繞蛇形走線,使得每組組內信號線之間長度差值在100mil以內,不同廠家的公差要求可能不同,但對硬件工程師來說,條件允許的情況下,公差越小,則時序裕量越大,設計時應盡量將公差縮小。注意這個公差應該是CPU的MAC到PHY芯片的走線,有些核心板的手冊標注了核心板RGMII走線長度和CPU內部的長度,此時必須要將它們和底板的長度加起來計算等長。

2. 阻抗匹配

RGMII的所有信號線要求單端50Ω的阻抗匹配,50Ω是一個約定俗成,沿用至今的值,也是板廠熟悉,易于疊層和制板的取值。阻抗匹配指的特征阻抗,定義是:傳輸線長度趨近于無窮大時,傳輸線的阻抗是多少(例如上述的50Ω)。在有限長傳輸線中,它表征電信號經過導體瞬間的阻抗,但這個值不是50Ω,阻抗匹配即有限長傳輸線中每一處的特征阻抗都是相等的、均勻的、連續的。設計時,它是由PCB的銅厚、線寬、相鄰層間距、板材等計算得來的。對設計師來說,最重要的是阻抗的連續性,電信號經過阻抗不連續的導體,如同光線經過密度不同的介質(水和空氣)時產生反射與折射,信號就會失真。傳輸線打孔、換層、經過電阻和連接器的焊盤、有分叉,都會導致不同程度的阻抗不連續。所以layout時應避免分叉、走線改變方向用45度折彎,盡量避免打孔換層。

3. 完整的參考平面

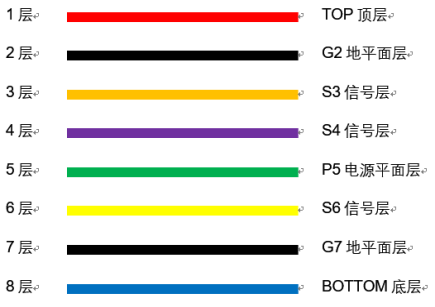

參考平面對阻抗匹配是非常重要的,傳輸線原理中,傳輸線包含信號線和回流路徑,當信號線是均勻連續的,但參考平面不連續也會導致傳輸線不連續。參考平面是根據疊層確定的,一般是相鄰的平面層,例如圖1中,8層板疊層1層和3層參考2層,4層參考5層,6層和8層參考7層。信號線投影區域內參考層的銅皮也不能中斷或改變網絡。容易出問題的地方是換層的時候如果信號從1層打孔到了8層,那么參考層就從2層變成了7層,建議在信號換層位置200mil范圍內打地過孔創造回流路徑。有條件的地方也應補上地過孔增強兩層地的連續性。那么當信號從1層換層到4層,參考層由GND變成了PWR,網絡都改變了,這時該怎么辦呢?這種情況可以在換層位置附近布置0.1uF的縫合電容將2層和5層的網絡連在一起。

圖1 一種常見8層板疊層結構圖

4. 避免源端反射

前面講過阻抗匹配,當信號傳輸到接收端,RGMII的接收IO是高阻的,信號就會反射回去,反射波到達源端又發生二次反射,叫做源端反射。源端反射會和原始信號疊加在一起形成過沖、振鈴等,影響信號質量。通過在靠近信號發送端的位置串聯源端匹配電阻,可以有效降低源端反射。有些芯片推薦的匹配電阻是33Ω,有些是22Ω,這是因為芯片管腳驅動器的輸出阻抗不同,當驅動器輸出阻抗+源端匹配電阻的阻值為50Ω左右的時候,配合50Ω的阻抗匹配,防止源端反射的效果才最好,而這也是串阻要靠近信號源端的原因。

5. 防止串擾

外部的干擾也是不能忽視的,檢查諸如走線之間有沒有保持3W間距,時鐘走線有沒有包地。類似圖 1.44的疊層中3層和4層的走線有沒有和相鄰層的其它走線有長距離、近距離的平行走線等等,在這些地方往往也能找到能夠優化的點。

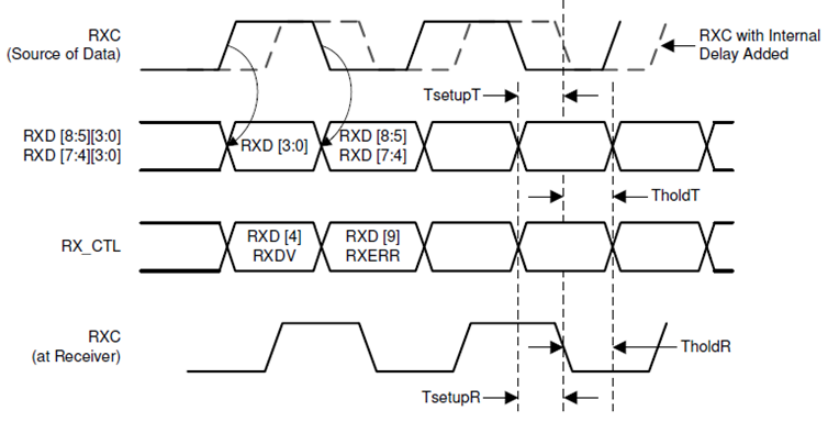

6. 軟件Delayline調試

如果板子調試時發現速率不夠,其實也不一定就是硬件問題,可以先看下軟件有沒有進行Delay line的配置。Delay line就是在CLK上增加一段無用的buffer來達到延時的效果,通過調整buffer數量,來補償PCB走線的延時,最終使得接收端接收到的時鐘邊沿移動到數據眼圖的正中間。一般MAC端和PHY端都可以進行Delay line的調節,但MAC端調節的精度更細,操作也更方便,一般將PHY端的Delay line設為0,只在MAC端調節。

圖2 Delayline電路結構示意圖

圖3 Delayline調整波形示意圖

剛開始調Delay line時,網絡有可能完全ping不通,同時沒法區分是發送有問題還是接收有問題,所以要借助PC端的Wireshark先調試發送數據。MAC端調節Delay line每個步進增加0.08ns延時,待調試的板子在后臺ping PC的IP,輸入命令讓板子遍歷所有TX Delay line,此時觀察電腦端的Wireshark,會看到從某個值開始收到板子發來的ICMP包,稱為窗口的開始;隨著TX delayline逐漸增加,收到的數據包會變得更完整,接著變得不完整,最后徹底收不到板子發來的ICMP包,此時的TX Delay line值稱為窗口的結束。取窗口開始和結束的中間值作為此PCB板的TX Delay line最優值,記下這個值。調通板子網卡的發送功能之后,板子就具備了應答ping ICMP包的能力。下面在電腦端綁定板子網卡的MAC地址和IP地址,并開始ping板子的IP地址,板子執行以下命令遍歷所有RX Delay line,觀察電腦端ping命令的返回信息,會看到ping返回失敗,漸漸變成ping成功,而后又變為ping失敗,記錄下這些節點對應的RX Delay line值。ping成功的這段區間稱為接收窗口,同樣取其中值,作為RX Delay line的最優值。最后把Delay line最優值設置,添加到設備樹的gmac節點中,固化Delay line,完成Delay line的配置。要注意的是,使用RGMII接口連接千兆PHY時,只要硬件存在差別,都需要重新做一次Delay line的配置。另外可以調整Delay line也不代表硬件不需要做等長Layout;如果不做等長,意味著時鐘信號的跳變邊沿要同時對四條數據線的相位進行延時微調,它們重疊的區域才能對數據正確采樣,但這個區域將會變得過窄,甚至超出Delay line延時的范圍。

7. 調整驅動強度

除了配置Delay line,還可以調整RGMII的驅動強度進一步改善問題。當使用iperf長時間測試發送會掉線也可以嘗試調整驅動強度。當將驅動強度調高時,信號的邊沿會變得更陡峭,但與此同時,過沖和振鈴也會變強,驅動強度調低時,信號邊沿會變緩,但能夠減少過沖和振鈴的影響。驅動強度通常只有幾個檔位(通常4或8檔),有些廠商會標出是多少mA,有些則只標出強度等級,沒有具體單位,所以不用像Delay line那樣找最佳值,實測在不同強度下速率最高,穩定性最好的取值即可。

-

以太網

+關注

關注

40文章

5541瀏覽量

174032 -

阻抗匹配

+關注

關注

14文章

357瀏覽量

31190 -

阻抗

+關注

關注

17文章

967瀏覽量

46788 -

通信

+關注

關注

18文章

6138瀏覽量

137123 -

帶寬

+關注

關注

3文章

985瀏覽量

41567

發布評論請先 登錄

相關推薦

評論