前言

S參數(shù)測量是射頻設(shè)計(jì)過程中的基本手段之一。S參數(shù)將元件描述成一個黑盒子,并被用來模擬電子元件在不同頻率下的行為。在有源和無源電路設(shè)計(jì)和分析中經(jīng)常會用到S參數(shù)。

S參數(shù)是RF工程師/SI工程師必須掌握的內(nèi)容,業(yè)界已有多位大師寫過關(guān)于S參數(shù)的文章,即便如此,在相關(guān)領(lǐng)域打滾多年的人, 可能還是會被一些問題困擾著。你懂S參數(shù)嗎? 請繼續(xù)往下看

基礎(chǔ)篇

1、簡介:從時域與頻域評估傳輸線特性

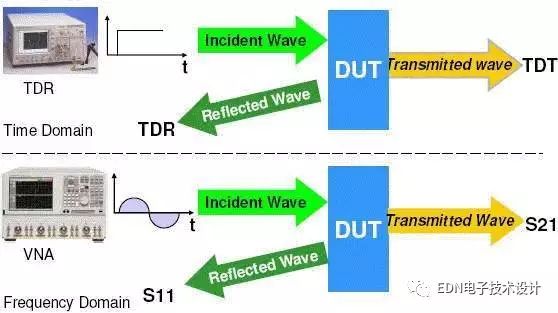

良好的傳輸線,訊號從一個點(diǎn)傳送到另一點(diǎn)的失真(扭曲),必須在一個可接受的程度內(nèi)。而如何去衡量傳輸線互連對訊號的影響,可分別從時域與頻域的角度觀察。

S參數(shù)即是頻域特性的觀察,其中"S"意指"Scatter",與Y或Z參數(shù),同屬雙端口網(wǎng)絡(luò)系統(tǒng)的參數(shù)表示。

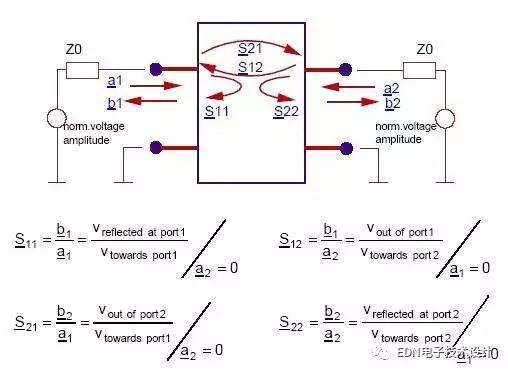

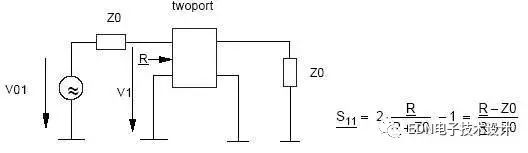

S參數(shù)是在傳輸線兩端有終端的條件下定義出來的,一般這Zo=50奧姆,因?yàn)閂NA port也是50奧姆終端。所以,reference impedance of port的定義不同時,S參數(shù)值也不同,即S參數(shù)是基于一指定的port Zo條件下所得到的。

2. 看一條線的特性:S11、S21

看一條線的特性:S11、S21

如下圖所示,假設(shè)port1是訊號輸入端,port2是訊號輸出端

S11表示在port 1量反射損失(return loss),主要是觀測發(fā)送端看到多大的的訊號反射成份;值越接近0越好(越低越好 ,一般-25~-40dB),表示傳遞過程反射(reflection)越小,也稱為輸入反射系數(shù)(Input Reflection Coefficient)。

S21表示訊號從port 1傳遞到port 2過程的饋入損失(insertion loss),主要是觀測接收端的訊號剩多少;值越接近1越好(0dB),表示傳遞過程損失(loss)越小,也稱為順向穿透系數(shù)(Forward Transmission Coefficient)。

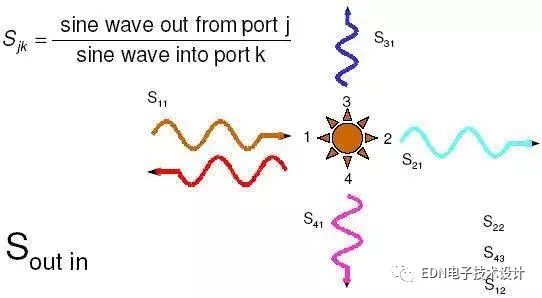

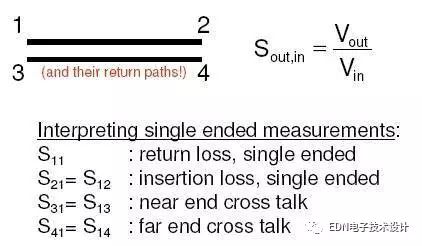

3、看兩條線的相互關(guān)系:S31、S41

雖然沒有硬性規(guī)定1、2、3、4分別要標(biāo)示在線哪一端,但[Eric Bogatin大師]建議奇數(shù)端放左邊,且一般表示兩條線以上cross-talk交互影響時,才會用到S31。以上圖為例,S31意指Near End Cross-talk (NEXT),S41意指Far End Cross-talk (FEXT).

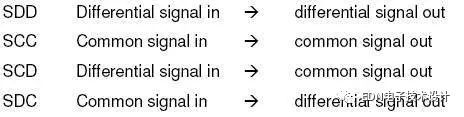

4、看不同模式的訊號成份:SDD、SCC、SCD、SDC

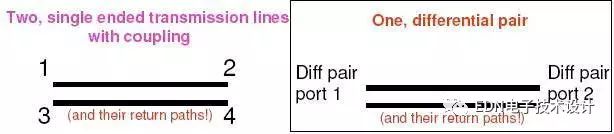

以上談的都是single ended transmission line (one or two line),接著要談differential pair結(jié)構(gòu)。

5、以史密斯圖觀察S參數(shù)

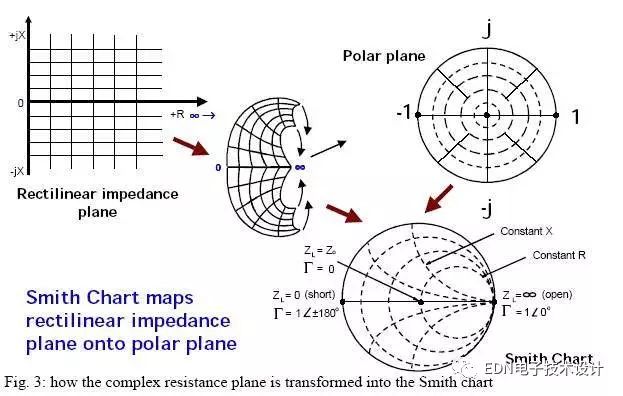

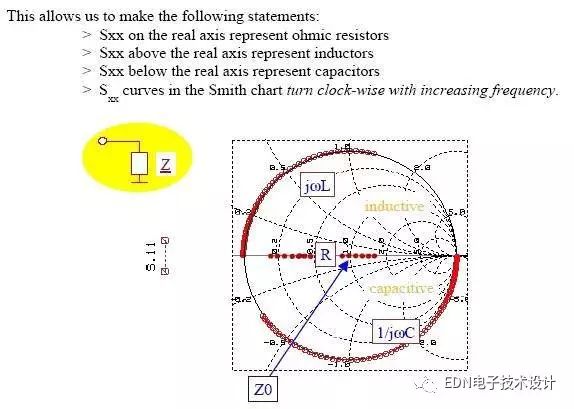

因?yàn)镾11、S22是反映傳輸線的reflection,不難理解S11其實(shí)也可以直接以反射系數(shù)表示。

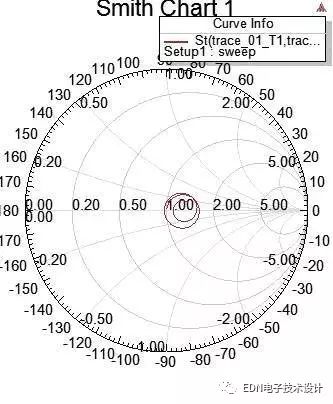

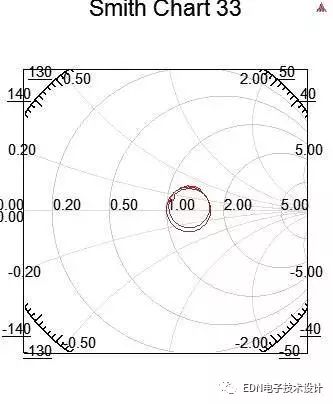

既然是反射系數(shù),那就可以用史密斯圖來觀察了,史密斯圖可以想做是把直角坐標(biāo)的Y軸上下盡頭拉到X軸最右邊所形成

水平軸表示實(shí)數(shù)R,水平軸以上平面表示電感性,水平軸以下平面表示電容性

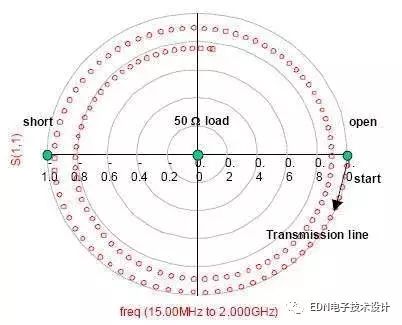

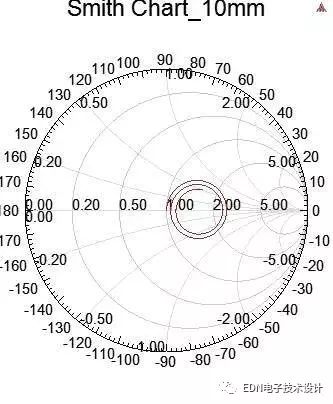

以一條四英寸長,50歐姆的傳輸線為例,從15M~2GHz的史密斯圖,S11會呈現(xiàn)螺旋狀往圓心收斂,而這螺旋就是dielectric losses absorb造成,越高頻loss越大。

6、仿真范例

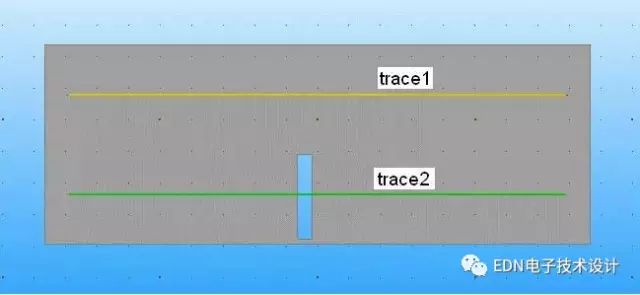

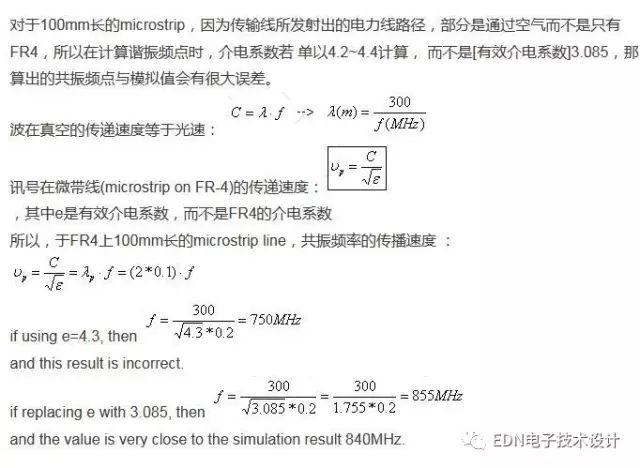

取一條100mm長,線寬7mils、銅厚0.7mils、堆棧高4mils,特性阻抗50奧姆的microstrip,以下方reference plane是否有被slot切開做比對。Trace1的地回路是完整的,而Trace2的地有一個橫切的slot造成地回路不連續(xù)。

6.1

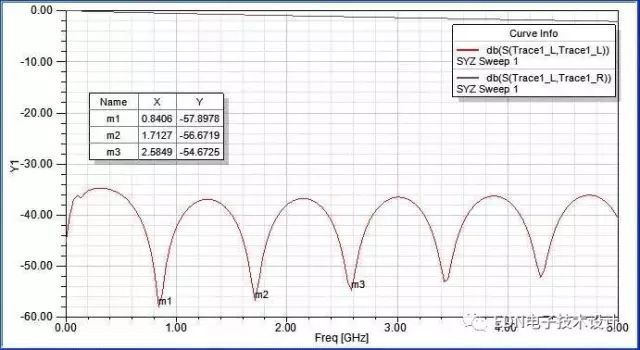

觀察Trace 1的S11、S21:S11從1~5GHz都維持在-35dB以下,表示反射成份很小;S21從1~5GHz都很接近0dB,表示大部分的訊號成份都完整的從port 1傳到port 2。

一條良好的傳輸線,S11、S21會拉蠻開的,隨著頻率增加彼此才會慢慢靠近一些 。另外,從S11可以很清楚看到由線長所決定的共振頻點(diǎn).

一般50歐姆特性阻抗的microstrip on FR4,有效介電限數(shù)大約3.0~3.1,可以透過Design/Nexxim得到.

6.2

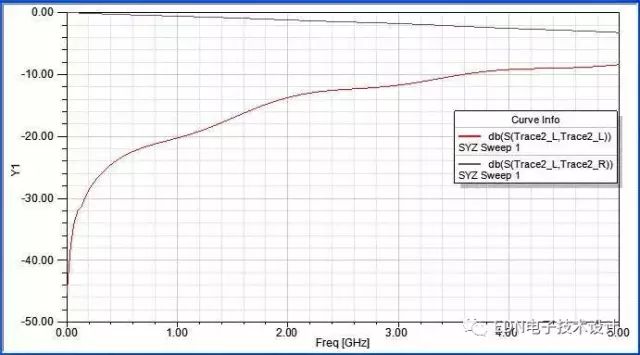

觀察Trace 2的S11、S21:S11在1GHz以上時,就超過-20dB了,表示反射成份很大;S21與Trace1比較起來,隨頻率降低的速度也大一倍,表示有較多訊號成份在port 1傳到port 2的過程中損耗。

7.問題與討論

7.1 埠端阻抗是如何影響S11參數(shù)的?

Ans:端口阻抗(referenced impedance, Zport)會影響Zin,進(jìn)而影響S11

For the transmission line with characteristic impedance Zo, the max. impedance referenced to Zport is Zin=Zo*2/Zport ,S11=(Zin-Zport)/(Zin+Zport)

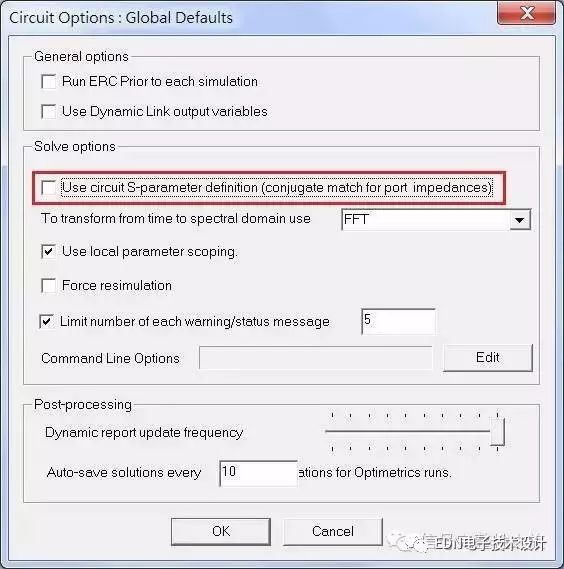

在HFSS內(nèi),上式S11中的Zport以實(shí)數(shù)考慮(non-conjugate matched load for S-parameter),而在Designer或一般電路仿真軟件中,上式S11中的Zport以復(fù)數(shù) 考慮(conjugate matched load for S-parameter)。在 一些天線或waveguide的應(yīng)用中,如果埠 端阻抗含虛部,而又希望可以在Designer內(nèi)看到跟HFSS的S參數(shù) 同樣結(jié)果,可從以下設(shè)定[Tools] [Options] [Circuit Options],un-check [Use circuit S-parameter definition]。

請注意:這只是S參數(shù)埠端定義的不同,結(jié)果 都是對的,所以不管哪一種定義下,如果轉(zhuǎn)到Y(jié)或Z參數(shù)(或是從Designer透過dynamic link HFSS)去看,其值是一樣的。

7.2 Touchstone file (.snp)跟S-parameter是什么關(guān)系?

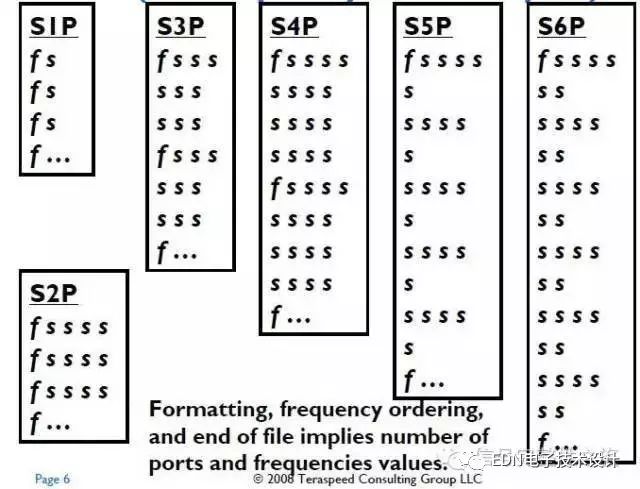

Ans:Touchstone file (.snp)是基于每個頻點(diǎn)的S參數(shù),所定義的一種頻域模型,其格式如下所示:

7.3 為何端口阻抗會影響S參數(shù),但不影響Z參數(shù)(Z11)?

Ans:Z11=Vi/Iin與埠端阻抗無關(guān)。

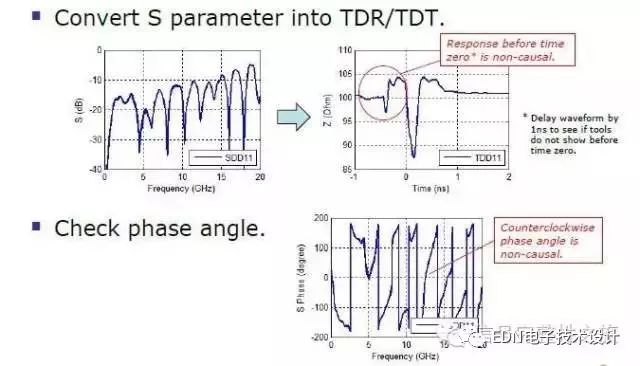

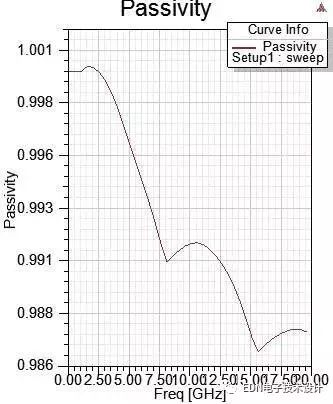

7.4 除了靠軟件,還有其他方法檢查Passivity、Causality嗎?

Ans:如圖所示,透過觀察TDRNEXTFEXT是否在T=0之前有響應(yīng)。

7.5 史密斯圖(Smith Chart)與Causality、Passivity是否有關(guān)聯(lián)性?

Ans:有的

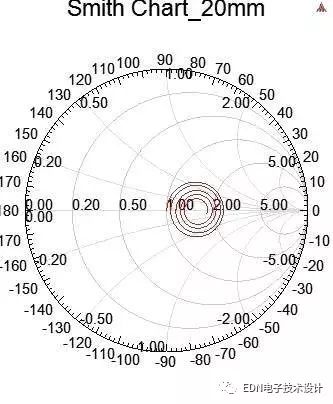

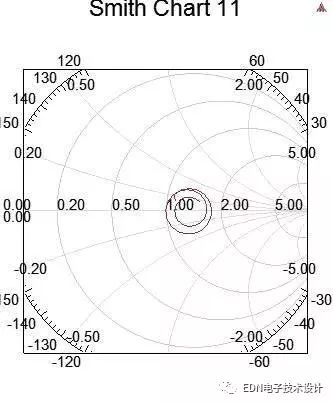

7.5.1 滿足Causality與Passivity傳輸線的史密斯圖,會呈現(xiàn)以順時針方向往中心螺旋收斂的曲線。

將線長從10mm拉長一倍到20mm,發(fā)現(xiàn)越長的線,其Smith Chart中隨頻率增加而順時針向中心旋轉(zhuǎn)收斂的步幅也會增加。

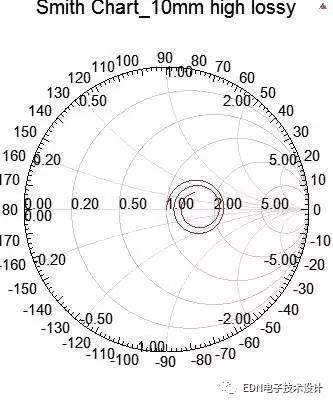

把介質(zhì)loss tangent從0.02改0.06,發(fā)現(xiàn)Smith Chart中隨頻率增加而順時針向中心旋轉(zhuǎn)的收斂會加快。順時針向中心旋轉(zhuǎn)與lossy有關(guān)。

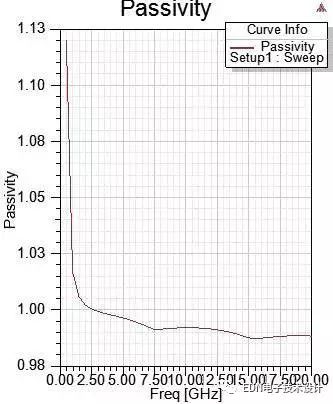

7.5.2 滿足Causality但a bit violate Passivity傳輸線的史密斯圖,會出現(xiàn)部份頻段貼合,沒有往中心 旋轉(zhuǎn)收斂。

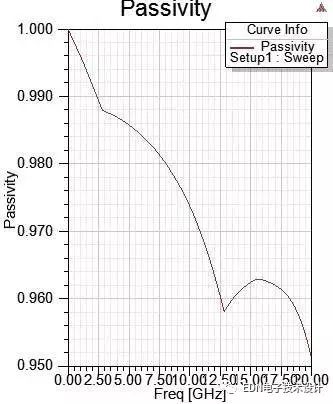

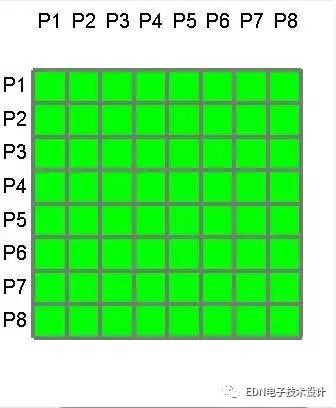

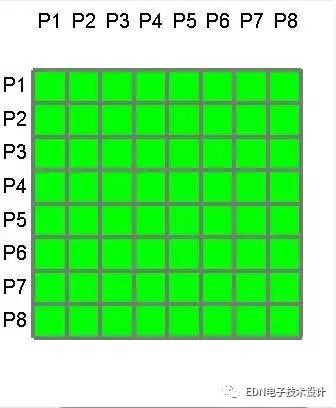

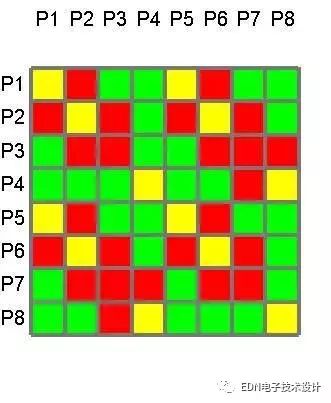

近幾年的HFSS性能一直提升,想要用簡單的例子搞出non-passivity還不太容易。本例是四條傳輸線(.s8p),故意 降低mesh performance(放大error percentage=0.1%),低頻DC~0.1GHz刻意不求解,并且使用lossless介質(zhì)。

7.5.3 non-causality and non-passivity的史密斯圖,相對于n*n matrix中不同矩陣區(qū)塊內(nèi)的violate程度,曲線可能會折彎 (低頻violate passivity嚴(yán)重,在Smith Chart也看到低頻曲線有不規(guī)則的折彎),或是不往中心收斂

筆者還看不到HFSS產(chǎn)生的non-causal S參數(shù)的Smith Chart會逆時針旋轉(zhuǎn),或其時域響應(yīng)提前發(fā)生的現(xiàn)象 。但可以用Designer內(nèi)的de-embedded功能產(chǎn)生逆時針旋轉(zhuǎn)的Smith Chart。

8、Reference

[1] Chapter1 -- 宜蘭大學(xué), 邱建文教授[2] In-Situ De-embedding (ISD) p.6~8 from AtaiTec Corp. (推薦)[3] Power Integrity for I/O Interfaces: With Signal Integrity/ Power IntegrityIn a passive high-speed channel, the speedy way to check for causality is to examine the S-parameter Smith Chart. If the data rotate clockwise, it has positive group delay; implying it to be causal. On the other hand, if the data rotates counterclockwise, this implies it is noncausal.[4] 一篇利用Smith Chart補(bǔ)償Passivity與Causality的專利技術(shù)Smith Chart can be used to monitor the passivity and causality of networks under study. For instance, Foster's reaction theorem dictates a general motion in the clockwise direction with frequency for the parameters of an arbitrary network.[5] touchstone spec. 2.0[6] TS1.0 and TS2.0 (推薦)[7] Converting S-Parameters from 50Ω to 75Ω Impedance[8] Scattering Parameters:Concept, Theory, and Applications[9] RF Matching Design[10] Why have non-causality (推薦)

進(jìn)階篇

目錄

1、前言2、個別S參數(shù)與串聯(lián)S參數(shù)的差別3、雙埠S參數(shù)對地回路效應(yīng)的處理4、兩個2-port S參數(shù),有可能組成一個4-port S參數(shù)嗎?5、全3D模型的S參數(shù),與分開的3D模型S參數(shù)串連的差別?6、Port阻抗的設(shè)定,對S參數(shù)本質(zhì)上,與S參數(shù)的使用上,有沒有影響?7、Export S參數(shù)模型時,有沒有做port renormalize to 50 ohm,對使用S參數(shù)有沒有影響?8、問題與討論

1、前言

S參數(shù)是SI與RF領(lǐng)域工程師必備的基礎(chǔ)知識,大家很容易從網(wǎng)絡(luò)或書本上找到S,Y,Z參數(shù)的說明,筆者也在多年前寫了S參數(shù) -- 基礎(chǔ)篇。但即使如此,在相關(guān)領(lǐng)域打滾多年的人, 可能還是會被一些問題困擾著。你懂S參數(shù)嗎? 請繼續(xù)往下看...

2、個別S參數(shù)與串聯(lián)S參數(shù)的差別

問題1:為何有時候會遇到每一段的S參數(shù)個別看都還好,但串起來卻很差的情況(loss不是1+1=2的趨勢)?

Quick answer : 如果每一線段彼此連接處的real port Zo是匹配的,那loss會是累加的趨勢,但若每一線段彼此連接處的real port Zo差異很大,那就會看到loss不是累加的趨勢,因?yàn)榇拥慕用嫔蠒卸嘣黾拥姆瓷鋼p失。

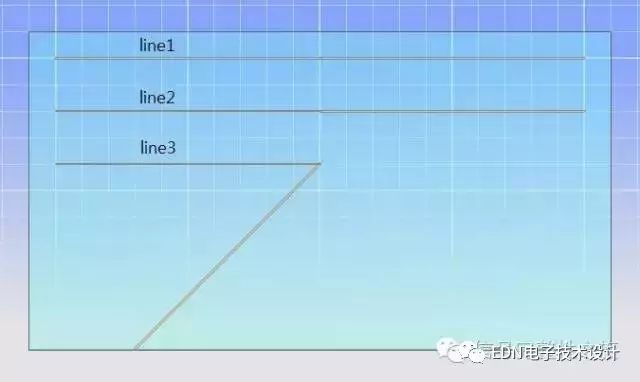

(1)下圖所示的三條傳輸線

Line1是一條100mm長,特性阻抗設(shè)計(jì)在50ohm的微帶線,左邊50mm,右邊50mm。Line2也是一條100mm長的微帶線,左邊50mm維持特性阻抗50ohm,但右邊50mm線寬加倍,特性阻抗變 小到33。Line3也是一條100mm長的微帶線,左邊50mm維持特性阻抗50ohm,但右邊50mm線寬加倍,特性阻抗變 小到33,且呈135o轉(zhuǎn)折。

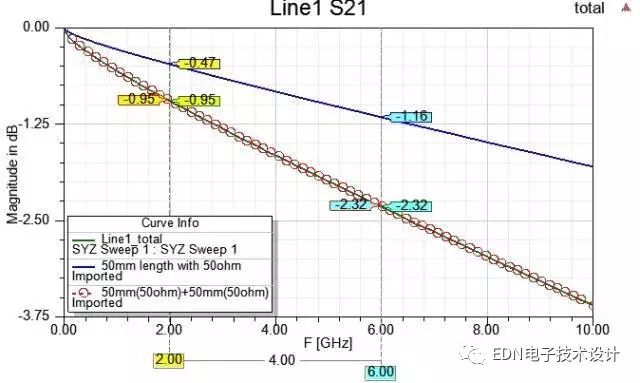

觀察Line1的S21發(fā)現(xiàn),左右兩段的S參數(shù)有累加特性

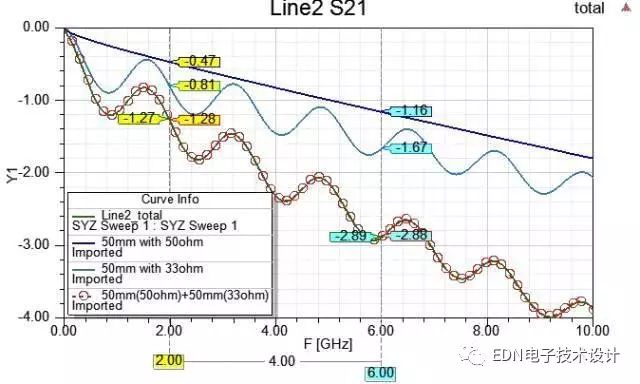

觀察Line2, Line3的S21發(fā)現(xiàn), 整條線的S參數(shù)比起左右兩段個別看的S參數(shù)之累加差一些

問題2:為何各別抽BGA與PCB的S參數(shù)后,在Designer內(nèi)串接看總loss,與直接抽BGA+PCB看S參數(shù)的結(jié)果不同?

Quick answer : 這與結(jié)構(gòu)在3D空間上的交互影響,還有下port位置有時也有影響。

(2)下圖所示是兩層板BGA封裝,放上有完整參考平面的PCB兩層板, 這是在消費(fèi)性電子產(chǎn)品很常見的應(yīng)用條件。

黃色是高速的差動對訊號,其在PCB上走線的部分,有很好的完整參考平面,但在BGA端則完全沒有參考平面。

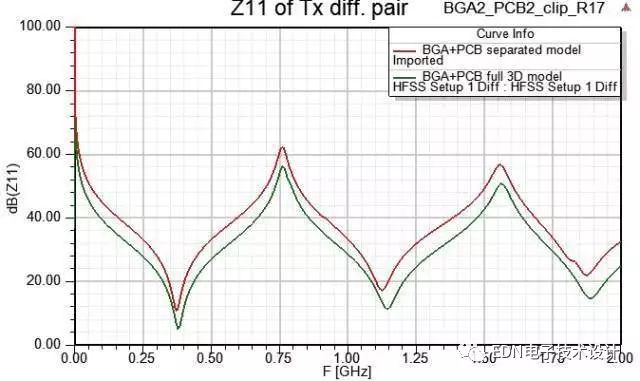

HFSS 3D Layout模擬結(jié)果

3、雙埠S參數(shù)對地回路效應(yīng)的處理

問題1:RLC等效電路可以估出訊號線與地回路每一段的RLC特性,但S參數(shù)卻不行,原因是什么? S參數(shù)帶有地回路的寄生效應(yīng)嗎?

Quick answer : RLC等效電路是terminal base model,而S參數(shù)是port base model,后者看的昰一個port的正負(fù)兩端之間的差值。所以S參數(shù)雖然有含地回路(return path)寄生效應(yīng),但無法單獨(dú)分離出地回路的影響。

問題2:在Designer匯入S參數(shù)模型時,可以選擇該S參數(shù)的電路符號要不要有每一個port的reference ground (negative terminal),或是使用common ground,使用common ground是否表示把每個port的negative terminal短路,會忽略地回路的寄生效應(yīng)嗎?

Quick answer : 使用common ground,并不會把return path兩端short,S參數(shù)本身已經(jīng)內(nèi)含地回路的效應(yīng)。

4、兩個2-port S參數(shù),有可能組成一個4-port S參數(shù)嗎?

Quick answer : No. 一個2-port S參數(shù),內(nèi)涵2x2 (4) matrix單元,即S11, S12, S21, S22,而一個4-port S參數(shù),需內(nèi)涵4x4 (16) matrix單元。所以明顯的,當(dāng)有兩條線的兩個2-port S參數(shù),并不足以充分且唯一定義一個4-port S參數(shù),即這兩條"之間"的近端耦合與遠(yuǎn)程耦合條件并未被定義。換言之,一個4-port S參數(shù)可以簡化(reduce order)分離出兩個2-port S參數(shù),但反之不然。

5、全3D模型的S參數(shù),與分開的3D模型S參數(shù)串連的差別

常見的問題是:封裝與PCB板單獨(dú)抽S參數(shù)后,再于電路仿真軟件串接S參數(shù),這樣的做法跟把封裝與PCB直接在仿真軟件中3D貼合抽S參數(shù)會有怎樣的差異?

Quick answer : 封裝與PCB間在Z軸上的空間耦合路徑,只有把封裝與PCB直接在仿真軟件中3D貼合抽S參數(shù)時,才會被考慮。這樣的做法當(dāng)然是最準(zhǔn)的做法,但需不需要每個案子都一定 非得這么做不可,其實(shí)取決于結(jié)構(gòu)與帶寬考慮。當(dāng)這條路徑的耦合效應(yīng)影響,在您所設(shè)計(jì)的結(jié)構(gòu)下,在一定帶寬以上的影響不能被忽略時,就必須考慮。

6、Port阻抗的設(shè)定

Port阻抗的設(shè)定,對S參數(shù)本質(zhì)上,與S參數(shù)的使用上,有沒有影響?

Quick answer : 雖然renormalize不同的port阻抗,會得到不同的S參數(shù)曲線,但該N-port model所定義的物理效應(yīng)本質(zhì)上是相同的。所以對于model的使用,理論上沒影響,但實(shí)際上 因?yàn)閠ool的transient analysis的數(shù)值處理能力(fitting ability)不同,有些時候有影響。

打個比方,在SIwave v4.0很早期的文件,會建議訊號的port阻抗設(shè)50ohm,而電源的port阻抗設(shè)0.1~1ohm,但目前的SIwave其實(shí)就不需要特別這么做,即你可以延續(xù)之前的設(shè)定習(xí)慣,或是全部都renormalize 50ohm,SIwave吐出的S參數(shù)代到Designer去用,都可以得到一樣的結(jié)果。如果您使用其他的tool有遇到設(shè)不同的port阻抗,得到時域模擬結(jié)果不同的情況,建議您可以試試SIwave。

7、Export S參數(shù)模型時

Export S參數(shù)模型時,有沒有做port renormalize to 50ohm,對使用S參數(shù)有沒有影

Quick answer : No

8、問題與討論

(1) S參數(shù)無法匯入怎么辦?

Ans:首先檢查tool是否反饋任何錯誤訊息,再來以文本編輯器打開該S參數(shù),檢查其頻點(diǎn)描述定義是否是遞增排列(frequency monotonicity)。會出現(xiàn)這種烏龍錯誤,通常是有人手動編輯去修改S參數(shù)造成。

(2) S參數(shù)因?yàn)閜ort數(shù)過多導(dǎo)致模擬耗時怎么辦?

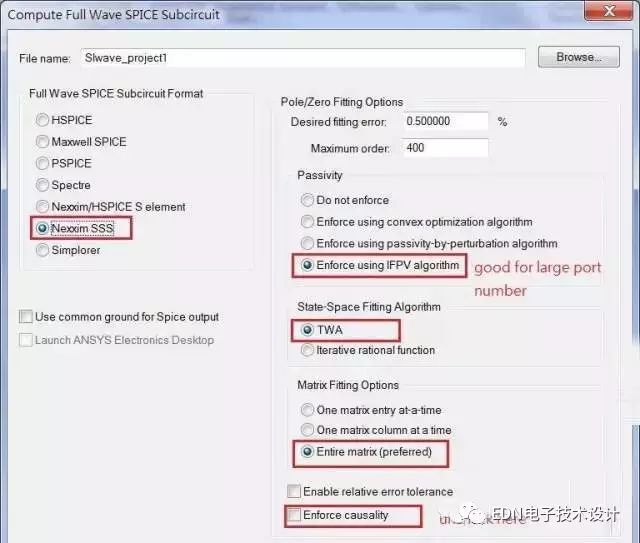

Ans:遇到S參數(shù)模擬耗時,首先我會檢查該S參數(shù)是否有passivity與causality issue,或是在Designer模擬過程中,注意看看是否在state-space fitting process卡很久。遇到多埠S參數(shù),則試著轉(zhuǎn)成state space model (.sss),仿真速度會加快不少,而透過SIwave或NdE轉(zhuǎn)state space model的程序中,建議只勾enforce passivity,不用勾enforce causality,這樣也會節(jié)省不少時間。(因?yàn)閟tate space algorithm本身就滿足primitive causality,所以不用擔(dān)心其因果性問題)

(3) Toushstone1.0(TS1.0)與TS2.0主要有何差別?

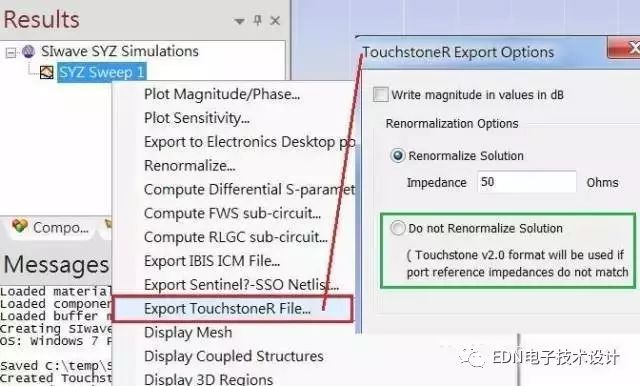

Ans:TS2.0 (.ts)支持mixed reference impedance,而TS1.0 (.snp)每個port的reference impedance都要是相同的50ohm. 以SIwave為例:

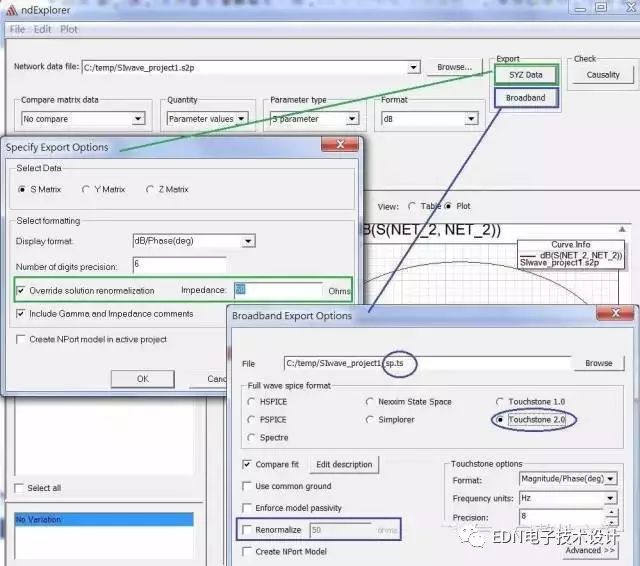

以Designer內(nèi)NdE (Network Data Explorer)為例

不管原本在SIwave或HFSS的port設(shè)定是否有指定renormalize,最后要export時還可以再決定要不要overwrite renormalize

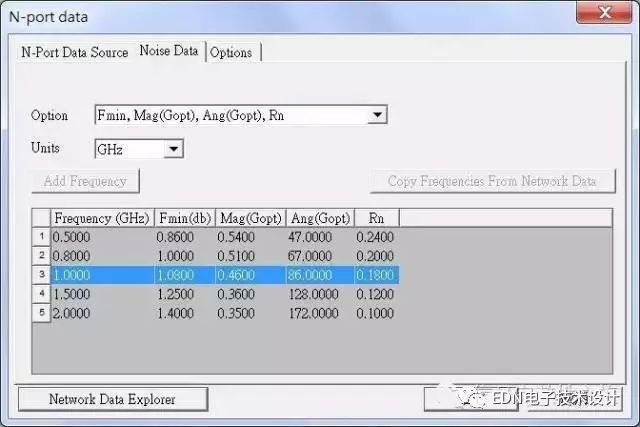

(4)0Touchstone file可以設(shè)定noise data,那是什么東西,何時使用?

Ans:這是在TS1.0就有定義的功能,可以對Touchstone file附加noise data定義,一般用于主動組件的S參數(shù)模型。

當(dāng)你在Designer匯入S參數(shù)模型時,可以右鍵單擊[Edit Model]檢視noise data (如果有的話).

(5)為何在2.2的例子,BGA與PCB各別S參數(shù)的loss累加(-0.29-0.8=-1.09)反而是比整個3D model一起看所得到的S參數(shù)(-1.06)來的差?

Ans:當(dāng)BGA與PCB做3D結(jié)合的條件下去抽S參數(shù)時,此時原本沒有參考平面的BGA上走線,會看到一些PCB上的平面透過solder ball所貢獻(xiàn)的些微回流路徑效應(yīng)。這點(diǎn)我們也可以透過觀察Z11(Z profile)來驗(yàn)證。

-

RF

+關(guān)注

關(guān)注

65文章

3051瀏覽量

166972 -

S參數(shù)

+關(guān)注

關(guān)注

2文章

141瀏覽量

46546

原文標(biāo)題:RF工程師必須掌握的內(nèi)容:從淺入深解說S參數(shù)

文章出處:【微信號:edn-china,微信公眾號:EDN電子技術(shù)設(shè)計(jì)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

工程師必須掌握的PCB專業(yè)術(shù)語

硬件工程師需要掌握的硬件基礎(chǔ)知識

當(dāng)你的工程師朋友失聯(lián)時,別氣,ta真的是在忙工作 #搞笑 #電子愛好者 #硬件工程師 #晶振 #揚(yáng)興科技

硬件工程師VS軟件工程師|硬件工程師看到這都淚目了!#硬件設(shè)計(jì) #硬件工程師 #電子工程師 #軟件工程師

干硬件這一行,各種辛酸只有同行才懂吧 ? #電路設(shè)計(jì) #電子愛好者 #硬件工程師 #電子工程師

嵌入式軟件工程師和硬件工程師的區(qū)別?

“班長!說好畢業(yè)后當(dāng)硬件工程師,你怎么..." #搞笑 #電子行業(yè) #電子工程師 #晶振 #揚(yáng)興科技

RF工程師必須掌握的內(nèi)容:從淺入深解說S參數(shù)

RF工程師必須掌握的內(nèi)容:從淺入深解說S參數(shù)

評論